# A Survey on Thread-Level Speculation Techniques

Alvaro Estebanez, Universidad de Valladolid Diego R. Llanos, Universidad de Valladolid Arturo Gonzalez-Escribano, Universidad de Valladolid

Thread-Level Speculation (TLS) is a promising technique that allows the parallel execution of sequential code without relying on a prior, compile-time dependence analysis. In this work we introduce the technique, present a taxonomy of TLS solutions, and summarize and put into perspective the most relevant advances in this field.

Categories and Subject Descriptors: F.1.2 [Modes of Computation]: Parallelism and Concurrency; D.1.3 [Concurrent programming]: Parallel programming

General Terms: Runtime parallelization

Additional Key Words and Phrases: Speculative multithreading, speculative runtime parallelization, thread-level data speculation, TLDS, optimistic parallelization, thread-level speculation, TLS

#### **ACM Reference Format:**

Alvaro Estebanez, Diego R. Llanos, Arturo Gonzalez-Escribano, 2014. A Survey on Thread-Level Speculation Techniques. ACM Comput. Surv. X, Y, Article ZZ ( 20YY), 40 pages. DOI: http://dx.doi.org/10.1145/0000000.0000000

#### 1. INTRODUCTION

Thread-Level Speculation (TLS), also called Speculative Parallelization (SP), or even Optimistic Parallelization, is a runtime technique that executes in parallel fragments of code that were originally intended to run sequentially. Instead of relying on compiletime analysis to identify independent parts of sequential code that can be run concurrently, TLS techniques optimistically assume that these parts can be executed in parallel by different threads. To ensure correctness, speculative threads should detect whether they have consumed a datum that was subsequently updated by a predeccessor thread, that is, a thread executing an earlier part of the code, according to sequential semantics. Such situations, called *dependence violations*, should be detected and rectified by hardware or software mechanisms, or a combination of both, to keep sequential semantics. If a dependence violation is detected, a corrective action will take place, typically discarding the results calculated by the thread that has consumed the incorrect value, and restarting it to be fed with the updated datum.

In this paper we review the literature related to Thread-Level Speculation techniques, presenting a taxonomy that helps to better understand each proposed solution in its context. The paper is organized as follows. Section 2 presents a global view of the

This research has been partially supported by MICINN (Spain) and ERDF program of the European Union: HomProg-HetSys project (TIN2014-58876-P), CAPAP-H5 network (TIN2014-53522-REDT), and COST Program Action IC1305: Network for Sustainable Ultrascale Computing (NESUS).

Author's addresses: A. Estebanez, D. R. Llanos and A. Gonzalez-Escribano, Departamento de Informática, Universidad de Valladolid, Paseo Belén 15, Valladolid, Spain.

Permission to make digital or hard copies of part or all of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies show this notice on the first page or initial screen of a display along with the full citation. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, to republish, to post on servers, to redistribute to lists, or to use any component of this work in other works requires prior specific permission and/or a fee. Permissions may be requested from Publications Dept., ACM, Inc., 2 Penn Plaza, Suite 701, New York, NY 10121-0701 USA, fax +1 (212) 869-0481, or permissions@acm.org.

© 20YY ACM 0360-0300/20YY/-ARTZZ \$15.00 DOI: http://dx.doi.org/10.1145/0000000.0000000 problem, including a description of sources of speculation in the code, together with the main design choices that may arise while designing a TLS solution. Section 3 examines the first solutions that served as a base for the development of TLS systems. Section 4 details hardware-based approaches, where additional hardware is added to support speculation. Section 5 shows software-based proposals, which do not require additional hardware to monitor the parallel execution, at the cost of a certain performance loss. Section 6 describes other works that take advantage of TLS capabilities for different purposes. Section 7 cites some studies that have pointed out the theoretical and practical limits of the TLS paradigm. Finally, Section 8 concludes our paper.

#### 2. SOURCES OF TLS AND DESIGN CHOICES

In [Torrellas 2011], an accurate summary of Thread-Level Speculation techniques is given, including a detailed description of the two main issues that any TLS system should solve: How to buffer and manage speculative states, and how to detect and handle dependence violations. His analysis makes any effort to reproduce a summary of TLS characteristics here meaningless: we suggest the reader to consult his work to better understand the fundamentals of the field and the management of side effects due to the use of thread-level speculation. In this section, we will briefly discuss where are the main sources of speculation, how TLS techniques can be classified, and which are the most important design choices that have to be faced to set up a TLS system.

#### 2.1. Loops as a source of speculation

Due to how easy it is to distribute work among threads, loops are the most important source for TLS. The synthesis of loop-based speculation written by [Rauchwerger 2011], who was also a pioneer in the field, accurately reflects the importance of loops as a source of speculation. Under TLS, loops are divided into blocks of iterations that are dispatched to be optimistically executed in parallel, while a monitor ensures that the execution follows sequential semantics. If this is not the case, the monitor squashes offending threads, restarting them with the correct values. Otherwise, version data stored in the local speculative buffers are committed to the main copy. We will first briefly describe how data processed in one iteration may interact with calculations in different iterations, a situation known as data dependence.

There are three basic types of data dependences among two fragments of code, namely true, anti, and output dependences. In the following examples, let  $S_i$  and  $S_j$  be two statements, where  $S_i$  should be executed earlier than  $S_j$  according to sequential semantics.

- *True dependence*: Statement  $S_i$  writes into a location that is later read by  $S_j$ . These situations are also called RAW (Read After Write) conflicts, or *flow* dependences.

- —Anti dependence: Statement  $S_i$  reads a location that is later written by  $S_j$ . These situations are also called WAR (Write After Read) conflicts.

- Output dependence: Both statements  $S_i$  and  $S_j$  write into the same location. These situations are also called WAW (Write After Write) conflicts.

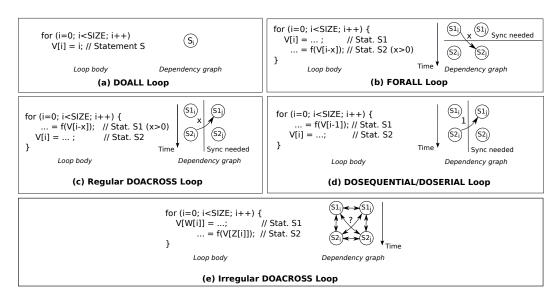

These definitions can be used to create a taxonomy of loops, according to the presence of data dependences among their iterations. One of the first taxonomies was proposed by [Polychronopoulos and Kuck 1987]. This work classified loops into three different types: *doall*, *forall*, and *doacross*.

— Doall loops: Loops that do not present any dependence among their iterations. Therefore, all iterations can be processed in parallel with no further checking [Tang and Yew 1986]. Figure 1(a) shows an example of this loop. Most of current compilers can parallelize this kind of loops automatically.

Fig. 1. Different types of loops according to the presence of data dependences. The label in each edge represents the dependence distance. Data flows are represented by the arrow directions.

- Forall loops: Loop whose iterations may present true (that is, RAW) dependences: Values produced by one iteration may be used in a subsequent iteration. An example is depicted in Fig. 1(b). All iterations of a forall loop can be executed simultaneously if and only if all the statements that produce the value (S1 in the figure) have finished before the execution of any statement that consumes the value (S2 in the figure). If this behavior cannot be guaranteed, a synchronization mechanism is needed.

- Doacross loops: Loops that may have cross-iteration anti (also known as WAR or backward) dependences. [Krothapalli and Sadayappan 1990] divides doacross loops into three categories:

- Regular doacross loops: Loops whose anti dependences among iterations are dominated by a constant value x. Figure 1(c) shows an example. Regular doacross loops with x>1 can be parallelized by ensuring that the execution of the iterations involved in the dependence follows sequential semantics. If the value of x is known at compile time, compilers are usually able to produce a parallel version of the loop.

- Dosequential or doserial loops: A special type of regular doacross whose iterations depend on the previous one (that is, loops that have a dependence distance x=1). Figure 1(d) shows an example where the dependence is from the last statement of the body of the loop to the first statement. These loops have no parallelism at the iteration level.

- *Irregular doacross loops:* Loops whose anti (also kwown as backward) dependences among iterations are not known at compile time. Figure 1(e) shows an example. These loops are commonly called "irregular loops", and in general they cannot be parallelized safely at compile time.

Compile-time techniques can be used to generate parallel versions of *doall*, *forall* and, when the dependence distance is known at compile time, *regular doacross* loops. Since TLS is a runtime technique, it can use the available information in all of the described loops, including *irregular doacross* loops. With respect to *dosequential* loops, a TLS system will also guarantee that the parallel execution will be correct, at the cost of

squashing and re-starting iterations continuously to follow sequential semantics, thus degrading performance. The main application of TLS is in the parallel execution of *irregular doacross* loops when the total number of dependences that appear at runtime is low.

#### 2.2. Drawbacks of TLS

Although TLS can extract parallelism even from *irregular doacross loops*, it will likely be slower than a compile-time parallelization, if the latter can be applied. Sources of overhead in TLS include the cost associated to thread squash and restart due to data dependence violations, speculative buffer overflows, load imbalance due to data locality issues, thread dispatch and commit, and inter-thread communications [Dou and Cintra 2004].

TLS overheads may not only lead to lower performance in terms of execution time, but also to a greater energy consumption. This issue appears in software solutions, due to the energy cost associated to the execution of additional instructions to guarantee that sequential semantics are followed, and to the wasted work carried out by squashed threads. Energy inefficiencies also appear in hardware approaches, due to the need of additional hardware structures in the cache hierarchy for data versioning, dependence checking, and its associated bus traffic [Renau et al. 2005]. We will return to this problem in Sect. 6.3.

## 2.3. A first classification of TLS techniques

According to [Marcuello et al. 1998; Kejariwal et al. 2006], there are three types of speculation techniques: (1) control speculation; (2) data dependence speculation; and (3) data values speculation (also called *value prediction*). These types are not disjoint, and their basis can be combined to achieve better results.

- 2.3.1. Control speculation. Control speculation applies speculation to loops that include conditional sentences. Execution paths of each iteration are detected, mapping them to different threads. [Jacobson et al. 1997b; Wallace et al. 1998; Akkary and Driscoll 1998] combined control speculation with branch prediction. [Puiggali et al. 2012] tried to predict the outcome of conditional branches without the need to know all the variables implied in the condition.

- 2.3.2. Data dependence speculation. Data dependence speculation is a technique suitable for the parallel execution of loops that may lead to inter-thread memory dependences. Load operations from speculative variables (that is, variables whose use may lead to a dependence violation) usually return the most recent value for that variable, while speculative store operations search for the use of incorrect values in those threads, executing subsequent iterations according to sequential semantics. Many researchers have contributed to this solution: Please refer to [Rauchwerger and Padua 1995; Franklin and Sohi 1996; Breach 1998; Marcuello et al. 1998; Cintra and Llanos 2003; Tian et al. 2008].

- 2.3.3. Data values speculation. Data value speculation techniques, also known as value prediction techniques, predict at runtime the result of instructions before their execution. This approach is based on the idea that an accurate prediction may avoid a squash. For example, the work by [Raman et al. 2008] describes a prediction-based TLS software that predicted values of the following iterations without specifying the iteration where a value would be taken from. The main disadvantage of these proposals is that, in general, for loops with irregular memory accesses and complex control flow, this solution does not obtain good predictions. Other works that use predictors are [Sohi et al. 1995; Akkary and Driscoll 1998; Codrescu and Wills 1999a; Steffan

et al. 2002; Cintra and Torrellas 2002; Prabhu and Olukotun 2003; Li et al. 2005; Tian et al. 2010a; Fan et al. 2012; Gao et al. 2013].

#### 2.4. Design choices overview

To be speculatively executed, the original code should be instrumented at compile or runtime to handle different operations, such as loading and storing of speculative data, performing commit operations if the speculative execution succeeds, and discarding incorrect work if it does not. The main design choices that should be faced in a TLS system are described in [Yiapanis et al. 2013]. To implement a TLS system, a number of decisions should be taken<sup>1</sup>:

- 2.4.1. Metadata management. TLS approaches should manage some information in order to detect whether a dependence violation has occurred. Thus, each thread should know both what memory addresses have been used, what operations have been done, and which thread has done each operation. All this information is collectively known as metadata [Yiapanis et al. 2013], and its management has two goals: Preserving the information related to variables at risk of suffering violations, such as which thread has loaded, stored, or is locking a certain variable; and maintaining references about operations done by each thread, specifically, recording the variables loaded or written. The choice of the data structure to handle metadata may severely affect performance, depending on the relative costs of accessing and updating information during the parallel execution. An example of such tradeoff can be found in [Estebanez et al. 2014a].

- 2.4.2. Version Management. When executing several consecutive fragments of sequential code in parallel, each thread usually maintains a version copy of the data structure that is accessed speculatively. This solution allows changes to this data to be performed locally, only storing these changes to a permanent place if the speculative execution of this thread proves successful. To do so, TLS systems require some additional storage to maintain the intermediate copies of each thread. There are two ways of managing these data:

- —Lazy Version Management. In this case, a local copy of the exposed data is individually stored and managed. Therefore, when a load or store operation is performed, only the local version is changed. When a RAW dependence violation is detected, only local versions of threads in conflict have to be discarded, instead of modifying the reference version in memory<sup>2</sup>.

- The other approach, *Eager Version Management*, requires fewer resources, because the reference version in memory is modified. An additional buffer (called *undo log* in the literature) records old values and is used to restore original data in the case of a dependence violation.

Regarding version management, [Garzarán et al. 2003; Garzarán et al. 2005] proposed a taxonomy to classify speculative systems according to the way of buffering the speculative versions of variables. They took into account the isolation of speculative thread states in each processor, and how the new data versions produced by speculative threads is merged with the main memory.

2.4.3. Conflict Detection. Dependence violations can be checked with either a lazy or an eager approach: Lazy Conflict Detection avoids the need to check for conflicts on every access, by delaying this task to a later stage before the commit operation. This solu-

$<sup>^1</sup>$ Unless otherwise noted, the following discussion applies for both loop-level and block-level TLS systems.

<sup>&</sup>lt;sup>2</sup>Note that WAW dependence violations can be avoided by a commit operation that follows sequential semantics. Regarding WAR dependences, the use of local versions of exposed data avoids this problem.

tion implies to store the sequence of accesses to each speculative datum by different threads, in order to ensure that all accesses were performed following sequential semantics. Although this approach avoids time-consuming checks during the speculative execution, the amount of work that might be potentially discarded is much higher. A more strict approach, called *Eager Conflict Detection*, looks for potential dependence violations on every access. This design avoids performance losses produced by later checks, by squashing and restarting threads as soon as a dependence violation is produced. However, the time devoted to checking each potential dependence violation is much higher, slowing down the parallel execution even when no dependence violations arise.

2.4.4. Scheduling of iterations. To speculatively parallelize a loop, it should be partitioned into *chunks* (or *blocks*) of iterations to be assigned to different threads. Early approaches included a compile phase capable of classifying iterations into sets of independent iterations. Although iterations within a set should be executed in order, the sets should be executed sequentially, in order to avoid dependence violations. This *compile-time scheduling* solution came at the cost of performing a costly analysis, that in many cases could not be carried out due to its complexity and/or the presence of potential dependence violations that depended on runtime information. In these cases, the simplest solution is to use *chunks of fixed size* [Kruskal and Weiss 1985]. The particular size chosen is an important design decision. The use of smaller chunks will reduce squashing costs, at the cost of a higher scheduling overhead. On the other hand, bigger chunks will increase the cost of thread squashing and may lead to load imbalance.

To mitigate these problems, variable chunk size strategies originally designed to achieve load balancing in parallel computations, such as [Hummel et al. 1992; Polychronopoulos and Kuck 1987], can also be used in speculative execution. Regarding the particular context of TLS, [Llanos et al. 2007] proposed a *variable chunk size* for the speculative execution of randomized incremental algorithms, an important class of problems where the probability of a dependence violation decreases as execution proceeds. Their work uses smaller chunks for the first iterations, where randomized incremental algorithms present more dependence violations, then gradually increases the chunk size to reduce scheduling overheads, and finally reduces the size of the chunks again to achieve a better load balancing.

The use of chunk sizes that follows a predefined distribution, however, may not be the best solution. Speculative parallelization poses a more complex scheduling challenge than traditional parallelization, because, for irregular applications, both the number and the particular distribution of dependence violations are unknown before the loop is executed. Therefore, the idea of *changing the chunk size at runtime* depending on the number of squashes produced makes sense [Llanos et al. 2008]. Recently, [Estebanez et al. 2015] proposed a method, called Moody Scheduling, that makes use of both the number of re-executions of the last chunks of iterations and their tendency (increasing, decreasing, stable) to figure out an appropriate chunk size for the following chunk to be scheduled.

2.4.5. Squashing alternatives. If a RAW dependence violation is produced, all data calculated by the offending thread (the one that have consumed the incorrect value) should be discarded. The mechanism chosen to do so is a design decision that severely affects performance. Some approaches just discard the threads that have consumed this particular, wrong value, and others discard the offending thread and all its successors. This leads to the following solution space, as described by [Garcia-Yaguez et al. 2014]:

- —Stops parallel execution: First solutions, such as [Rauchwerger and Padua 1995], simply discard the entire speculation execution when a dependence violation was produced, and then restart the loop sequentially from the beginning. Due to their high cost in terms of execution time, these solutions only benefit loops that were indeed parallel.

- *Inclusive squashing*: This approach stops and restarts the first thread that have consumed the wrong value, together with all its successors, regardless of whether they have consumed any value from the offending thread. Due to its simplicity of implementation, this is the most used solution (see [Cintra and Torrellas 2002; Cintra and Llanos 2003; Prabhu and Olukotun 2003; Ceze et al. 2006]), although it may discard potentially useful work carried out by a successor that has not consumed any polluted data.

- Exclusive squashing: This approach squashes (a) the offending thread, (b) all successor threads that have consumed any value generated by him, and (c) all threads that have consumed any value produced by the aforementioned squashed threads. In other words, only successor threads that have not consumed any value that may be derived from the offending thread are allowed to survive. Note that this solution may discard threads that have consumed values from the offending thread that have no relationship with the value that triggered the dependence violation. [Li et al. 2005] tried to implement this ideas in hardware. [Colohan et al. 2006] also used this kind of squashing mechanism in the context of databases (where restarting a thread leads to big performance losses), and used sub-threads to check for squashed threads. [Tian et al. 2010b] also proposed a solution that does not discard all the produced values, only a small part of them. Also, [García-Yágüez et al. 2011; Garcia-Yáguez et al. 2014] developed a software-only version of this idea, with the help of a list that stores which threads have consumed a value for a particular predecessor.

- Perfect squashing: Discards offending threads and those successors that have consumed the incorrect value or any value generated using it. Threads that have consumed correct values from the offending thread are not squashed. This is the approach that leads to fewer squashes. However, to keep track of the definition and use of each particular datum, an in-depth analysis should be performed, This operation seems to be too costly. For example, [Akkary and Driscoll 1998] proposed a specific table to store dependences, while [Rotenberg et al. 1997] used a table that saved all intermediate values. Nevertheless, [Tian et al. 2011] addressed this problem and concluded that this squash mechanism is not profitable.

The above discussion assumes that the data dependences are handled at the data-element granularity level. Note that, if the TLS system uses a granularity coarser than the data-element for speculative data, for example at the cache level, *false conflicts* may appear, leading to unnecessary squashes of speculative threads.

The following section describes the ideas that led to modern TLS techniques.

### 3. PRECURSORS

One of the first approaches centered on the parallelization of loops that may present dependence violations was the one proposed by [Knight 1986]. With the functional languages in mind, specifically the Multi-Lisp approach, [Halstead 1985] introduced a hardware approach that allowed speculation through the use of two different caches, one dedicated to storing those values loaded from memory, and the other used to hold those values produced by the processor whose accuracy was not confirmed yet, thus using lazy version management (see Sect. 2.4.2). [Midkiff and Padua 1987] described a solution to synchronize the concurrent execution of singly-nested loops, while [Zhu and Yew 1987] described an algorithm to handle all types of loops described in Sect. 2.1.

[Aiken and Nicolau 1988] described another scheduling algorithm (see Sect. 2.4.4). which analyzed loops and obtained the optimal, dependence-free distribution, making use of compile-time analysis techniques (See Sect.2.4.4). In those years, [Baxter et al. 1989] performed research to extract some parallelism of Doconsider loops, a kind of regular Doacross loops (see Sect. 2.1). where iterations could be rearranged, in order to preserve dependence semantics, and parallelize as many iterations as possible. They developed a compiler plugin that divided iterations into subsets of iterations that depend on each other, so as to execute several independent subsets at the same time. Although this paper was focused on programs whose dependences are known at compile time, it also mentioned codes not schedulable at start-time [Mirchandaney and Saltz 1988; Saltz and Mirchandaney 1988], which are codes whose dependences could only be extracted during their execution, and therefore a compile-time scheduling mechanism is not applicable. [Krothapalli and Sadayappan 1988] explored a solution to remove anti and output dependences (see Sect. 2.1). For that purpose, they performed a reference analysis, storing multiple copies of suspicious variables used in the loop. Later, [Krothapalli and Sadayappan 1990] proposed a dynamic scheduler based on synchronism (see Sect. 2.4.4), that allowed doacross loops to be addressed with complex inter-iteration dependences. Afterwards, [Wolf and Lam 1991] used matrices to transform and parallelize loops in a general way, with the help of compile-time scheduling mechanisms capable of dealing with nested loops.

The idea of the use of a dynamic *inspector-executor* model appeared at that time. With this approach, an inspector loop checks for dependences in a preliminary phase, and if no dependences arise, a second phase executes the loop in parallel. [Saltz et al. 1991] introduced this method in order to parallelize loops, showing that this technique allowed a significant performance improvement in loops with a big number of operations, where inspector phase time was not significant compared to the executor phase. However, none of these approaches parallelize loops with output dependences. [Chen et al. 1994] developed a software solution that reduced delays between processor communications and allowed the parallelization of loops with output dependences. They reused some results during the execution, allowing the overlap of dependence iterations and the sharing of some information between inspector and executor phases.

#### 4. HARDWARE-BASED APPROACHES

Several hardware implementations have been developed to support TLS, mainly through the addition of auxiliary registers to manage speculation. Even though most hardware approaches have some parts implemented in software, in this section, we will review both pure hardware-based and mixed implementations. There are mainly two ways to implement TLS on hardware (HTLS): Developing a chip from scratch, or customizing an existing chip. The modification of an existing chip led to the development of Simultaneous Multithreading (SMT) processors<sup>3</sup>.

This section is structured in three parts. The first describes the approaches that did not rely upon any previously developed scheme; the second details those based on the SMT architecture; and the third depicts those that proposed CMP enhancements.

#### 4.1. Pioneers

4.1.1. Multiscalar paradigm. [Sohi et al. 1995] developed the Multiscalar processor, one of the first and most important approaches that executed sequential code (called tasks)

<sup>&</sup>lt;sup>3</sup>[Packirisamy et al. 2008; Tang et al. 2005] compared SMT with CMP (Chip Multiprocessors) in the context of TLS, giving a perspective of performance, power and thermal; [Ungerer et al. 2003] described chips that support multithreading. However, a full description of these processors is beyond the scope of this survey, and will not be provided.

in parallel through speculation. The underlying idea was to perform some tasks in parallel with the use of a chip that included several processors, ensuring sequential semantics. Parallelization was organized by using graphs of tasks. In this way, each processor received a task and executed it. Consistency was ensured with the help of additional control logic, that synchronized the production of register values in predecessor tasks with the consumption in successor tasks. A hardware monitor also ensures correctness in speculative memory accesses. The execution of parallel tasks in each processor followed a fixed order, needed to ensure sequential semantics. To handle this, a ring of processors was proposed. If a processor used a wrong value from a predecessor, its task was squashed and restarted (see Sect. 2.4.5). When each processor finished its execution, values were committed in the order imposed by the ring. As will be seen in Sect. 5.1.2, this idea was later used by several software-based TLS solutions to implement sliding-window mechanisms. The authors also suggested the use of a value predictor (see Sect. 2.3.3) to reduce squash overheads, and to improve load balance among processors in order to avoid wasting computational cycles, through the choice of an appropriate granularity. [Sohi et al. 1995] affirmed that correctness of the operations could be ensured by different hardware implementations. A full description of one that supports the Multiscalar architecture can be found in [Breach et al. 1994; Breach 1998; Franklin 1993; Vijaykumar 1998]. [Vijaykumar 1998; Vijaykumar and Sohi 1998] also described efficient ways of choosing a good task division by using compile-time scheduling techniques (see Sect. 2.4.4).

Improvements in the storage of speculative values. Several solutions tried to reduce overheads with the use of lazy version management (see Sect. 2.4.2) [Franklin and Sohi 1996; Gopal et al. 1998] describe several methods to support different data versions produced during speculative execution, through the use of hardware with the Multiscalar architecture. [Franklin and Sohi 1996] proposed ARB, an Address Resolution Buffer used by all processors. This solution introduced some overheads due to the traffic caused by the simultaneous accesses to the ARB. [Gopal et al. 1998] proposed a Speculative Versioning Cache (SVC), intended to overcome the limitations of ARB by assigning a different cache to each processor. [Jacobson et al. 1997a] studied different branch prediction techniques for control speculation (see Sect. 2.3.1): An automata-based predictor, a prediction based on the history, and an address predictor for jumps and indirect calls.

4.1.2. The Trace processor. [Rotenberg et al. 1997] developed an architecture based on the parallel execution of traces. Unlike the tasks used in the Multiscalar paradigm, that were obtained by the compiler dividing the sequential program, a trace is a dynamic sequence of instructions that are built as the program executes, and stored in a so-called trace cache [Rotenberg et al. 1996]. This proposal consisted of a processor composed of different processing elements, each having the organization of a small-scale superscalar processor, with enough space to hold an entire trace and enough functional units and register files. Instructions were executed in parallel, while intertrace dependences were speculated with the use of value predictors.

Improvements to Trace. [Patel et al. 1998] devised a way to reduce the size of traces and a modification of branches with the aim of making them more predictable. [Black et al. 1999] modified the original Trace approach, managing traces as series of pointers to basic blocks stored in cache. [Rotenberg and Smith 1999] addressed the problem of control independence to better exploit the parallelism of this architecture, using control speculation (see Sect. 2.3.1) to structure codes into control-independent code blocks. [Jacobson and Smith 2000] improved the instruction dispatching of trace caches through the construction of sets of traces before they were needed. Several years later,

[Padmanabha et al. 2013] proposed the use of super-traces to detect those parts of codes that had regular patterns to maximize energy efficiency.

- 4.1.3. Oplinger et al. architecture. [Oplinger et al. 1997] combined ideas from the Multiscalar paradigm, putting more emphasis on the hardware and the compiler. The result was a chip that contained some subsystem caches that supported speculation. They also developed a specific software adapted to the underlying hardware. This work also contained a study of several benchmarks under different metrics, namely the number of sequential code lines, doall loops, doacross loops, etc. The goal of this research was to check the parallel behavior of the benchmarks used. This study was improved by [Oplinger et al. 1999], with the aim of locating niches for speculation. The authors concluded that TLS should not only be applied in a single loop. Instead, they affirmed that using TLS in all loops and procedures of sequential applications would produce better results.

- 4.1.4. I-ACOMA. [Krishnan and Torrellas 1998] implemented a clustered SMT architecture where the chip had several independent processing units, with each unit having the capability to perform simultaneous multithreading. The system supported the speculative execution of binaries, without source recompilation, by the use of software that identified potential threads in programs. Their efforts were mainly centered on loops. The basis of this idea was to use a binary annotator that added some notes into the executable file. Order between threads was implemented through a bit mask and communications between threads were performed by either memory or registers, throughout an annotation phase in the case of registers, and in runtime otherwise. Dependence violations were identified with the help of a table called *Memory Disambiguation Table (MDT)* (an idea based on ARB, see [Franklin and Sohi 1996]). The MDT was stored in the L2 cache, and contained copies of the different data used.

- 4.1.5. STAMPede. [Steffan and Mowry 1998; Steffan et al. 2000] proposed a chip multiprocessor architecture with TLS support called STAMPede, whose goals were twofold. First, to handle arbitrary memory access patterns<sup>4</sup>; and second, to provide a scalable paradigm that could be adapted to both SMT and CMP architectures. They suggested a system that implements speculation with the help of a cache memory consistency protocol.

Value prediction. The same authors improved the communication cost of the STAM-Pede architecture in [Steffan et al. 2002]. To do so, they implemented value prediction (see Sect. 2.3.3), with no additional cost of recovering if prediction failed (speculation mechanisms were used in that case). Their solution tried to predict those values that were going to be loaded but not stored in the same epoch. The authors affirmed that these values were likely to produce dependence violations. They also proposed what they called "silent store", which avoided the unnecessary stores of values to variables with the same value, replacing these stores, which led to many dependence violations, with loads that compared values to check correctness.

Compiler optimization. [Steffan et al. 2005] extended the cache protocol described by [Steffan et al. 2000], developing a cooperative approach between the software and hardware parts of the system. Their goal was to optimize the compiler and reduce the complexity of the hardware used. Moreover, they adapted the hardware support to improve the compatibility with the majority of processors, and to be scalable to any machine size.

$<sup>^4</sup>$ The reason was that the authors affirmed that previous works could only use array references (contrary to the opinion of [Krishnan and Torrellas 1999]).

Cache locality. [Fung and Steffan 2006] used an extended version of STAMPede to study the inherent problems related to cache locality when TLS executions were performed. The authors started their study on the initial transition from sequential to parallel execution. Cache misses at that point (called startup misses) were not significant enough to adversely affect performance. Instead, they found that read-only cache misses were the most important part of misses in the execution of programs. Write-based sharing parameters and strided miss patterns were also addressed in this paper. The other misses were not intended to be mitigated because, according to their study, they represent less than 10% of the execution times of the benchmarks considered.

4.1.6. SPT approach. [Li et al. 2005] described an architecture specially designed to support scalar applications. This work also contains the design of a compiler specially developed for this architecture<sup>5</sup>. The architecture developed combined hardware and software parts. The proposed hardware was composed of two cores: One to execute the main program thread, and the other to execute speculative threads. [Li et al. 2003] described a software value predictor (see Sect. 2.3.3) in connection with this implementation.

## 4.2. Simultaneous multithreading (SMT)

[Tullsen et al. 1996; Tullsen et al. 1998] proposed to combine features available in both superscalar and multithreaded architectures. The original SMT paradigm was designed to improve the use of superscalar hardware with small additional cost, by overlapping multiple threads on a single, wide-issue processor in order to allow independent threads to use different functional units in the same cycle. SMT added thread tags to a single-thread architecture, and maintained a hardware context for every simultaneous thread, including a general register file, PC register, and other state registers. [Tullsen et al. 1998] can be viewed as the starting point of the main research in TLS with SMT.

- 4.2.1. Speculative multithreaded processor. [Marcuello et al. 1998] proposed a speculative multithreaded processor that extended the instruction window in order to use speculation through hardware. These authors developed an architecture that controlled parallelism without the need for a strict thread control. This scheme was entirely hardware-based, so it did not need any modifications to existing binaries. This solution automatically detected loops (details of this detection can be found in [Tubella and Gonzalez 1998]), and launched their parallel execution by several threads distributed along a ring. Communications among threads were supported using broadcast messages. This solution also used data prediction techniques (see Sect. 2.3.3). With the use of lazy version management (see Sect. 2.4.2), misspeculations were detected by the comparison of local values and versions of cache lines at commit time.

- 4.2.2. Threaded Multi-Path Execution (TME). [Wallace et al. 1998] enhanced the SMT processor with control speculation capabilities (see Sect. 2.3.1), through the use of a branch predictor. The procedure followed was the execution of all possible branches of a loop, whilst there were enough resources. Otherwise, the most likely branch to occur was predicted. Before speculatively executing a predicted branch, threads saved their execution context just in case dependence violations were produced, and they had to re-execute the branch with correct values.

- 4.2.3. Dynamic Multithreading Processor (DMP). [Akkary and Driscoll 1998] developed DMT, an architecture that fetched, renamed and dispatched instructions from different locations of the same program into a modified hierarchy of small instruction windows.

<sup>&</sup>lt;sup>5</sup>A more detailed description of this compiler can be found at [Du et al. 2004].

Each thread (created by hardware when a loop or a branch were located) managed and executed its own window of instructions. All its partial results, which were stored in additional buffers and handled with lazy version management, were accessible by the other threads in order to detect misspeculations. This approach also used a branch predictor (see Sect. 2.3.1) to mitigate data dependences between threads.

4.2.4. Implicitly-Multithreaded Processors (IMT). [Park et al. 2003] developed IMT, based on the Multiscalar approach by [Sohi et al. 1995], but mapping threads on SMT. This approach took some ideas from TME and DMT. IMT mainly differed from TME in the way the former managed control dependences among threads. Whereas TME speculated with multiple threads in case of branch mispredictions (as previously exposed), IMT created threads taking into account the predictions made by threads in execution, trying to follow the program order. Regarding DMT, IMT led to better results than DMT thanks to prediction enhancements, and also to the elimination of the selective recovering from misspeculations that required several searches.

4.2.5. Packirisamy et al. solution. [Packirisamy et al. 2006] extended the SMT architecture to support TLS with the use of a modified L1 data cache. The new cache scheme consisted of the addition of a pointer to the thread which stored a value in the cache, and some speculative bits to save the loads and stores performed to variables. The number of these bits was similar to the number of available threads, in order to avoid overheads in the check for dependence violations. According to [Wang et al. 2006], this solution was more useful than DMT [Akkary and Driscoll 1998] and IMT [Park et al. 2003] when dealing with big threads. In addition, this approach used a simpler hardware than the one proposed by [Marcuello et al. 1998].

## 4.3. Chip Multiprocessor (CMP)

CMPs have also been widely used in conjunction with TLS solutions. [Olukotun et al. 1996] was one of the first works that described these processors. A CMP can be viewed as a group of single-thread processors integrated onto the same processor chip, in order to act as a team. Generally, processors in a CMP have their own L1 cache, and share the second-level cache. [Olukotun et al. 2007] described some implementations of CMP such as Piranha [Barroso et al. 2000] and Niagara [Kongetira et al. 2005]. Here, we will review those studies that used CMP in connection to TLS.

4.3.1. SMT on CMPs. [Krishnan and Torrellas 1999] explained in more detail the ideas described by [Krishnan and Torrellas 1998], and extended the approach to CMPs, the chips used in all the following improvements. [Cintra et al. 2000] designed and evaluated a different CMP architecture, based on the use of the mentioned MDT, for scalable speculative parallelization. Their solution required a relatively simple hardware and was efficiently integrated with the cache coherence protocol of a conventional NUMA (Non-Uniform Memory Access) multiprocessor. This integration of speculative chip multiprocessors into scalable systems seemed to offer great potential. [Cintra and Torrellas 2002] later presented a hardware subsystem that aimed to learn, predict and solve dependence violations that could arise. They addressed the reduction of squashes using an improved version of the MDT that contained information about data managed by the threads in order to perform predictions, and making use of inclusive squashing (see Sect. 2.4.5). [Martínez and Torrellas 2002] also proposed using synchronism in speculative threads to speculate in active barriers or busy logs. To do so, they developed a hardware solution that added a bit per line and some logic to the cache, also giving support for register checkpointing. If a misspeculation was detected, the offending thread was restarted from a synchronization point.

4.3.2. Hydra CMP. The Hydra chip multiprocessor was developed by [Hammond et al. 1998; Hammond et al. 2000]. Hydra integrated four MIPS-based processors and their primary caches on a single chip, together with a shared secondary cache. Its design was influenced by two previous CMP designs that supported TLS: the Multiscalar paradigm [Sohi et al. 1995] and STAMPede [Steffan and Mowry 1998] approaches, both described previously. According to Hydra's authors, it was an intermediate step between them: Hydra allowed bigger threads with less complex processors than Multiscalar, where the use of a ring of processors and hardware-based thread sequencing used imposed these limitations. With respect to STAMPede, Hydra proposed more complex write-back primary caches that did not need to be drained as each thread completed, avoiding burst of bus activity. Hydra was also influenced by the architecture developed by [Oplinger et al. 1997]. Hydra required the user to mark loops which would be speculatively executed, and incorporated a specific compiler and a runtime system with some instructions to manage speculation, including those needed to both start and end speculative loops, fork calls, and manage dependence violations. [Olukotun et al. 1999] claimed that applying speculation only in loops, instead of speculating on both loops and procedures, led to performance improvements in connection to Hydra. This research also proposed some code transformations, and a hardware implementation of checkpoints to recover from misspeculations, with the help of backup copies of registers.

Profiling and code transformations. [Chen and Olukotun 2003a] added an additional hardware component to Hydra, called TEST, that carried out the analysis of sequential codes to extract potential speculative loops. This profiling was later used in a dynamic parallelization system that transformed Java programs for speculative execution. [Chen and Olukotun 2003b] used this tool to develop JRPM, a system that could dynamically and automatically parallelize many Java applications. JRPM served as an integration of all the previous approaches developed. This solution, implemented with the Java Virtual Machine as the abstraction layer, allowed the programmer to avoid the need for manual changes in the code to be parallelized almost entirely.

Tutorials and performance analysis. [Prabhu and Olukotun 2003] developed a tutorial to explain the main adjustments needed to change a code in order to improve the performance earned with TLS, using Hydra TLS hardware implementation as their test platform. Optimizations described went from code reorganization to using value prediction (see Sect. 2.3.3), but also to performing adjustments to the algorithm or to applying speculative pipelining. In a later work, [Prabhu and Olukotun 2005] performed an in-depth study of some applications of the SPEC CPU2000 benchmark suite with respect to speculative parallelization. The study includes a description of the applications used, and tips on their parallelization using some of the techniques described above.

4.3.3. Atlas Chip-Multiprocessor. [Codrescu and Wills 1999a; Codrescu et al. 2001] aimed to extract parallelism using single-chip multiprocessors by developing a new chip based on the combination of TLS and inter-thread data value prediction (see Sect. 2.3.3). Their solution assigned fragments of sequential code to processors until all of them were busy. This assignment was carried out by a control module that also performed value prediction. This development followed the principles exposed by [Rotenberg et al. 1997] and [Marcuello et al. 1998], being one of the first approaches whose main design factor was based on value prediction. The main contribution of this approach was the use of a better predictor than those used in previous TLS researches, called AMA. It was based on three tables of recent values, as described in [Codrescu

and Wills 1999b]. The processor also contained a branch predictor for control speculation (see Sect. 2.3.1), together with a *recovery queue*.

- 4.3.4. Out-of-order speculative execution. [Renau et al. 2005] enhanced CMP with hardware updates, developing the first approach that allowed out-of-order spawn in the context of TLS, that is, the execution of some instructions in an unpredictable order, far from the sequential order imposed by previous works. This research also included a compiler that could parallelize codes to be executed in either in-order or out-of-order modes. DMT [Akkary and Driscoll 1998] processors could also execute out-of-order fragments of code (tasks), using an SMT processor with different structures and mechanisms. [Akkary et al. 2008] later defined Disjoint Out-of-order execution (DOE) processors, a model that targeted inter-task data communications latencies. It was composed by several DOE cores, organized in a ring, that shared an L1 data cache and a task dispatcher. A DOE core consisted of two threads, one to execute independent instructions, and the other responsible of executing the dependent instructions. In this way, when a thread that depended on a previous thread execution needed to wait for a datum, its core executed its independent instructions while previous datum was produced.

- 4.3.5. Bulk. [Ceze et al. 2006] addressed the problem of the complexity of the basic operations involved in TLS processes. To do this, they used a metadata management system (see Sect. 2.4.1 consisting on a kind of hash encoder (called signature) that managed the addresses accessed by each speculative thread. Each signature was a set of addresses and allowed several addresses to be treated as if they were a single one. They enhanced the architecture with some hardware mechanisms that could efficiently operate with this hashed information. The model developed supported TLS and also transactional memory. In the TLS approach, they proposed to assign all the updated values of this thread to the nearest successors when it began its execution, and to get these data earlier. In addition, they developed some operations, such as intersection, union, etc., to manage and operate with signatures. The details of the compiler used to develop this system was described in [Liu et al. 2006].

- 4.3.6. POSH. [Liu et al. 2006] developed the POSH compiler, which divided subroutines and loops into tasks. Instead of relying entirely on compile-time scheduling mechanisms (see Sect. 2.4.4), they used a profiling tool to select those tasks that could be benefited from parallelism and data prefetching techniques. It was implemented in a CMP with some additional TLS registers, and supported a software value predictor similar to the solution developed by [Li et al. 2003].

- 4.3.7. RASP. The Runtime Automatic Speculative Parallelization (RASP) was the approach presented by [Hertzberg and Olukotun 2011]. This hardware-based model could speculate over binary codes directly. A translator analyzed programs running in x86 systems, and translated them into RISC microcode. The translator was based on the DBT86 system developed by [Hertzberg and Olukotun 2009], with some enhancements to speculatively parallelize loops and acquire feedback. The new system could locate loops and add some instructions to allow commitments and rollbacks with checkpoints, thus performing lazy conflict detection (see Sect. 2.4.3). The main contribution of this research was the inclusion of an automatic tool to speculatively parallelize binary codes over the existing hardware.

## 4.4. Related techniques

4.4.1. Transactional Memory. Transactional memory (TM) [Herlihy and Moss 1993] is another form of optimistic execution [Barreto et al. 2012]. The main difference between TM and TLS is that TM was designed for a number of different goals, such as encapsu-

lating synchronization burdens (such as deadlock avoidance) of fine-grained lock-based programming, and to reducing contention by the use of optimistic speculation-based techniques. On the contrary, TLS was primarly designed to parallelize sequential applications. Therefore, TM portions of code intended to run in parallel portions do not need to follow any sequential order, while TLS threads need to preserve sequential order. Transactions have been combined with TLS in two ways: Using transactions to guarantee sequential semantics of loops, and speculating over large transactions to be executed in parallel. Regarding the first approach, [Guo et al. 2008] proposed LogSPoTM, a hardware-based solution that enhanced LogTM, a transactional memory system, to ensure sequential semantics and give support to TLS. LogSPoTM was mainly based on the integration of timestamps and arbitration policies to impose a thread order and preserve semantics. [Deng et al. 2012] used this solution and, with the help of a hardware value predictor, improved their previous experimental results. [Dai et al. 2011] also used LogSPoTM in their work. They looked to reduce squashes with the use of a chip that supports packet-switch, Network-on-Chip, thus applying some of the ideas of network theories to speculation. This work considered that thread data were packets, and assigned higher priority to those belonging to predecessor threads. This solution helped to reduce both timeouts and the number of squashes.

[Porter et al. 2009] also used TLS to improve the performance of their hardware-based transactional model architecture. There are other works that combine TM techiques with software-based TLS: We will review them in Sect. 5.3.3.

4.4.2. Speculative and transactional lock elision. Locks are a useful technique to guarantee sequential semantics of parallel programs. [Rajwar and Goodman 2001] extended this concept with the so-called Speculative Lock Elision, allowing the speculative execution of critical sections. To do so, this solution automatically replaced locks by optimistic hardware transactions, checking that no errors were produced. If transactions failed, the system used the original lock. Some studies were conducted to evaluate transactional lock elision supports in different architectures, including [Dice et al. 2009; Cain et al. 2013; Afek et al. 2014]. Some commodity processors offer this support, including Intel's Haswell [Hammarlund and et al. 2014] and IBM's Power 8 [Cain and et al. 2013].

4.4.3. Database context. [Colohan et al. 2005] demonstrated that database transactions could benefit from the use of TLS when a large transaction (with more than 7500 instructions) should be executed. Moreover, they gave some guidelines to remove some of the frequent dependences of the software in this context. The hardware used to do so was based on STAMPede (see Sect. 4.1.5). Later, [Colohan et al. 2006] introduced subthreads to manage dependences that occur in those large threads. Their sub-threads introduced checkpoints and stored intermediate values to enable the recovery of some of the calculations done in the speculative execution until a dependence violation was produced, with the use of a lazy conflict detection system (see Sect. 2.4.3) that only discarded the wrong part of the execution.

## 5. SOFTWARE-BASED APPROACHES

Software-based TLS systems implement techniques to guarantee the coherence of the optimistic parallel execution on conventional processors, without the need for dedicated functional units. Research in this field has been centered on reducing, whenever possible, the overheads in execution times due to the need to ensure consistency by software.

As we will see, first proposals usually executed the loop in parallel, and if a dependence violation was produced, the work already carried out was discarded, and the loop was re-executed sequentially. Subsequent approaches performed partial commits,

in order to take advantage of the work carried out before a dependence violation appears, and thus tried to minimize the number of squashed threads to those that had actually consumed a polluted value and its sucessors (a technique known as *inclusive squashing* (see Sect. 2.4.5).

Again, we will follow a historical perspective to describe the research in this field. We will first center our attention on those solutions where programmers should explicitly invoke runtime library functions and/or compiler support to manage speculative execution. Then, we will move to solutions that are based on higher-level programming abstractions. We will finish this discussion with some proposals related to TLS behavior, and a brief review of some works that mixed TLS with other techniques.

# 5.1. Solutions relying on compile-time and runtime support

First approaches required programmers to use different methods to explicitly invoke TLS mechanisms. The most representative ones are described below.

5.1.1. LRPD test. We can place the origins of Software TLS (STLS) in the work carried out by [Rauchwerger and Padua 1995; 1999], with their research in the parallelism of doall loops. They proposed the use of a test called LRPD to support the speculative parallelization of loops with some backtracking capabilities. This proposal re-executed the loop serially if the runtime test failed, a squashing solution that is simple to implement but with a huge cost in case of misspeculation (see Sect. 2.4.5). The proposal worked as follows: The target loop was firstly transformed through privatization (that is, making private copies of shared variables) and reduction parallelization (determining at compile-time that certain operations are indeed reductions, and replacing them with a parallel algorithm), and then it was speculatively executed as a doall loop. During this parallel execution, the test stored the iteration number where shared variables were defined and/or used. After the parallel loop execution, a fully-parallel data dependence test was applied over this information to ensure that the loop had no cross-iteration dependence. If the test failed, the loop was sequentially re-executed. Otherwise, the parallel execution of the loop was considered successful. This approach had the disadvantage of detecting cross-iteration dependences only after the end of the parallel execution, thus implying a heavy performance penalty. [Gupta and Nim 1998] presented a more efficient method for speculative array privatization that did not require the computation to be rolled back when a particular variable was found to produce a dependence violation. To do so, they presented a technique that allowed the early detection of loop-carried dependences, and another that detected parallelization hazards immediately after they were produced. In addition, they proposed a set of new runtime tests for speculative parallelization of loops that defied parallelization methods based solely on static analysis. [Dang et al. 2002] developed a technique to extract the maximum available parallelism for loops that were known to present some dependences. This solution presented an evolution of the LRPD test, called Recursive LRPD (R-LRPD). The basic idea was to transform a partially-parallel loop into a sequence of fully-parallel loops. At each stage, this proposal speculatively executed all remaining iterations in parallel and the R-LRPD test was applied to detect the potential dependences.

5.1.2. Software versions of hardware solutions. [Rundberg and Stenström 2000] applied many of the ideas of hardware-based speculative architectures in software. First, name dependences were solved by dynamically renaming data at run time. Second, the overhead of restoring the original situation after a misspeculation was greatly reduced by reducing the amount of data to commit, and by supporting parallel implementations of the commit phase. Third, some anti data dependence violations were avoided by supporting lazy version management without the need to enforce synchronizations

between a pair of conflicting threads. Fourth, true data dependence violations were detected when they happened, which reduces the cost of misspeculations. To do so, each instruction on speculative data was augmented with a checking code that detects data dependence violations dynamically, that is, using eager conflict detection (Sect. 2.4.3). Finally, it committed data following sequential semantics.

[Cintra and Llanos 2003; 2005] developed a different scheme based on an aggressive sliding window. It checks for data dependence violations on every speculative store, while avoiding synchronization whenever possible. The sliding window used consisted of an array of slots which store the status of each running thread, and pointers to their own version of the speculative data, Commits were carried out in order from the non-speculative thread. Each time a commit operation was finished, the sliding window advanced one position, allowing a new, most-speculative thread to start. This solution used lazy version management, eager conflict detection and inclusive squashing. More recently, [Estebanez et al. 2014b] improved this solution with a different implementation that supported the speculative access to dynamically-allocated data structures and support for the use of pointer arithmetic. This solution used a sophisticated metadata management (see Sect. 2.4.1) with the help of hash tables to reduce the time needed to find the most up-to-date version of a datum (see Sect. 2.3.2), a problem also described in [Tian et al. 2010b].

- 5.1.3. Based on master/slave paradigm. [Zilles and Sohi 2002] introduced the Master/Slave speculative parallelism, a new kind of speculation whose basics were the use of a master thread and some slaves that performed the task assigned by their master. The main idea of this technique was to divide at compile time the program into tasks that would be carried out by the slaves, while the master thread predicted the values that would be produced by each task and continued with the execution of the code without waiting for their results. This approximation needed to check all the values produced by slaves after the execution of a task with respect to the values predicted by the master. If both were equal, the master's prediction had been successful, on the other hand, a misspeculation had been detected. In this case, the work incorrectly carried out by the master and all slaves since the last checkpoint needed to be discarded and re-executed.

- 5.1.4. Automatic thread extraction. [Ottoni et al. 2005] proposed an automatic approach for thread extraction. The system, called DSWP, exploited the fine-grained pipeline parallelism of many applications to extract long-running, concurrently executing threads. Their results showed significant improvements when executing these applications on a dual-core CMP.

- 5.1.5. Complementing compile-time techniques for auto-parallelization. [Tournavitis et al. 2009] proposed the use of profile-driven parallelism detection to augment the number of loops that may considered safe to parallelize, relying on the user for final approval. This work also uses machine-learning techniques to take better mapping decisions for different target architectures.

- 5.1.6. Other solutions: SpLIP, MiniTLS, and Later. [Oancea et al. 2009] developed SpLIP, a speculative tool centered on decreasing overheads of speculative operations of previous approaches, implementing non-locking operations where was possible, making use of hash functions for metadata management (see Sect. 2.4.1) and relying on versions of data instead of rollbacks (see Sect. 2.4.2). [Yiapanis et al. 2013] introduced a new structure that reduced memory overheads of classical approaches based on the idea of mapping every user-accessed address into an array of integers using a hash function. The authors implemented this compact data structure in two approaches, namely MiniTLS and Later. The main characteristic of MiniTLS was that threads updated

memory locations in-place, and also that all operations followed fast and optimistic design patterns. As in SpLIP, hash functions were used for metadata management. However, this approach used rollback mechanisms instead of version management, because speculative threads modified values directly, possibly producing errors that needed to be handled. This solution is similar to SpLIP, so both were compared in this work. *Later* followed a different design, implementing a lazy version management of values, together with pessimistic design patterns in its operations. The structure used was a bit different, but it was based on the same operations and patterns. This approach also introduced a combination of inspector-executor techniques (described in Sect. 3) and the LRPD test (described in Sect. 5.1.1), implementing the new solution upon them.

- 5.1.7. TLS compiler and runtime for distributed systems. [Kim et al. 2012] present an automatic speculative parallelization system for clusters, composed of a parallelizing compiler and a speculative runtime that minimizes the overheads due to validations, through the use of lazy version management and conflict detection. Other STLS runtime solutions for distributed environments are covered in Sect. 5.4.

- 5.1.8. TLS for web applications. [Martinsen et al. 2013] used a speculative mechanism in the context of web browsing. To do so, they implemented their software by means of the Squirrelfish JavaScript environment, that enabled the parallel execution of Javascript functions. They modified Squirrelfish interpreter to enable each instance of the interpreter to be executed as a thread, while executing as many instances as functions. The used variables were maintained in a special vector that showed modified values to detect dependence violations. The use of TLS in this context allowed these authors to achieve noticeable speedups.

- 5.1.9. Apollo. [Jimborean et al. 2012a; Jimborean 2012; Jimborean et al. 2013] introduced a TLS framework specially designed to speculatively execute nested loops, by using features of the polyhedral model [Ancourt and Irigoin 1991] to dynamically transform code into a more optimized version that led to higher speedups. First, a compiler [Jimborean et al. 2012b] generated skeletons<sup>6</sup> that were the basis of executions, due to their ability to produce different code versions that could be selected at runtime. Then, a dynamic part was responsible for (a) representing memory accesses as predicting linear functions of the loop indices, with the help of interpolating functions, (b) performing dynamic dependence analysis and transformation selection, (c) instantiating the parallel skeleton code, and (d) guiding the execution. The execution was based on profiling the code several times during the execution in order to choose the polyhedral transformations that could better speed up the execution. The detection of dependence violations (see Sect. 2.3.2) was done at three levels: Basic scalars, memory accesses, and loop bounds. This framework led the authors to parallelize some benchmarks that had not been parallelized before due to dependence management hurdles.

- 5.1.10. HVD-TLS. [Fan et al. 2012] developed a software-based speculative framework that improved classical TLS mechanisms by the development of new techniques to improve value prediction (see Sect. 2.3.3), value checking, dynamic task partition, and scheduling (see Sect. 2.4.4). Predictions performed were done using several predictors based on the original value of the variables in conflict. Such predictions used a predictor table that also maintained the number of correct predictions. Values were checked by the main thread to prevent committing unmodified values, a situation re-

<sup>&</sup>lt;sup>6</sup>Skeletons [Darlington et al. 1993] are a set of high-order parallel forms intended to be used as basic building blocks for parallel implementations. They include program transformations to ease portability between different systems.

peated many times according to the authors. Also, this system allowed different levels of granularity to be assigned at runtime, following a linear scheme or a heuristic scheme, where the system monitored the execution and changed the granularity accordingly.

#### 5.2. Solutions relying on additional programming abstraction layers

Our second set of software-based solutions eased the use of TLS by offering new, higher-level abstraction layers.

5.2.1. Fast Track. [Kelsey et al. 2009] developed a system called Fast Track, where a programmer can install potentially-unsafe optimized code while leaving the task of error checking and recovery to the underlying implementation. Specifically, their programming interface allowed users to suggest faster implementations based on partial knowledge of a program and its usage. Fast Track divided code into two branches, the fast track and the normal track, and programmers could change between both tracks when needed. Their implementation included both compile-time and runtime support. A compiler inserts function calls to ensure that the fast track produced the same result as the sequential execution. To protect runtime data, the system relied on the compiler to insert checking code that protects stack data. Regarding global and heap data, the system relied on the operating system to protect them, by turning off write permissions for them in both tracks, and installing custom page-fault handlers. These handlers first recorded which page had been modified in an access map and then reenabled write permissions. The runtime support checked program correctness through the comparison of results at the end of the tracks. If both results were similar, results were supposed to be correct. Otherwise, the fast track results were discarded. In this system, one processor was reserved to run the fast track, and the rest to the execution of normal tracks.

5.2.2. The Copy-or-Discard model. [Tian et al. 2008; 2009] proposed the Copy-or-Discard (CorD) execution model, in which the execution of parallel threads was separately managed by a non-speculative one. Speculative threads read values of the non-speculative thread and performed their computation. After that, speculative threads were committed in order. Then, results were checked by a non-speculative thread so as to preserve the semantics of the sequential order, using a lazy conflict detection (see Sect. 2.4.3). The commit operation was performed by the non-speculative thread through the CorD mechanism, which checked whether results were correct. In this case, results were copied to the non-speculative data. Otherwise, they were discarded at no additional cost, thanks to the use of version copies.

CorD and dynamic memory. The CorD approach did not give support to those applications whose speculative variables were dynamically allocated, so [Tian et al. 2010b] enhanced CorD to be used with programs that had such dynamic data structures. The main problem of this approach was data traversing, because a dynamic structure could change their size during the execution. Pointers imposed another problem, since a speculative copy of a dynamic structure might have a pointer with an address to a non-speculative copy. In order to solve these problems, they proposed using a mapping table that translated addresses among speculative and non-speculative threads. They also included optimizations in the treatment of linked structures. Finally, [Tian et al. 2010a] used a value predictor to improve the parallelization of programs with frequent and predictable cross-iteration dependences (see Sect. 2.3.2).

Reducing misspeculations. [Tian et al. 2011] later tried to further reduce misspeculations. They proposed an approach intended to reuse almost all the correct calculations performed by a thread whose iterations had suffered dependence violations,

instead of discarding all this information, as most approaches did. To do so, they used a partial speculative space in addition to the primary speculative space of each thread. This new space maintained the first read values of a speculative variable. If a misspeculation was found, only the successor spaces of the offending space were squashed (see Sect. 2.4.5). This approach led to better performance and to a reduction in the number of dependence violations, due to lower recovery times.

5.2.3. TLS based on the use of compile-time directives. [Bhowmik and Franklin 2002] described a compiler framework for TLS that allowed the parallelization of all instructions of a code, instead of only those that compose a loop. This feature specially benefited non-numerical applications with complex instructions. Codes were initially analyzed by the compiler and profiled to produce a control flow graph. It was then used to produce partitions that could be executed by multiple threads. [Chen et al. 2003] also developed a compiler that focused on providing a quantitative analysis of codes with complex dependences. Their aim was to give probabilities about the possible flows of the code, and detect if a squash was likely to be produced.

Mitosis. Mitosis is a compiler framework developed by [Quiñones et al. 2005] capable of deciding which fragments of code could be speculatively executed. To do so, the Mitosis compiler marked the beginning of a region whose outcome could be speculatively guessed with a so-called spawning point (SP), and its end with the control quasi-independent point (CQIP) mark. When the sequential execution reached the SP, a speculative thread was launched. This thread predicted the possible values of the outcome of the parallel region and used them to start the speculative execution of the code from the CQIP. Meanwhile, the non-speculative thread continued its execution. If no errors were produced, speculative threads were committed, otherwise, they were discarded. The choice of these spawning points was a key part of the work. To do so, marks were chosen with the use of a synthetic trace. It selected the most suitable parts of codes to be speculatively executed regarding some requirements, such as the amount of workload of routines with respect to the total, or possible misspeculations.

Spice C. SpiceC was an approach proposed by [Feng et al. 2011]. SpiceC implemented a number of directives that, when added to sequential code, eased parallel programming. Programmers did not need to be particularly careful about communications or dependences, because this model supported doall, doacross, pipelining and speculative parallelism. This solution also supported dynamic structures and pointer addresses. SpiceC threads had their own private space for data. A shared global space was used to store shared data. Threads' first accesses were referred to shared space and loaded to each local space, where following accesses were redirected to. When threads ended their executions, they checked for misspeculations, and committed their data to the shared space if they were correct. Directives were similar to OpenMP's [Dagum and Menon 1998], so sequential programs only needed a few additional directives: A directive to suggest what kind of parallelism would be used, and another to mark where commit operations had to take place.

[Feng et al. 2012a] extended SpiceC with some additional directives to support I/O operations within parallel loops. To the best of our knowledge, this was the first approach that addressed the parallelization of this kind of codes through TLS. The main idea behind this research was to break the cross-iteration dependences caused by I/O operations (see Sect. 2.3.2) modifying the original code. To parallelize input operations, this approach calculated file pointers before entering the loop to be used in each iteration. File pointer copies were created on demand by the iterations that used them. Regarding output operations, they required the use of some additional buffers, in order to store intermediate outputs produced by each thread. Each output value was

stored in the corresponding thread buffer and flushed at the end of each iteration following sequential semantics. [Feng et al. 2012b] also augmented SpiceC directives to parallelize loops with dynamically-linked data structures. This work tried to manage different data partitions of loops using the same code, addressing the problem of codes where multiple threads managed several data partitions.

ATLaS. [Aldea et al. 2014; 2015] developed a GCC plugin so as to add loop-based TLS support to OpenMP. Their proposal include the development of a new OpenMP speculative clause to be used in for loops [Aldea et al. 2012], which allowed programmers to declare all variables whose reads or writes may lead to dependence violations. The use of this clause guaranteed that all definitions and uses of speculative variables would follow sequential semantics. The ATLaS framework consisted on a GCC plug-in that gave support to the new speculative clause, and a runtime library that managed the speculative execution. The ATLaS runtime library is able to transparently support speculation over variables of any size, and permits the use of pointer arithmetic. Its implementation offered version management, eager conflict detection, fixed, dynamic, and adaptive chunk scheduling, and both inclusive and exclusive squashing. The internals of the runtime library that managed dependence violations were described in [Estebanez et al. 2014b]. The entire ATLaS framework can be freely downloaded from atlas.infor.uva.es.