$\oplus$

$\oplus$

# Universidad deValladolid

Escuela Técnica Superior de Ingeniería Informática

Departamento de Informática

Tesis Doctoral:

# Easing Parallel Programming on Heterogeneous Systems

Presentada por Ana Moretón Fernández para optar al grado de doctor por la Universidad de Valladolid

Dirigida por: Dr. Arturo González Escribano

Valladolid, 2018

$\oplus$

$\oplus$

#### Resumen

El modo más frecuente de resolver aplicaciones de HPC (High performance Computing) en tiempos de ejecución razonables y de una forma escalable es mediante el uso de sistemas de cómputo paralelo. La tendencia actual en los sistemas de HPC es la inclusión en la misma máquina de ejecución de varios dispositivos de cómputo, de diferente tipo y arquitectura. Sin embargo, su uso impone al programador retos específicos. Un programador debe ser experto en las herramientas y abstracciones existentes para memoria distribuida, los modelos de programación para sistemas de memoria compartida, y los modelos de programación específicos para para cada tipo de co-procesador, con el fin de crear programas híbridos que puedan explotar eficientemente todas las capacidades de la máquina. Actualmente, todos estos problemas deben ser resueltos por el programador, haciendo así la programación de una máquina heterogénea un auténtico reto.

Esta Tesis trata varios de los problemas principales relacionados con la programación en paralelo de los sistemas altamente heterogéneos y distribuidos. En ella se realizan propuestas que resuelven problemas que van desde la creación de códigos portables entre diferentes tipos de dispositivos, aceleradores, y arquitecturas, consiguiendo a su vez máxima eficiencia, hasta los problemas que aparecen en los sistemas de memoria distribuida relacionados con las comunicaciones y la partición de estructuras de datos.

#### **Palabras clave**

Computación paralela, Entornos paralelos, Sistemas heterogeneos, Nuevos modelos de programación, Memoria distribuida, Cálculo de comunicaciones

$\oplus$

$\oplus$

#### Abstract

The use of parallel computing systems frequently represents the only scalable way to solve HPC (High performance Computing) problems in reasonable execution times. The current trend in high performance computing platforms is to include in the same machine several parallel devices, of different type and architectures, and to interconnect them to form highly parallel and heterogeneous distributed systems. Programming efficient and portable parallel applications that can really exploit these systems, imposes specific and complex challenges to the programmers. A programmer must be proficient in distributed-memory communication tools or layers, shared-memory programming models, and specific programming models for the available co-processors, in order to create hybrid programs that will exploit all the machine capabilities. Moreover, she also has to deal with the proper workload distribution among the different nodes and devices, assigning to each one an amount of workload related to their computation power and features. Nowadays, all these issues should be solved by the programmer, making the programming of heterogeneous platforms an actual challenge.

This PhD. Thesis addresses several main problems related to the parallel programming for highly heterogeneous and distributed systems. It first tackles problems to allow the developing of efficient coordination codes, portable across different kind of devices, accelerators, and architectures. Then, it also targets problems related to the data communication and partition issues concerning the use of devices in distributed-memory systems. In this dissertation we introduce abstractions, mechanisms, and methods to solve many of these problems. We also discuss their practical application to develop research prototypes and actual programming tools. Experimental works conducted using these tools validates the applicability of the proposed techniques and the portability, efficiency, and versatility of the programs that can be obtained.

#### **Keywords**

Parallel programming, Parallel frameworks, Heterogeneous systems, New programming models, Distributed-memory, Communication calculation.

This research has been partially supported by Universidad de Valladolid (UVa), MICINN (Spain), the ERDF program of the European Union and Junta de Castilla y Leon: HomProg-HetSys project (TIN2014-58876-P), PCAS (TIN 2017-88614-R), CAPAP-H5 network (TIN2014-53522-REDT), CAPAP-H6 (TIN2016-81840-REDT), COST Program Action IC1305: Network for Sustainable Ultrascale Computing (NESUS), FEDER Grant VA082P17 (PROPHET Project), and by the computing facilities of Extremadura Research Centre for Advanced Technologies (CETA-CIEMAT), funded by the European Regional Development Fund (ERDF). CETA-CIEMAT belongs to CIEMAT and the Government of Spain.  $\oplus$

$\oplus$

$\oplus$

$\oplus$

$\oplus$

$\oplus$

$\oplus$

# Agradecimientos

Tras casi 7 años con ellos (y por aguantarme tanto tiempo yo creo que se lo merecen), empiezo mis agradecimientos a mis tutores Diego y Arturo. En especial dar las gracias a Arturo, por las innumerables horas gastadas juntos escribiendo papers con fórmulas matemáticas inentendibles, por la paciencia que tuvo hasta que aprendí a escribir dos frases seguidas, y por no desistir ni dejar de confiar a pesar de los dos millones de papers rechazados (más o menos echando las cuentas a ojo). Muchas gracias a ambos por darme la oportunidad de realizar el doctorado con vosotros y compartir laboratorio y puesto de trabajo con un motón de gente maravillosa. Gente a la que le debo la Tesis. No se si hubiese sido capaz de acabarla sin los coffe-breaks y la compañía de: Sergio, Alvaro, Héctor, Javi, Yuri, Dani, Edu y un montón más de personas haciendo proyectos fin de carrera, que aunque no pueda nombrar a todas les sigo teniendo muy en cuenta. Tampoco me quiero olvidar de mis compañeros de carrera, con los que empecé este camino, y con los que se me metió esta idea de doctorado en la cabeza. Agradecer también a Ana Lucia Varbanescu la opción de realizar mi estancia de tres meses en Delft, y agradecerla a ella y al resto de compañeros de allí también el trato recibido durante la estancia.

Y cómo no agradecer a mis amigos, empezando por la gente con la que he crecido, con la que mantengo decenas de años de amistad y que en todo momento me han apoyado; y terminando por los Muy Mejores Amig@s y la peña Despiporre que, a pesar de la diversidad de ideas y vidas que hay en el grupo, han sido y son una fuente inagotable de risas, fiestas, alegrías, positivismo y el mejor ejemplo que conozco a seguir como grupo. Como solemos decir: *Poco nos vemos, para lo mucho que nos queremos*.

Por último agradecer a mi familia. Empezaré por orden inverso de antigüedad =). A Adri por estar siempre ahí apoyándome en lo bueno y en lo malo, animarme en este camino siempre que lo he necesitado, y disfrutar conmigo los buenos momentos. A mi hermano, por ser siempre la cabeza pensante, objetiva y razonable de la familia. Seguiría dudando de cualquier tontería de hace 5 años si no fuese por él. A mi madre. Sería banal decir que ella me ha ayudado en este camino, porque en realidad ella me ha ayudado en todos (una Santa como dicen mis amigos). No sería la persona que soy sin ella. Y por último a mi padre, la persona que más orgullosa ha estado de mi, que más me ha apoyado durante los estudios y la que, por qué no decirlo también, la que más presumía de hija. Siempre guardaré tus consejos, y haré todo lo posible para que sigas orgulloso de mi allá donde estés.

Ana Moreton-Fernandez

VI |

$\oplus$

$\oplus$

$\oplus$

$\oplus$

$\oplus$

$\oplus$

$\oplus$

# Contents

$\oplus$

$\oplus$

$\oplus$

$\oplus$

$\oplus$

$\oplus$

$\oplus$

$\oplus$

| Re |              |          | Tesis Doctoral                                                  | 1  |  |  |

|----|--------------|----------|-----------------------------------------------------------------|----|--|--|

|    | R.1          |          | ación                                                           | 2  |  |  |

|    |              | R.1.1    | Computación paralela                                            | 2  |  |  |

|    |              | R.1.2    | Sistemas para la computación paralela                           | 3  |  |  |

|    |              | R.1.3    | Modelos de programación paralelos                               | 4  |  |  |

|    | R.2          |          | vos de la Tesis Doctoral                                        | 7  |  |  |

|    |              | R.2.1    | Metodología de investigación                                    | 7  |  |  |

|    |              | R.2.2    | Objetivos                                                       | 8  |  |  |

|    | R.3          |          | nen de contribuciones                                           | 14 |  |  |

|    |              | R.3.1    | Respuesta a la pregunta de investigación y conclusiones         | 14 |  |  |

|    |              | R.3.2    | Simplificando la programación sobre sistemas heterogéneos basa- |    |  |  |

|    |              |          | dos en aceleradores                                             | 14 |  |  |

|    |              | R.3.3    | Automatizando el manejo de datos en sistemas heterogéneos con   |    |  |  |

|    |              |          | memoria distribuida                                             | 15 |  |  |

|    | R.4          | Conclu   | usiones                                                         | 18 |  |  |

| 1  | Introduction |          |                                                                 |    |  |  |

|    | 1.1          | Motiva   | ation                                                           | 20 |  |  |

|    |              | 1.1.1    | Parallel computing                                              | 20 |  |  |

|    |              | 1.1.2    | Machines for parallel computing                                 | 20 |  |  |

|    |              | 1.1.3    | Parallel programming models                                     | 22 |  |  |

|    | 1.2          | Object   | tives of this Thesis                                            | 24 |  |  |

|    |              | 1.2.1    | Research methodology                                            | 24 |  |  |

|    |              | 1.2.2    | Milestones                                                      | 25 |  |  |

|    | 1.3          | Docum    | nent structure                                                  | 30 |  |  |

|    |              |          |                                                                 |    |  |  |

| I  |              |          | ng the programming on accelerator-based heterogen               |    |  |  |

| ec | ous sy       | ystems   | 3                                                               | 33 |  |  |

| 2  | State        | e of the | art on heterogeneous programming                                | 35 |  |  |

|    | 2.1          | Motiv    | ation                                                           | 36 |  |  |

- vii -

## VIII | CONTENTS

$\oplus$

$\oplus$

$\oplus$

$\oplus$

|   | 2.2 | Proposals for standardizing parallel programming                        |

|---|-----|-------------------------------------------------------------------------|

|   | 2.3 | Proposals targeting directly heterogeneous systems                      |

|   | 2.4 | Summary                                                                 |

|   |     |                                                                         |

| 3 | Con | trollers: An abstraction to ease the use of hardware accelerators 39    |

|   | 3.1 | Motivation                                                              |

|   | 3.2 | Controller Model                                                        |

|   |     | 3.2.1 Kernel management                                                 |

|   |     | 3.2.2 Data management                                                   |

|   | 3.3 | The Controllers library 45                                              |

|   |     | 3.3.1 Data structures and Hitmap                                        |

|   |     | 3.3.2 Controllers and variables management                              |

|   |     | 3.3.3 Declaration and configuration of kernels                          |

|   |     | 3.3.4 Kernel characterization                                           |

|   |     | 3.3.5 Kernel launching                                                  |

|   |     | 3.3.6 Programming example                                               |

|   | 3.4 | Experimental study                                                      |

|   |     | 3.4.1 Case studies                                                      |

|   |     | 3.4.2 Development effort and code complexity                            |

|   |     | 3.4.3 Performance study                                                 |

|   | 3.5 | Summary                                                                 |

|   |     | ,,                                                                      |

| 4 | Sup | porting the Xeon Phi coprocessor in the Controller Programming Model 65 |

|   | 4.1 | Approach to support MIC accelerators                                    |

|   | 4.2 | Integrating MIC coprocessors in the Controller library                  |

|   |     | 4.2.1 Attaching and detaching data structures on the MIC 68             |

|   |     | 4.2.2 New kernel definitions                                            |

|   |     | 4.2.3 Queue management and Kernel launching                             |

|   | 4.3 | Experimental study                                                      |

|   |     | 4.3.1 Study cases                                                       |

|   |     | 4.3.2 Performance study                                                 |

|   |     | 4.3.3 Development effort measures                                       |

|   | 4.4 | Summary                                                                 |

|   |     |                                                                         |

| 5 | Mul | ti-Device Controllers 77                                                |

|   | 5.1 | Introduction                                                            |

|   | 5.2 | Multiple-Device Controller (MCtrl) library                              |

|   |     | 5.2.1 Multi-Controller construction                                     |

|   |     | 5.2.2 Data structures and domains                                       |

|   |     | 5.2.3 Kernel launching                                                  |

|   |     | 5.2.4 Programming methodology and example                               |

|   | 53  | Experimental study 86                                                   |

$\oplus$

$\oplus$

$\oplus$

### CONTENTS | IX

$\oplus$

$\oplus$

$\oplus$

$\oplus$

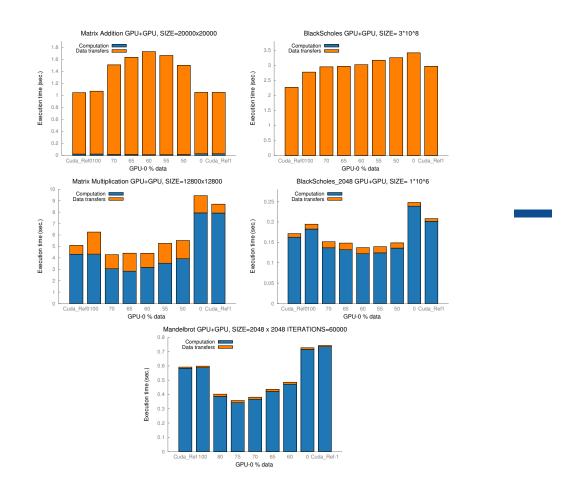

|     | 5.3.1 | Study cases         | 86 |

|-----|-------|---------------------|----|

|     | 5.3.2 | Development effort  | 87 |

|     | 5.3.3 | Performance results | 88 |

| 5.4 | Summa | ry                  | 92 |

$\oplus$

$\oplus$

$\oplus$

$\oplus$

## II Automatizing the data management for distributed-memory spaces in heterogeneous systems 95

| 6 | Stat | e of the | art on automatic management of distributed-memory spaces      | <b>9</b> 7 |

|---|------|----------|---------------------------------------------------------------|------------|

|   | 6.1  | Motiva   | ation and related Work                                        | 98         |

|   |      | 6.1.1    | Parallel libraries                                            | 100        |

|   | 6.2  | Summ     | ary                                                           | 101        |

| 7 | Ana  | lyzing t | he current limitations of communication code generators       | 103        |

|   | 7.1  | The FC   | DP communication scheme                                       | 104        |

|   | 7.2  | Cost n   | nodel                                                         | 105        |

|   |      | 7.2.1    | General cost for a distributed loop                           | 106        |

|   |      | 7.2.2    | Problem size and number of iterations                         | 108        |

|   |      | 7.2.3    | Distribution policy                                           | 108        |

|   |      | 7.2.4    | Packing stage                                                 | 108        |

|   |      | 7.2.5    | Coordination and communication stage                          | 109        |

|   |      | 7.2.6    | Unpacking stage                                               | 109        |

|   |      | 7.2.7    | Total cost                                                    | 110        |

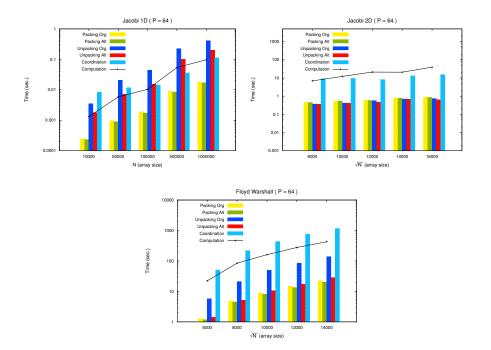

|   | 7.3  | Propos   | sal: Implementation alternative                               | 110        |

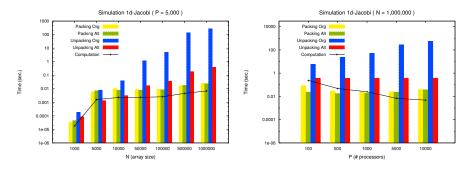

|   | 7.4  | Case st  | tudy: 1-D Jacobi                                              | 112        |

|   |      | 7.4.1    | Cost model parametrization                                    | 112        |

|   |      | 7.4.2    | Simulation study                                              | 113        |

|   | 7.5  | Experi   | mental Study                                                  | 115        |

|   |      | 7.5.1    | Experimental environment                                      | 115        |

|   |      | 7.5.2    | Results                                                       | 115        |

|   | 7.6  | Summ     | ary                                                           | . 117      |

| 8 | Auto | omatica  | lly calculating communications for DMS from data-access expre | es-        |

|   | sion | S        |                                                               | 119        |

|   | 8.1  | Introd   | uction                                                        | 120        |

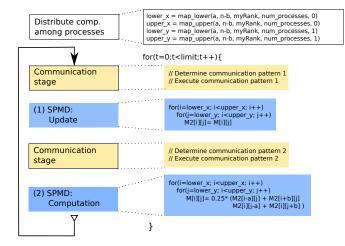

|   | 8.2  | Illustra | ative example and Overview                                    | 121        |

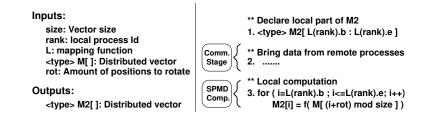

|   |      | 8.2.1    | Programming with an SPMD model                                | 122        |

|   |      | 8.2.2    | Overview of the communication determination technique         |            |

|   | 8.3  | The Tr   | asgo Model                                                    | 125        |

|   |      | 8.3.1    | Overview of the code transformation framework                 |            |

|   |      | 8.3.2    | Notations and definitions                                     | 127        |

## X | CONTENTS

$\oplus$

$\oplus$

$\oplus$

$\oplus$

|    |      | 8.3.3    | Extensions to the Hitmap library                                    | 128   |

|----|------|----------|---------------------------------------------------------------------|-------|

|    | 8.4  | Implen   | nentation of the technique to determine communication patterns      | 129   |

|    |      | 8.4.1    | Functions to calculate working set indexes                          | 129   |

|    |      | 8.4.2    | Determining communications patterns                                 | 132   |

|    |      | 8.4.3    | Communication patterns for specific applications                    | 134   |

|    | 8.5  | Experi   | mental study                                                        | 136   |

|    |      | 8.5.1    | Study cases                                                         | 137   |

|    |      | 8.5.2    | Experimental platforms and setup                                    | 139   |

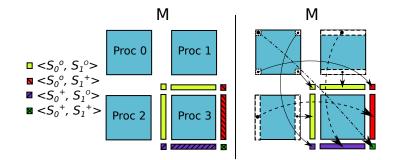

|    |      | 8.5.3    | Improvement achieved by tuning the tile size for each process       | 140   |

|    |      | 8.5.4    | General communications model vs. patterns for specific applications | s 141 |

|    |      | 8.5.5    | Comparison with MPI references                                      | 143   |

|    |      | 8.5.6    | Comparison with a state-of-the-art tool                             | 144   |

|    | 8.6  | Summa    | ary                                                                 | 148   |

|    |      |          |                                                                     |       |

| 9  |      | -        | communications for applications on periodic domains                 | 149   |

|    | 9.1  |          | uction                                                              | 150   |

|    | 9.2  |          | l work targeting problems with periodic domains                     | 150   |

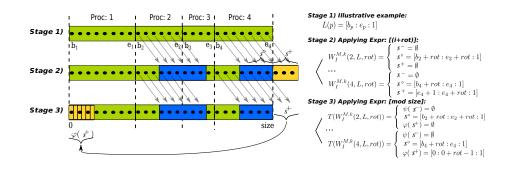

|    | 9.3  |          | tive example                                                        | 151   |

|    | 9.4  |          | ated-communication model                                            | 153   |

|    |      | 9.4.1    | Definitions                                                         | 154   |

|    |      | 9.4.2    | Model for calculating communication patterns in 1-D applications    | 155   |

|    |      | 9.4.3    | Multi-dimensional model                                             | 158   |

|    | 9.5  | -        | nentation on a parallel programming framework                       | 159   |

|    | 9.6  |          | sion: Analyzing the technique                                       | 161   |

|    | 9.7  |          | mental study                                                        | 162   |

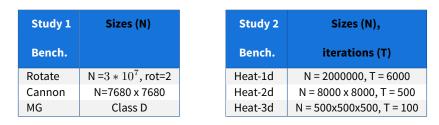

|    |      | 9.7.1    | Design and setup of the experimental study                          | 162   |

|    |      | 9.7.2    | Study 1: Performance comparison with MPI reference codes            | 163   |

|    |      | 9.7.3    | Study 2: Ease of programming                                        | 164   |

|    |      | 9.7.4    | Study 3: Relative cost of calculating communications                | 164   |

|    | 9.8  | Summa    | ary                                                                 | 166   |

| 10 | One  | rators f | or data redistribution                                              | 167   |

| 10 | -    |          | uction                                                              | 168   |

|    |      |          | ting example                                                        | 168   |

|    |      |          | al: Redistribution operators                                        | 171   |

|    | 10.0 | -        | ArrayRemapRange: Remap of an array range                            | 171   |

|    |      | 10.3.2   |                                                                     | 172   |

|    |      | 10.3.2   | ArrayDivide: Dividing an array in several balanced parts using a    | 172   |

|    |      | 10.0.0   | multivalued mask                                                    | 172   |

|    |      | 10.3.4   |                                                                     | 173   |

|    | 10.4 |          | nentation of the operators                                          | 174   |

|    |      |          |                                                                     |       |

$\oplus$

$\oplus$

$\oplus$

## CONTENTS | XI

$\oplus$

$\oplus$

$\oplus$

$\oplus$

|    |      | 10.4.1                              | Supporting data redistributions at Hitmap runtime level         | 174               |

|----|------|-------------------------------------|-----------------------------------------------------------------|-------------------|

|    |      | 10.4.2                              | Implementation of the new operators                             | 175               |

|    | 10.5 | Experi                              | mental studies                                                  | 178               |

|    |      | 10.5.1                              | Experimental platform and setup                                 | 178               |

|    |      | 10.5.2                              | Applying the operators: case studies                            | 178               |

|    |      | 10.5.3                              | Impact of redistributing workload on performance                | 181               |

|    |      | 10.5.4                              | Using the STL library for analyzing the four operators          | 182               |

|    |      | 10.5.5                              | Evaluating the use of the proposal on a real-world application: |                   |

|    |      |                                     | Raytracing algorithm                                            | 185               |

|    | 10.6 | Summa                               | ury                                                             | 186               |

|    |      |                                     |                                                                 |                   |

| 11 | Cond | clusions                            |                                                                 | 187               |

| 11 |      |                                     | s                                                               | <b>187</b><br>188 |

| 11 |      |                                     | rry of contributions                                            |                   |

| 11 |      | Summa                               | rry of contributions                                            |                   |

| 11 |      | Summa                               | rry of contributions                                            | 188               |

| 11 |      | Summa<br>11.1.1                     | iry of contributions                                            | 188               |

| 11 | 11.1 | Summa<br>11.1.1<br>11.1.2           | rry of contributions                                            | 188<br>188        |

| 11 | 11.1 | Summa<br>11.1.1<br>11.1.2<br>Answer | The programming on accelerator-based heterogeneous systems      | 188<br>188<br>189 |

$\oplus$

$\oplus$

$\oplus$

$\oplus$

$\oplus$

$\oplus$

XII | CONTENTS

# List of Figures

$\oplus$

$\oplus$

$\oplus$

$\oplus$

$\oplus$

$\oplus$

$\oplus$

$\oplus$

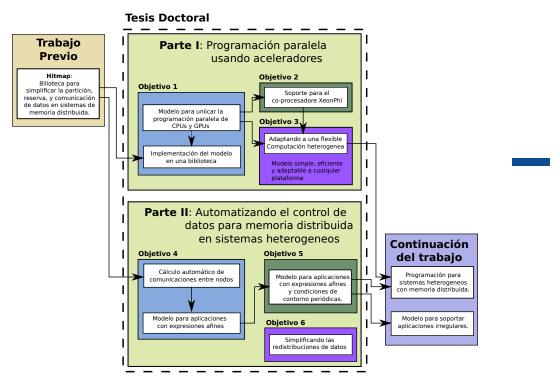

| 1   | Objetivos y estructura de la Tesis Doctoral.                                                                                                   | 9  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.1 | Objectives and structure of this Thesis                                                                                                        | 26 |

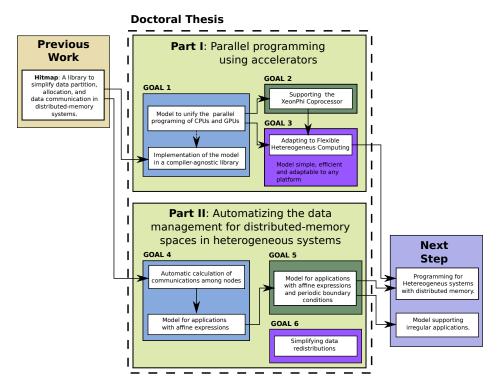

| 3.1 | Diagram of the Controller model architecture                                                                                                   | 42 |

| 3.2 | Examples of the kernel characterization and definition for a stencil program.                                                                  | 48 |

| 3.3 | Example of the main code, for a stencil program.                                                                                               | 49 |

| 3.4 | Excerpt of the Controller library code generated for kernel deployment/launch-<br>ing on a CUDA capable GPU device.                            | 52 |

| 3.5 | Excerpts of the Controller library code generated for kernel deployment/launch-                                                                | 32 |

| 3.5 | ing on a group of CPU-cores.                                                                                                                   | 53 |

| 3.6 | Characterization of the generic or GPU specialized kernels for the case studies (left). Example of kernel wrapper to execute a specialized GPU | 55 |

|     | library function (right).                                                                                                                      | 55 |

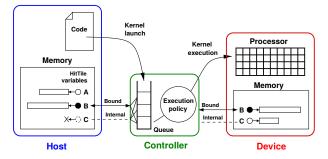

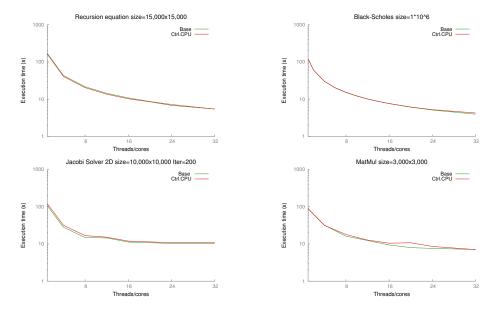

| 3.7 | Execution times (seconds) in Heracles machine of the baseline (Base) and                                                                       | 55 |

| 5.7 | the Controller versions for CPU device (Ctrl.CPU) with a variable number                                                                       |    |

|     | of cores.                                                                                                                                      | 62 |

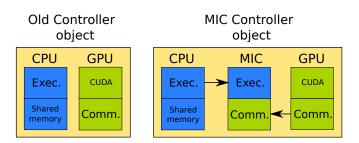

| 4.1 | Old and New Controller model.                                                                                                                  | 66 |

| 4.2 | Kernel definition and configuration, and host program of a matrix addition                                                                     |    |

|     | using the Controller library.                                                                                                                  | 67 |

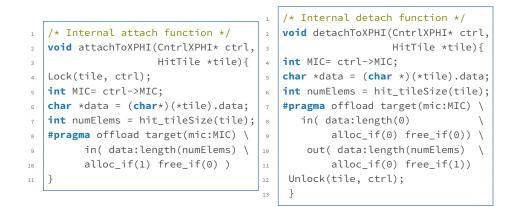

| 4.3 | Excerpts of the internal codes that perform data transfers of a HitTile object.                                                                | 68 |

| 4.4 | Functions internally generated by the MIC kernel definition.                                                                                   | 70 |

| 4.5 | Auxiliary macros defined for a one parameter kernel                                                                                            | 71 |

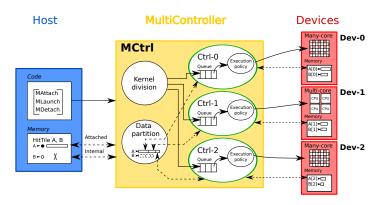

| 5.1 | Diagram of the Multiple-Device Controller library (MCtrl).                                                                                     | 79 |

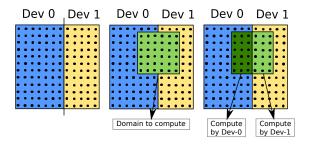

| 5.2 | Calculating the domains to compute for each device.                                                                                            | 83 |

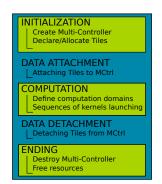

| 5.3 | Typical programming stages using the MCtrl library.                                                                                            | 83 |

| 5.4 | Matrix addition example programmed using our approach                                                                                          | 85 |

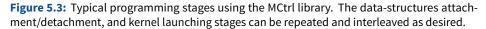

| 5.5 | An image of the Mandelbrot set with the limits <i>xmin</i> : $-1.4748333$ , <i>xmax</i> :                                                      |    |

|     | -0.9748333, ymin: -0.1791667, ymax: 0.1958333                                                                                                  | 87 |

| 5.6 | Performance results (in seconds) for experiments on Hydra using a group of                                                                     |    |

|     | 10 CPU-cores and a GPU.                                                                                                                        | 90 |

- xiii -

## XIV | LIST OF FIGURES

| 5.7         | Performance results (in seconds) for experiments on Hydra using a group of 10 CPU-cores and a GPU.                                                                                                              | 91         |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 7.1         | Sequential code of the Jacobi-1D benchmark.                                                                                                                                                                     | 106        |

| 7.2         | Excerpt of the communication generated code by Pluto compiler for the array <i>b</i> for the Jacobi-1D solver using the FOP scheme                                                                              | 107        |

| 7.3         | Pseudo-codes of the original $\pi$ (top left) and $\Pi$ (top right) functions, and our alternative implementation proposed.                                                                                     | 111        |

| 7.4         | Execution times with the original and alternative $\pi$ function with different problem sizes $N$ and different number of processes $P$                                                                         | 113        |

| 7.5         | Execution times of the codes generated using the FOP scheme, with the original and the alternative $\pi$ function implementation                                                                                | 116        |

| 8.1<br>8.2  | Sequential algorithm for the illustrative example                                                                                                                                                               | 121        |

| 0.2         | illustrative example (left), and code excerpts for the main blocks (right).                                                                                                                                     | 122        |

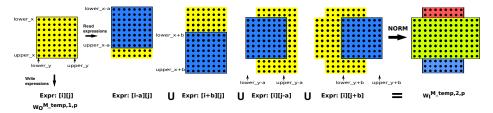

| 8.3         | Using the read and write data-access expressions inside the parallel structure of the illustrative example to calculate the working input and output index                                                      |            |

| 0.4         | sets $(W_I^2, W_O^1)$ for M_temp at a generic process.                                                                                                                                                          | 124        |

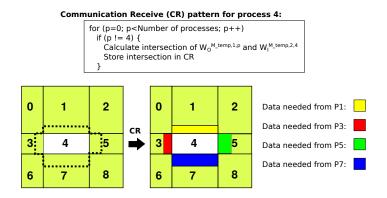

| 8.4         | Calculation of Communication Receive $(C_R)$ pattern between the two par-<br>allel structures of the illustrative example.                                                                                      | 124        |

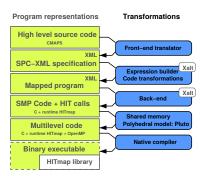

| 8.5         | Structure of the Trasgo transformation framework.                                                                                                                                                               | 126        |

| 8.6         | CMAPS code for the illustrative example.                                                                                                                                                                        | 127        |

| 8.7         | Generated code for illustrative example.                                                                                                                                                                        | 131        |

| 8.8         | Working-set index functions used to tailor the communication constructor                                                                                                                                        |            |

|             | algorithms for the four possible situations                                                                                                                                                                     | 134        |

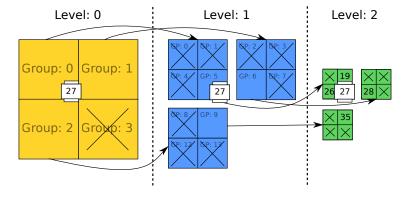

| 8.9<br>8.10 | Excerpt of generated code for illustrative example: main program Application of the proposed communication calculation technique when using a hierarchical QuadTree mapping policy to distribute a matrix on 64 | 135        |

|             | processes.                                                                                                                                                                                                      | 142        |

| 9.1         | Sequential algorithm for the illustrative example assuming a positive value                                                                                                                                     | 151        |

| 9.2         | of <i>rot.</i>                                                                                                                                                                                                  | 151<br>152 |

| 9.2<br>9.3  | Communication structures calculation.                                                                                                                                                                           | 152        |

| 9.3<br>9.4  | Communications in a Stencil-2D application.                                                                                                                                                                     | 155        |

| 9.5         | Trasgo input code for the illustrative example.                                                                                                                                                                 | 150        |

| 9.6         | Excerpt of the generated function that applies the input-code affine access expressions and periodic conditions to compute $T(W_I^{A,k}(p,L,rot))$ for                                                          | 157        |

|             | the illustrative example.                                                                                                                                                                                       | 160        |

| 9.7         | Calling both the communication calculation and execution functions in the                                                                                                                                       |            |

|             | target program of the illustrative example                                                                                                                                                                      | 161        |

$\oplus$

$\oplus$

$\oplus$

$\oplus$

$\oplus$

$\oplus$

$\oplus$

### LIST OF FIGURES | XV

$\oplus$

$\oplus$

$\oplus$

$\oplus$

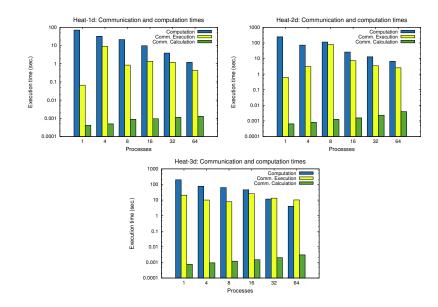

| 9.8<br>9.9 | Computation, communication calculation, and communication execution times in seconds for the Heat examples on the distributed-memory machine (log scale), using the problem sizes of Tab. 9.1 | 165 |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|            | times in seconds for the Heat examples on the shared-memory machine (log scale), using the problem sizes of Tab. 9.1.                                                                         | 166 |

| 10.1       | Motivating example algorithms using two different approaches.                                                                                                                                 | 169 |

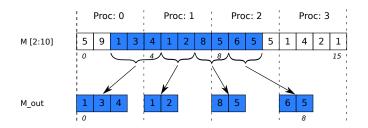

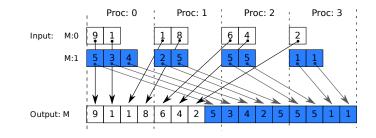

| 10.2       | Data redistribution performed by the <i>ArrayRemapRange</i> operator. In this case                                                                                                            |     |

|            | the call to the operator is $M\_out = ArrayRemapRange(M, \langle 2, 10 \rangle, L)$ .                                                                                                         | 171 |

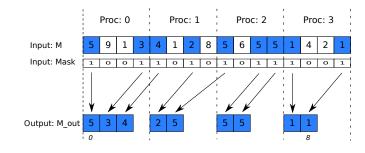

| 10.3       | Data redistribution performed by the ArrayRemapMask operator. In this case                                                                                                                    |     |

|            | the call to the operator is $M\_out = ArrayRemapMask(M, Mask, L)$ .                                                                                                                           | 172 |

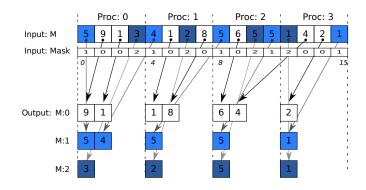

| 10.4       | Data redistribution performed by the <i>ArrayDivide</i> operator                                                                                                                              | 173 |

| 10.5       | Operation performed by the <i>ArrayMerge</i> operator                                                                                                                                         | 174 |

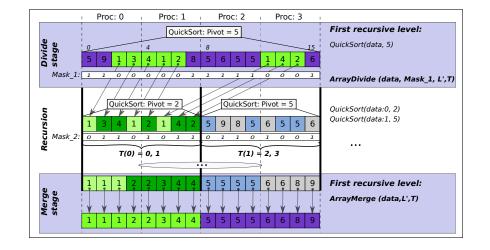

| 10.6       | Sequence of operations performed in the QuickSort algorithm in a distributed-                                                                                                                 |     |

|            | memory system using the <i>ArrayDivide</i> and <i>ArrayMerge</i> operators                                                                                                                    | 175 |

| 10.7       | Internal code of the ArrayRemapRange operator along with some auxiliary                                                                                                                       |     |

|            | macro functions                                                                                                                                                                               | 176 |

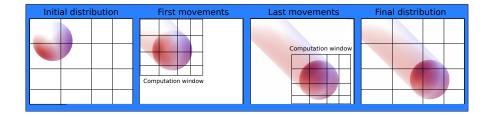

| 10.8       | Consecutive applications of the RayTracing algorithm on a moving sphere.                                                                                                                      | 180 |

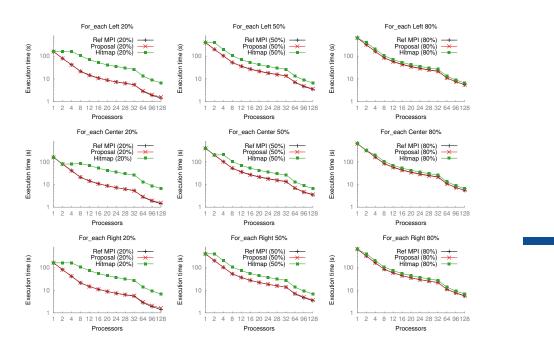

| 10.9       | Performance scalability results (in seconds) for the <i>for_each</i> algorithm in                                                                                                             |     |

|            | CETA, the distributed-memory system (logarithmic scale). $Size = 1000000$ .                                                                                                                   |     |

|            |                                                                                                                                                                                               | 183 |

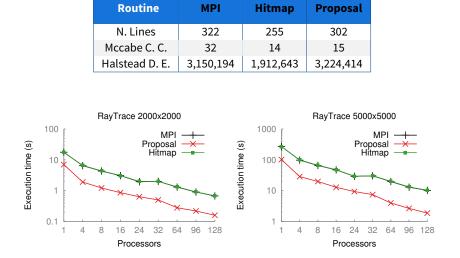

| 10.10      | Performance scalability results (in seconds) for the <i>RayTracing</i> algorithm in                                                                                                           |     |

|            | CETA with different image sizes (logarithmic scale).                                                                                                                                          | 185 |

$\oplus$

$\oplus$

$\oplus$

$\oplus - \bigcup_{i=1}^{k}$

XVI | LIST OF FIGURES

$\oplus$

$\oplus$

$\oplus$

$\oplus$

# List of Tables

$\oplus$

$\oplus$

$\oplus$

$\oplus$

$\oplus$

$\oplus$

$\oplus$

$\oplus$

| 3.1 | Measurements of the development effort metrics for the codes of the case studies.                                                                                                                                                       | 59  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.2 | Comparison in terms of the percentage of words that are common and can<br>be reused, should be deleted, or should be changed, when porting codes<br>between GPU and CPU versions using the native models, or the Controllers<br>model.  | 60  |

| 3.3 | Input data sizes and number of iterations selected for each case study in the performance experimental study.                                                                                                                           | 61  |

| 3.4 | Execution time (seconds) for the case studies versions using CUDA, or Con-<br>trollers for GPUs, with different input sizes.                                                                                                            | 61  |

| 4.1 | Performance results (seconds) comparing LEO reference codes with Con-<br>troller codes for different input sizes.                                                                                                                       | 73  |

| 4.2 | Comparison of number of code lines, code tokens, and cyclomatic complex-<br>ity between the Controller version and the version using native program-<br>ming models.                                                                    | 74  |

| 4.3 | Comparison in terms of the percentage of words that are common and can<br>be reused, should be deleted, or should be changed, when porting codes<br>between GPU and MIC versions using the native models, or the Controller<br>library. | 74  |

| 5.1 | Development effort measures for the four benchmarks when they are pro-<br>grammed using Cuda, OpenMP, and the proposed Multi-Controller library.                                                                                        | 88  |

| 8.1 | Input data sizes $(N \times N)$ , time loop iterations $(T)$ , and threshold parameter, for the different benchmarks in the experimental studies conducted                                                                              | 100 |

| 8.2 | in Heracles and CETA                                                                                                                                                                                                                    | 139 |

|     | the cluster Atlas with different tunning of the tile size                                                                                                                                                                               | 140 |

| 8.3 | Execution time for the communication determination for Jacobi-2D solver (seconds).                                                                                                                                                      | 141 |

- xvii -

## XVIII | LIST OF TABLES

$\oplus$

$\oplus$

$\oplus$

$\oplus$

| 8.4  | Performance (in seconds) obtained for the three benchmarks chosen             | 143 |

|------|-------------------------------------------------------------------------------|-----|

| 8.5  | Maximum variation in the execution times for each benchmark in Heracles       |     |

|      | and CETA, when using Trasgo and Pluto.                                        | 145 |

| 8.6  | Main execution times (in seconds) for the five benchmarks chosen from the     |     |

|      | Polybench.                                                                    | 145 |

| 8.7  | Performance (in seconds) of Polybench codes, generated for distributed-       |     |

|      | memory by Trasgo, and by Pluto-MPI, broken down into computation and          |     |

|      | communication times (including calculation and execution)                     | 147 |

| 9.1  | Input data sizes $(N)$ and time loop iterations $(T)$ , for benchmarks in the |     |

| 9.1  | experimental studies.                                                         | 162 |

| 9.2  | Study 1: Performance (in seconds) for the illustrative example, Cannon's      | 102 |

| 1.2  | algorithm, and the MG real-world application.                                 | 163 |

| 9.3  | Comparison of development effort measures for three case studies.             | 164 |

| 2.0  |                                                                               | 101 |

| 10.1 | Summary of the implemented STL routines for one dimensional numeric           |     |

|      | arrays, for distributed-memory systems, using the new four operators          | 179 |

| 10.2 | Measures of development effort for the STL study cases, comparing our         |     |

|      | proposal with MPI.                                                            | 184 |

| 10.3 | Measures (in miliseconds) of performance for the STL study cases comparing    |     |

|      | our proposal with MPI, using 128 MPI processes in CETA                        | 184 |

| 10.4 | Measures of development effort for the RayTracing algorithm, comparing        |     |

|      | our proposal with MPI.                                                        | 185 |

$\oplus$

$\oplus$

$\oplus$

# Resumen de la Tesis Doctoral

$\oplus$

$\oplus$

$\oplus$

E nodo más frecuente de resolver aplicaciones de HPC (High performance Computing) en tiempos de ejecución razonables y de una forma escalable es mediante el uso de sistemas de cómputo paralelo. Sin embargo, su uso enfrenta al programador retos específicos.

Este capítulo describirá esos retos, y de acuerdo a los problemas que se vayan identificando, presentará los objetivos, la pregunta de investigación de esta Tesis Doctoral, y se describirán de forma general las contribuciones aportadas a lo largo de la Tesis Doctoral, para resolver las cuestiones planteadas por la pregunta de investigación, y conseguir los objetivos descritos.

$\oplus$

### R.1 Motivación

En esta sección presentamos la motivación que da lugar al planteamiento de esta Tesis Doctoral. En primer lugar repasaremos la evolución de los sistemas de computo paralelos. Veremos como esta evolución ha llevado a la necesidad de diseñar nuevos modelos de programación y nuevos sistemas de control y gestión del paralelismo durante la ejecución. Analizaremos diferentes clases de propuestas para dichos modelos y herramientas, y descubriremos cuestiones aún no resueltas. Esta observación nos llevará a plantear los diversos retos que esta Tesis Doctoral trata de resolver. En esta sección introduciremos también el trabajo realizado en este ámbito por el grupo de investigación Trasgo, en el que se ha desarrollado el trabajo principal que se describe en este volumen.

#### **R.1.1** Computación paralela

Existen muchos problemas de cómputo, como por ejemplo los relacionados con las simulaciones médicas, el análisis de tráfico o flujo en redes, o la navegación de coches autónomos, que requieren simulaciones muy complejas, niveles de precisión muy altos o respuestas al problema en un tiempo limitado y generalmente muy corto [9]. Estos requisitos se corresponden con programas de un alto coste computacional y hacen que la ejecución de estos programas sea prohibitiva con programas o máquinas que ejecutan las instrucciones de forma únicamente secuencial.

Una solución para reducir el tiempo de ejecución de este tipo de aplicaciones es el aumento de la frecuencia de reloj en los sistemas hardware que ejecutan los programas. Sin embargo, la evolución de la velocidad de reloj de los procesadores y chips basados en una alta escala de integración de transistores se está viendo limitada. El consumo de energía y el calor disipado aumenta demasiado rápido con la frecuencia con las tecnologías actuales [47]. Por ello, la tendencia actual pasa por utilizar la enorme cantidad de transistores que se puede integrar en un reducido espacio para construir chips con varios elementos de computo que pueden trabajar de forma simultánea o paralela. Así mismo, dentro de la misma máquina se pueden colocar varios dispositivos paralelos, e interconectar con tecnología de red varias máquinas para formar enormes y complejos sistemas capaces de ejecutar multitud de subprogramas o tareas simultáneamente. Por tanto, la división de los trabajos en varias tareas independientes puede ser una solución para los problemas de alto coste computacional mencionados [3]. Cuántas más unidades de procesamiento tenga una máquina, más tareas pueden ser creadas y ejecutadas simultáneamente, reduciendo el tiempo total de ejecución. Este método de diseño de programas nos proporciona soluciones escalables. Así, los problemas que necesitan cada vez más cantidad de cómputo, cuya carga computacional crece, se pueden resolver en tiempos razonables con un número proporcionalmente mayor de elementos de cómputo. Esta característica ha hecho que hoy en día los sistemas paralelos se estén convirtiendo en la base de la computación de alto coste o alto rendimiento (HPC, High-Performance Computing).

#### R.1 MOTIVACIÓN | 3

La necesidad de dar con una solución para los problemas de HPC ha fomentado el desarrollo de los sistemas paralelos, haciendo que durante las últimas décadas el número de elementos de procesamiento en los sistemas paralelos vaya aumentando. Por otra parte, el tiempo y el esfuerzo necesario para el desarrollo de programas para su ejecución en paralelo ha crecido desmesuradamente [56] debido a: (1) la inherente complejidad de crear y coordinar las tareas a ejecutar por cada elemento de procesamiento; (2) la falta de modelos de programación, herramientas de desarrollo y estrategias de diseño que realmente permitan la portabilidad de los códigos entre sistemas diferentes; y (3) la gran diversidad de tipos y arquitecturas en las plataformas de cómputo paralelo.

A lo largo de esta sección repasaremos las arquitecturas de las máquinas más usadas actualmente para la computación en paralelo. Después, describiremos los modelos de programación más conocidos y usados para cada arquitectura.

#### **R.1.2** Sistemas para la computación paralela

La evolución de los sistemas de cómputo se ha focalizado en el diseño de nuevas arquitecturas con un creciente nivel de paralelismo, en lugar de en el desarrollo de procesadores más rápidos. La computación paralela representa en muchas situaciones la única solución escalable para resolver ciertos problemas en tiempos de ejecución razonables.

Existen diversos términos y denominaciones referidos a sistemas cuyas arquitecturas incluyen múltiples elementos de cómputo independientes. El término *multi-core* se refiere a la integración de varias unidades de procesamiento en un único chip, donde además cada unidad de procesamiento puede operar como un procesador de propósito general. El uso de varias unidades de procesamiento a la vez implica un aumento del rendimiento, sin la necesidad de aumentar la frecuencia de reloj, debido a que la carga de trabajo puede ser distribuida entre los diversos elementos de procesamiento. De acuerdo a su diseño, los elementos de procesamiento pueden compartir espacio de memoria, formando una memoria global, o no. La presencia de un único espacio de memoria global hace la programación de estas plataformas más natural para los programadores habituados a los modelos clásicos de programación secuencial. Las operaciones de memoria de solo lectura serán invisibles para el programador, y programadas de forma similar que en los programas secuenciales. Sin embargo, las operaciones de escritura requieren que el programador use sistemas de exclusión mutua para los accesos concurrentes, o sincronizaciones de lectura-escritura, haciendo su tarea mucho más complicada.

Por otra parte, los sistemas que no comparten espacio de memoria presentan retos aparentemente diferentes al programador. Cada unidad de procesamiento de una máquina puede tener su propio espacio de memoria local. Así, todas las interacciones entre diferentes elementos de procesamiento deben ser realizadas, por ejemplo, mediante el uso de abstracciones de comunicación como son los mensajes, los cuales podrán transferir datos, trabajo o simplemente sincronizar acciones entre los procesos. 4 | RESUMEN DE LA TESIS DOCTORAL

#### Coprocesadores para la computación paralela

Un coprocesador puede ser considerado como un dispositivo de computación que se añade a un sistema por otra parte completo, con el fin de ejecutar software especializado. Los coprocesadores más usados para supercomputación hoy en día son las GPUs (Graphics Processing Unit) [133]. Las GPUs fueron originalmente diseñadas para ayudar al procesador principal en el procesamiento gráfico. En las aplicaciones de procesamiento gráfico, la reutilización de datos es pequeña, y los programas son muy simples. Por ello, el diseño de las GPUs está basado en el uso de pequeñas cachés on-chip con una colección de Unidades Aritmético-Lógicas (ALUs) sencillas. El uso de coprocesadores como procesadores de propósito general ha sido tendencia en la supercomputación desde que Nvidia lanzase la tarjeta Tesla en 2007. Aunque las GPUs [133] fueron originalmente diseñadas para el procesamiento gráfico, sus potentes capacidades de cómputo masivamente paralelo han hecho su uso muy popular en las aplicaciones de HPC, creando una nueva tendencia basada en ellas, GPGPU (General-Purpose Computing on Graphics Processing Units).

Durante los últimos años han surgido nuevos dispositivos aceleradores para atacar eficientemente el tipo de problemas que no encajan bien con la arquitectura de las GPUs. Un ejemplo es la familia de tarjetas Intel Xeon Phi (lanzada en 2012), la cual también es conocida como Many Integrated Cores (MICs) [73]. El coprocesador Xeon Phi es un acelerador con muchos cores de propósito general basados en la tecnología x86, con unidades de vectorización mejoradas y mejor ancho de banda de memoria.

# Computación Heterogénea: Sacando partido a todos los tipos de arquitecturas a la vez.

La evolución de los supercomputadores puede seguirse gracias al proyecto Top500 [130], que cada seis meses publica una clasificación de los 500 computadores más potentes en el mundo, en base a su velocidad de ejecución de unos programas de prueba concretos. Los supercomputadores actuales están compuestos por varios nodos (máquinas interconectadas) con memoria distribuida donde cada nodo puede tener diferentes capacidades de cómputo, jerarquías de memoria o coprocesadores asociados como GPUs o Xeon Phis. En muchos casos, las características de computación de cada nodo son muy diferentes. Este tipo de sistemas son denominados *Sistemas Heterogéneos* [26].

#### **R.1.3** Modelos de programación paralelos

Según el trabajo de Balaji [12], un modelo de programación puede entenderse como una máquina abstracta para que un programador escriba instrucciones. Típicamente, estos modelos de programación son instanciados en lenguajes en si mismos, o en bibliotecas de funciones.

Esta nueva era de la computación en paralelo está requiriendo un continuo esfuerzo de investigación en el diseño y desarrollo de nuevos modelos de programación, apropiados para explotar la computación paralela en aplicaciones de alto coste computacional. Programar

#### R.1 MOTIVACIÓN | 5

sistemas paralelos es complicado. Con el fin de lograr una ejecución correcta del programa y que realmente aproveche el nivel de paralelismo que ofrecen las arquitecturas modernas, el programador debe razonar teniendo en cuenta los comportamientos estocásticos asociados con la ejecución simultánea y los costes asociados a los movimientos de datos entre múltiples unidades de procesamiento y entre sus diferentes niveles en la jerarquía de memoria. Así, los modelos de programación paralelos definen de forma explícita o implícita dos submodelos. El primero es un modelo de ordenación y sincronización entre las secuencias de operaciones que el código ejecutará, generalmente llamado *modelo de ejecución*. El segundo es un modelo que determina como mover los datos entre los nodos y las jerarquías de memoria del sistema paralelo, llamado *modelo de memoria*.

Existen cuatro pilares o características fundamentales que representan las posibles preferencias del programador entre las características de un modelo de programación, independientemente de que sea secuencial o paralelo: (1) *Productivo*, capaz de expresas algoritmos abstractos con facilidad, (2) *Portable*, capaz de ser usado en cualquier arquitectura de computación, (3) *Eficiente*, capaz de producir un buen rendimiento adecuado con el hardware donde se esta ejecutando, y (4) *Expresivo*, capaz de representar o expresar un gran rango de clases de algoritmos.

Sería ideal diseñar un lenguaje de programación que cumpla con las cuatro características expuestas, sin embargo esto parece imposible por el momento. Por ello, existen muchos lenguajes de programación secuencial, cada uno aportando diferentes soluciones a la hora de expresar algoritmos y transformarlos a código ejecutable, focalizándose en una combinación particular de las anteriores características. Este comportamiento no es diferente para los sistemas paralelos. Los diferentes usuarios tienen preferencias entre los niveles de abstracción que nos dan las combinacións de los cuatro pilares. En esta sección veremos un resumen de los modelos de programación paralela más conocidos y usados para HPC y la supercomputación actualmente.

#### Clasificación de los modelos de programación paralela

Muchos modelos y lenguajes de programación han surgido para la programación en paralelo, con el fin de abstraer al programador de muchos de los problemas de implementación que típicamente aparecen en este tipo de computo. Algunos nos abstraen por completo del modelo de arquitectura, pero suelen tener problemas de eficiencia en la implementación sobre arquitecturas completas. Para poder utilizar formas de implementación más eficientes y específicas, otros se focalizan en alguno de los modelos fundamentales de arquitectura, como son por ejemplo los modelos de memoria compartida, o de memoria distribuida. OpenMP y el paradigma de paso de mensajes (implementado por ejemplo en bibliotecas MPI) son los métodos de programación paralela más extendidos y usados para memoria compartida y distribuida respectivamente [32, 59]. Ambas aproximaciones han sido declaradas como los modelos más básicos de programación paralela, y dominan el campo de la programación para HPC desde finales de los años 90 del siglo pasado [44].

#### 6 | RESUMEN DE LA TESIS DOCTORAL

OpenMP [33, 40] es una API (application programming interface) que facilita la programación en paralelo para sistemas de memoria compartida. Está compuesta por un conjunto de directivas, pragmas, funciones de biblioteca y un sistema de tiempo de ejecución que es capaz de manejar la creación de hilos, su sincronización y por tanto de sus operaciones, y las interacciones que se producen en las operaciones en memoria compartida. Originalmente, OpenMP fue diseñado para paralelizar códigos secuenciales con un bajo esfuerzo de programación. Los códigos secuenciales son anotados con una serie de pragmas o anotaciones que no son parte del lenguaje, pero incluyen información extra para el compilador. Estas anotaciones son procesadas por el compilador, que debe tener la tecnología adecuada para entenderlas y utilizarlas para producir un código que resuelva los problemas de la paralelización siguiendo las pautas indicadas en los pragmas. Originalmente OpenMP estaba orientado a la paralelización de iteraciones de bucles. Actualmente, OpenMP también provee herramientas orientadas a tareas dinámicas y estructuras para la programación paralela más complejas [10].

Existen también otros modelos menos abstractos para memoria compartida como POSIX threads (PThreads) [29, 78], que es la herramienta en la que se apoyan muchos compiladores de OpenMP para la gestión de las tareas a bajo nivel. Se trata de un estándar que define un conjunto de tipos y funciones, para el que se han implementado bindings en los lenguajes de programación más populares, como por ejemplo C/C++, Fortran, Python, etc. La biblioteca de Pthreads nos da una serie de funciones para la creación y destrucción de hilos y para la coordinación de las actividades de los hilos. Sin embargo, comparado con OpenMP, la interfaz de Pthreads es de un nivel más bajo, necesitando el programador un mayor esfuerzo de desarrollo.

La programación en sistemas de memoria distribuida impone retos específicos. El *paso de mensajes* es el modelo de programación más extendido para estos sistemas. Toda la información necesaria para la ejecución del proceso local, que pueda estar contenida en un proceso remoto, debe ser enviada antes al proceso local mediante un intercambio de mensajes. El estándar MPI ha dominado el campo de las propuestas de este modelo, existiendo implementaciones muy eficientes, y siendo hoy en día el estándar de facto para las aplicaciones de HPC en arquitecturas distribuidas [58, 59, 89]. Sin embargo, cuando el programador usa las especificaciones de MPI aun tiene que tratar con problemas de diseño e implementación complejos, como son las decisiones acerca de la partición y la localidad de datos vs. la sincronización y los costes de las comunicaciones. No solo MPI trata con los retos de la programación en sistemas distribuidos. También existen soluciones como GASnet [20] que proveen una capa de programación de bajo nivel para la implementación de lenguajes y bibliotecas paralelas con un espacio de memoria global (modelos PGAS), que proveen de una capa de abstracción similar a la memoria compartida, con el objetivo de simplificar la programación a los usuarios finales.

La programación de co-procesadores es diferente de la programación de sistemas multicore o en memoria distribuida en muchos aspectos. El programador tiene que tratar con muchos detalles manualmente, como por ejemplo las transferencias de datos al dispositivo, o

#### R.2 OBJETIVOS DE LA TESIS DOCTORAL | 7

la configuración de los parámetros de ejecución de cada bloque paralelo. NVIDIA presentó en 2007 CUDA [102], un nuevo modelo de programación especialmente diseñado para los aceleradores GPU de NVIDIA. El modelo de programación CUDA solo se puede utilizar actualmente con los aceleradores GPU de NVIDIA. Para otros tipos de GPUs existen otros modelos de programación similares como son OpenCL [127] o BrookGPU [27]. Para otros tipos de aceleradores como la Xeon Phi, modelos de programación basados en pragmas, como LEO [101], ofrecen mecanismos de programación similares.

#### Programación paralela para sistemas heterogéneos multinivel.

Diferentes modelos de programación han sido establecidos para cada diferente tipo de dispositivo o arquitectura como hemos descrito previamente. Esto nos indica, que para aprovechar los sistemas paralelos heterogéneos actuales, un programador debe ser experto en las herramientas y abstracciones existentes para memoria distribuida (e.g MPI, GASNet [20], etc), los modelos de programación para sistemas de memoria compartida (e.g OpenMP), y los modelos de programación específicos para para cada tipo de co-procesador (e.g CUDA, OpenCL, o tecnologías equivalentes), con el fin de crear programas híbridos que puedan explotar eficientemente todas las capacidades de la máquina [141]. Además, el programador también tiene que tratar con la distribución de trabajo apropiada para cada caso entre los diferentes nodos y dispositivos, asignando a cada uno, una carga de trabajo proporcional a sus capacidades y capacidad de cómputo. Actualmente, todos estos problemas deben ser resueltos por el programador, haciendo así la programación de una máquina heterogénea un auténtico reto.

## R.2 Objetivos de la Tesis Doctoral

De acuerdo con los problemas encontrados y descritos en la sección anterior, la pregunta de investigación que esta Tesis doctoral trata de resolver es la siguiente:

Es posible desarrollar: (1) Abstracciones simples que hagan transparente y uniforme el desarrollo, despliegue y coordinación de programas entre diferentes sistemas y arquitecturas paralelas de cómputo, y (2) nuevas técnicas de tiempo de ejecución que, basándose en las dependencias de datos de un programa, puedan distribuir y comunicar de forma automática los datos, de forma transparente para el programador, una vez que las características de la plataforma de ejecución sean conocidas?

#### R.2.1 Metodología de investigación

La metodología de investigación usada en esta Tesis esta basada en el método experimental y el método de ingeniería software, compuestos ambos for cuatro fases: Observar la 8 | RESUMEN DE LA TESIS DOCTORAL

solución existente, proponer una solución mejor, desarrollar las soluciones propuestas y hacer mediciones de índices de calidad, comparar y analizar las nuevas soluciones [1]. Es una metodología iterativa donde en cada iteración la solución se refina hasta encontrar la más apropiada, recordando las etapas de cada iteración a las fases del clásico método científico: Búsqueda de problema, formulación de hipótesis, predicción y validación de hipótesis.

1. Observar las soluciones existentes.

En la fase exploratoria se estudiará la literatura y el estado del arte del campo de investigación tratando de determinar posibles mejoras.

2. Proponer soluciones mejores.

Esta fase está dedicada al análisis y diseño de soluciones mejores, tratando de superar los límites de las propuestas previas o mejorando los métodos existentes en la literatura.

3. Desarrollar la solución.

El objetivo de esta fase es desarrollar un prototipo para demostrar las características de nuestra solución.

4. Medir y analizar la nueva solución.

Por último, los prototipos implementados son empíricamente evaluados y comparados con las diferentes alternativas. El objetivo de esta evaluación es validar la nueva solución propuesta y corroborar que los problemas descubiertos en la primera fase fueron resueltos.

#### **R.2.2** Objetivos

Hemos definido dos tareas principales con el fin de resolver la pregunta de investigación. Cada tarea se trata en una de las dos partes en las que se organiza esta Tesis Doctoral, y propone diferentes objetivos o items a cumplir para resolver el problema de investigación global considerado (ver Fig. 1). La metodología de investigación descrita se aplicará a cada objetivo.

#### Trabajo previo

En los últimos años el grupo de investigación Trasgo [61] ha diseñado y desarrollado Hitmap [48, 55], una biblioteca altamente eficiente para el particionado y mapeado jerárquico en memoria distribuida de estructuras de datos indexadas como vectores, matrices multidimensionales, matrices dispersas o grafos. Hitmap esta diseñada para utilizar una abstracción que permita simultáneamente una visión global o local de una computación paralela, permitiendo la creación, manipulación, distribución y eficiente comunicación de estructuras de datos *teseladas* (particionadas) de forma abstracta. El programador no necesita pensar en el número de procesos y procesadores. En su lugar, Hitmap usa una abstracción para la construcción de R.2 OBJETIVOS DE LA TESIS DOCTORAL | 9

$\oplus$

$\oplus$

$\oplus$

Figura 1: Objetivos y estructura de la Tesis Doctoral.

patrones de comunicación para las estructuras distribuidas de cualquier nivel, con estados globales claramente identificados. Así, las operaciones de codificación y verificación son mucho más fáciles.

Esta biblioteca da soporte a funcionalidades de: (1) Organización de los elementos de proceso en topologías virtuales; (2) Partición y asignación de partes de las estructuras de datos a los diferentes procesos usando diferentes técnicas de equilibrio de carga de forma modular; (3) Determinación y gestión automática de los procesos inactivos en cualquier estado de la computación; (4) Identificación de los procesos vecinos o relacionados para mejorar las comunicaciones en su caso; y (5) Construcción abstracta de patrones de comunicación, que además son reutilizables en algoritmos iterativos.

#### Parte I: Simplificando la programación de sistemas heterogéneos basados en aceleradores

En la primera parte de la Tesis Doctoral presentaremos un modelo de programación que simplifica la programación en paralelo de sistemas heterogéneos, entendiendo un sistema

$\oplus$

#### 10 | RESUMEN DE LA TESIS DOCTORAL

heterogéneo como aquel sistema compuesto por un host (proceso principal) y diferentes dispositivos de computación asociados al host (grupos de núcleos de CPU, o aceleradores del tipo GPUs o XeonPhi).

# Objetivo 1: Diseñar y desarrollar un modelo de programación para unificar la programación de CPUs y GPUs.

- (*Observación*) Actualmente el uso de aceleradores hardware, como las unidades de procesamiento gráfico (GPUs), es clave para resolver problemas de alto coste computacional que requieren HPC. Sin embargo, programar soluciones para un eficiente despliegue en este tipo de dispositivos es una tarea muy difícil, que requiere del tratamiento manual de las transferencias de memoria y de los parámetros de configuración. El programador es el responsable de realizar un estudio de los datos necesarios en cada momento para la computación en cada diferente coprocesador, teniendo en cuenta a su vez los detalles de la arquitectura de ejecución.

- (Propuesta e Proponemos el concepto de Controller, una entidad abstracta que permite ocultar los implementación)

detalles de las comunicaciones y lanzamientos de kernels en los aceleradores hardware, facilitando su programación. El modelo también ofrece la posibilidad de definir y lanzar kernels para CPU en procesadores multi-core, usando la misma abstracción y metodología que para las GPUs.

- (Resultados) Presentaremos una implementación del modelo de los Controladores en un prototipo construido como una biblioteca de funciones, junto con una serie de casos de estudio. Demostraremos que el uso de esta biblioteca reduce el esfuerzo de programación y los costes de portar el código entre dispositivos, sin añadir sobrecostes en los tiempos de ejecución cuando se comparan con soluciones directamente programadas y optimizadas con CUDA u OpenMP.

## Objetivo 2: Soporte para un nuevo tipo de aceleradores como el coprocesador Xeon Phi.

- (Observación) Soportar diferentes tipos de dispositivos como las GPUs o las Xeon Phis en los modelos de programación actuales es vital para explotar los sistemas paralelos. Diferentes tipos y familias de aceleradores son usados en las arquitecturas modernas de cómputo, como podemos observar en la configuración de los los supercomputadores de la lista TOP500 [130]. Sin embargo, los modelos de programación usados típicamente para GPUs y Xeon Phis son muy diferentes.

- (Propuesta e En este punto proponemos una extensión del modelo de programación heterogéneo implementación) anterior para GPUs y CPUs, obteniendo una nueva aproximación a la programación homogénea de CPUS, GPUs y XeonPhis. Esta contribución extiende el modelo de los Controladores anterior y su implementación, combinando el modelo de comunicaciones diseñado para GPUs con el modelo de ejecución diseñado para CPUs. Esto resulta en una nueva solución para dar soporte a la Xeon Phi.

\_\_\_\_

#### R.2 OBJETIVOS DE LA TESIS DOCTORAL | 11

(*Resultados*) Los resultados experimentales de esta parte muestran que usando la nueva solución, el esfuerzo de programación necesario para cambiar la plataforma de ejecución ha sido muy reducido en muchos casos de estudio. Por ejemplo, usando nuestro modelo para programar el benchmark Mandelbrot, el 97 % del código es reutilizado entre la implementación para GPU y la de Xeon Phi.

# Objetivo 3: Diseñar y desarrollar un modelo de programación adaptable, simple y eficiente para la programación de sistemas con múltiples dispositivos heterogéneos.

- (Observación) Existen muchas propuestas para simplificar la programación, el manejo de varios aceleradores, y la programación de sistemas híbridos mezclando aceleradores y CPUs. Sin embargo, la portabilidad muchas veces compromete la eficiencia de los programas en los diferentes dispositivos. Además, hay detalles acerca de la coordinación y el manejo de memoria que deben ser todavía atacados por el programador.

- (Propuesta e En este objetivo proponemos la entidad Multi-Controlador (MCtrl), una entidad absimplementación) tracta implementada también en una biblioteca. Esta entidad coordina los diferentes dispositivos (incluyendo aceleradores o grupos de CPUs) que se pueden encontrar en un sistema heterogéneo. Nuestra propuesta usa el modelo de Controladores y la biblioteca Hitmap para crear un nuevo modelo de programación que mejora las soluciones del estado del arte, simplificando la partición y mapeo de datos y haciendo transparente la computación de los kernels en los diferentes dispositivos. El sistema runtime selecciona y ejecuta automáticamente la mejor implementación de kernel existente (entre las suministradas por el programador) para cada dispositivo, haciéndose cargo también de los movimientos necesarios de datos y ocultando los detalles del lanzamiento de los kernels en los diferentes dispositivos.

- (*Resultados*) Los resultados de un estudio experimental con varios casos de estudio indican que nuestra abstracción permite el desarrollo de programas flexibles y eficientes en múltiples dispositivos o unidades computacionales, que se adaptan a los entornos heterogéneos.

Al final de esta parte de la Tesis Doctoral obtendremos un modelo de programación que simplifica la programación en paralelo sobre sistemas heterogéneos, logrando una gran eficiencia en términos de tiempo de ejecución para aplicaciones que no tengan dependencias de datos.

El soporte de aplicaciones con dependencias de datos en sistemas que incluyen dispositivos con espacios de memoria separados, requiere el diseño y desarrollo de técnicas para realizar automáticamente las transferencias de datos entre dispositivos. Este tipo de técnicas son presentadas en la parte II.

#### 12 | RESUMEN DE LA TESIS DOCTORAL

#### Parte II: Automatizando el manejo de datos en sistemas heterogéneos con memoria distribuida.

Los casos más significativos donde los dispositivos tienen un espacio de memoria separado son los sistemas distribuidos. En esta parte de la Tesis Doctoral presentamos un conjunto de técnicas genéricas y automáticas que simplifican la programación en paralelo sobre sistemas de memoria distribuida. Estas hacen transparente al programador muchos de los problemas relacionados con la partición, reserva y transferencia de datos.

# Objetivo 4: Diseño y desarrollo de una técnica en tiempo de ejecución que calcula automáticamente las comunicaciones agregadas para las aplicaciones con expresiones afines y uniformes en el acceso a datos.