# E. T. S. Ingeniería de Telecomunicaciones

Trabajo Fin de Máster

Máster Universitario de Investigación en Tecnologías de la Información y las Comunicaciones

Módulo Especialización en Análisis y Diseño en Electrónica y Comunicaciones

Estudio experimental de estructuras para su aplicación en memorias resistivas

Autor:

Luis Antonio Domínguez López

Tutor:

Helena Castán Lanaspa Salvador Dueñas Carazo

# Agradecimientos

A las primeras personas a las que estoy muy agradecido es a mis padres, siempre a mi lado, apoyándome en todas mis decisiones y retos y con su confianza y aliento he podido alcanzar mis metas.

A mis tutores Helena Castán y Salvador Dueñas, que me dieron la oportunidad de iniciarme en el mundo de la ciencia, siempre he contado con su apoyo y conocimentos y he podido aprender muchísimo de ellos. Han sido una fuente inagotable de motivación y positividad.

A mi profesor Héctor García con el que he compartido muchas horas de laboratorio y me ha enseñado los entresijos de la caracterización de dispositivos, siempre dispuesto a echar una mano.

A mis compañeros de grupo Óscar, Alfredo y Miriam, con los que la experimentación se ha hecho más amena y divertida. Y al resto de compañeros de la universidad por toda la ayuda prestada.

A Marcos Herrero, Diego Calvo, Javier San José y Miguel Benito, con amigos así se puede superar cualquier cosa, siempre puedo contar con ellos.

Muchísimas gracias a todos.

## Resumen

La memoria de acceso aleatorio resistivas (RRAM) está en la actualidad siendo investigada y desarrollada como reemplazo de la tecnología flash, por el momento usada para almacenar información en dispositivos móviles, instrumentación científica, electrónica médica, robótica industrial, etc. Estas nuevas memorias no volátiles están basadas en estructuras metal-aislante-metal (MIM) o estructuras metal-asilante-semiconductor (MIS) las cuales manifiestan el fenómeno de conmutación resistiva. Este fenómeno va a depender de las características del aislante y los materiales que compongan el electrodo metálico. Este trabajo tiene como objetivo conocer el comportamiento de estructuras tanto MIS como MIM como células RRAM. Para ello, se realizará una caracterización eléctrica en profundidad de las estructuras, que determine las propiedades y el comportamiento de estos dispositivos.

En este proyecto, se medirán las características del dieléctrico y de la interface que forman parte de una estructura MIS compuesta por  $Ni/Capa\ dieléctrica/Si-n^+$  por medio de una gran variedad de técnicas, como medidas de Capacidad - Tensión o transitorios de banda plana  $(V_{fb}-t)$ . También se medirán estructuras MIM compuestas por  $W/Ti/Capa\ dieléctrica/TiN/Ti$  en la que se aplicarán técnicas de medida de corriente-tensión y de conductancia-tensión que permitan obtener un estudio del funcionamiento global.

## Abstract

Resistive random access memory (RRAM) is currently being researched and developed as a replacement for flash technology, at the moment used to store information in mobile devices, scientific instrumentation, medical electronics, industrial robotics, etc. These new non-volatile memories are based on metal-insulator-metal (MIM) structures or metal-insulator-semiconductor (MIS) structures which manifest the phenomenon of resistive switching. This phenomenon will depend on the characteristics of the insulator and the materials that make up the metal electrode. The objective of this work is to know the behavior of both MIS and MIM structures as RRAM cells. For this, an electrical characterization in depth of the structures will be carried out, which determines the properties and behavior of these devices.

In this project, the characteristics of the dielectric and the interface that are part of a MIS structure composed of  $Ni/Dielectric\ Layer/Si-n^+$  will be measured through a variety of techniques, such as Capacity - Voltage measurements or flat band transients  $(V_{fb}-t)$ . MIM structures composed of  $W/Ti/Dielectric\ Layer/TiN/Ti$  will also be measured in which current-voltage and conductance-voltage measurement techniques will be applied to obtain a global performance study.

"If I have seen further it is by standing on the shoulders of a giant" Isaac Newton

"The scientific man does not aim at an inmediate result. He does nost expect that his advanced ideas will be readily taken up. His work is like that of the planter - for the future. His duty is to lay the foundation for those whoare to com, and point the way. He lives and labors and hopes"

Nikola Tesla

# Índice general

| Ι  | Int  | roducción y Objetivos                                                               | 1  |

|----|------|-------------------------------------------------------------------------------------|----|

| 1. | Intr | oducción                                                                            | 9  |

|    | 1.1. | Motivación y objetivos                                                              | 6  |

|    |      | 1.1.1. Objetivos                                                                    | 6  |

|    |      | 1.1.2. Estructura del trabajo                                                       | 7  |

|    | 1.2. | Tipos de memorias                                                                   | 7  |

|    |      | 1.2.1. Dispositivos de Almacenamiento Masivo                                        | 7  |

|    |      | 1.2.2. Memorias de Acceso no Aleatorio                                              | 8  |

|    |      | 1.2.3. Memorias de Acceso Aleatorio                                                 | 8  |

|    | 1.3. | Bases de las memorias RRAM                                                          | 11 |

|    |      | 1.3.1. Tipos de RS según su polaridad                                               | 12 |

|    |      | 1.3.2. Materiales usados en RRAMs                                                   | 13 |

|    |      | 1.3.3. Forming, SET Y RESET                                                         | 14 |

|    | 1.4. | Procesos de conmutación resistiva                                                   | 15 |

|    |      | 1.4.1. Memoria de metalización electroquímica                                       | 15 |

|    |      | 1.4.2. Memoria de cambio de valencia                                                | 18 |

|    |      | 1.4.3. Memoria termoquímica                                                         | 19 |

|    | 1.5. | Dieléctricos de alta-k                                                              | 21 |

| II | Pr   | rocedimiento Experimental                                                           | 23 |

| 2. | Inst | rumentos de Medida                                                                  | 25 |

|    | 2.1. | Sistema de caracterización de semiconductores Keithley 4200-SCS $\ \ldots \ \ldots$ | 25 |

|    | 2.2. | Analizador parámetros en continua de semiconductores HP 4155B $\ \ldots \ \ldots$   | 27 |

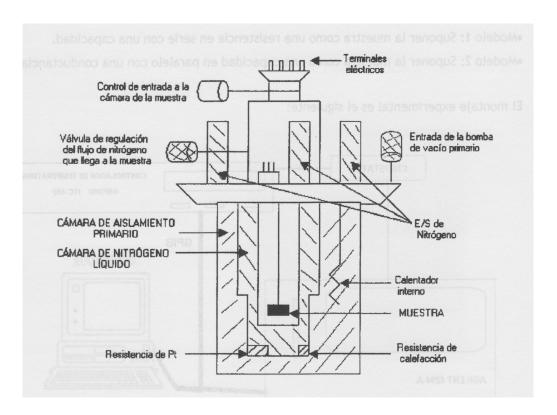

|    | 2.3. | Criostato de nitrógeno líquido Oxford DN1710                                        | 28 |

|    | 2.4. | Controlador de temperatura Oxford Instruments ITC503                                | 30 |

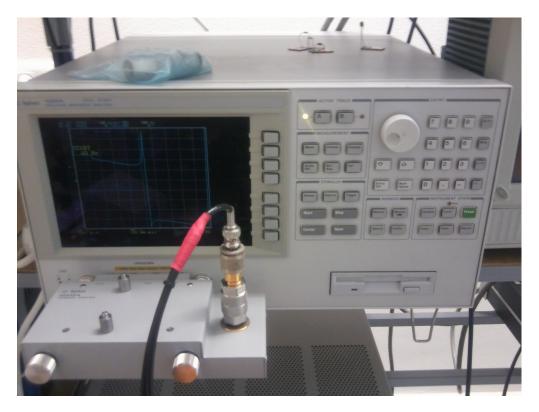

|    | 2.5. | Analizador de impedancia Agilent 4294A                                              | 31 |

|    | 2.6. | Electrómetro Programable Keithley 6517A                                             | 32 |

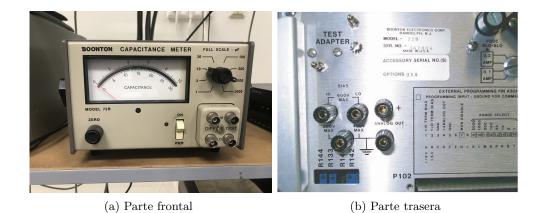

|    | 2.7. | Capacímetro Boonton 72B                                                             | 33 |

|    | 2.8. | Amplificador Lock-In EG&G 5210                                                      | 34 |

#### ÍNDICE GENERAL

| 3.        | Mue            | estras Estudiadas                                                                          | 35 |

|-----------|----------------|--------------------------------------------------------------------------------------------|----|

|           | 3.1.           | Creación de las muestras estudiadas                                                        | 35 |

|           |                | 3.1.1. Técnica ALD (Atomic Layer Deposition)                                               | 35 |

|           |                | 3.1.2. Magnetron sputtering                                                                | 38 |

|           | 3.2.           | Máscara CNM733                                                                             | 39 |

|           |                | 3.2.1. Descripción de las máscaras                                                         | 39 |

|           | 3.3.           | Muestras MIS                                                                               | 40 |

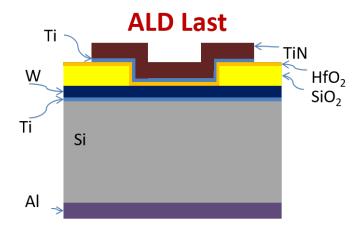

|           | 3.4.           | Muestras MIM                                                                               | 42 |

| 4.        | Téc            | nicas de Caracterización                                                                   | 45 |

|           | 4.1.           | Caracterización de dieléctricos e $interfaces$                                             | 45 |

|           | 4.2.           | Estudio de mecanismos de conducción                                                        | 46 |

|           |                | 4.2.1. Técnica I-V                                                                         | 46 |

|           | 4.3.           | Caracterización eléctrica inicial                                                          | 52 |

|           |                | 4.3.1. Medidas de Capacidad – Tensión (C-V) $\ \ldots \ \ldots \ \ldots \ \ldots \ \ldots$ | 52 |

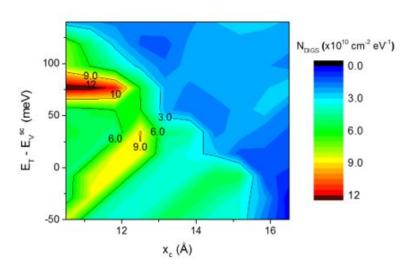

|           | 4.4.           | Determinación de estados superficiales                                                     | 57 |

|           |                | 4.4.1. Single-Shot DLTS (Deep Level Transient Spectroscopy)                                | 57 |

|           | 4.5.           | Defectos en el aislante                                                                    | 59 |

|           |                | 4.5.1. Transitorios de Conductancia (GTT)                                                  | 59 |

|           |                | 4.5.2. Transitorios de Banda Plana $(V_{fb}-t)$                                            | 62 |

|           | 4.6.           | Caracterización de estructuras memresistivas                                               | 65 |

|           |                | 4.6.1. Medidas I-V                                                                         | 65 |

|           |                | 4.6.2. Medidas GC-V                                                                        | 66 |

| <b>5.</b> | Res            | ultados y discusión                                                                        | 69 |

|           | 5.1.           | Caracterización muestras multicapa con $Al_3O_2$ y $HfO_2$ con sustrato tipo $n$           | 69 |

|           | 5.2.           | Resultados obtenidos con muestras MIM                                                      | 74 |

|           |                | 5.2.1. Caracterización I-V                                                                 | 74 |

|           |                | 5.2.2. Caracterización GC-V                                                                | 79 |

| II        | I C            | fonclusiones                                                                               | 83 |

| c         | Con            | aclusiones y Líneas Futuras                                                                | 85 |

| υ.        |                | •                                                                                          | 85 |

|           |                | Objetivos Cumplidos                                                                        | 86 |

|           |                | Conclusiones                                                                               | 86 |

|           |                | Líneas Futuras                                                                             |    |

|           | 0.4.           | Lineas rutulas                                                                             | 86 |

| IV        | <b>Т</b> А     | péndices y Bibliografía                                                                    | 89 |

| Α.        | $\mathbf{Pub}$ | olicaciones como coautor                                                                   | 91 |

Bibliografía 93

# Índice de figuras

| 1.1. | Relaciones entre magnitudes de un circuito eléctrico [3]                             | 5  |

|------|--------------------------------------------------------------------------------------|----|

| 1.2. | Estructura esquemática de la celda ReRAM                                             | 12 |

| 1.3. | Posibles combinaciones de curvas I-V de Set y Reset [8]                              | 13 |

| 1.4. | Estructura ReRAM y estados de SET y RESET [11]                                       | 14 |

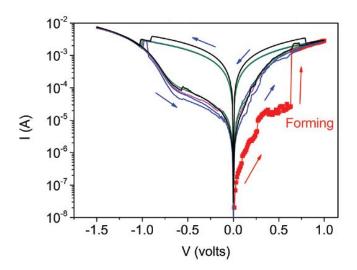

| 1.5. | Forming y primeros ciclos de una muestra MIM formada por $Pt/Ta_2O_5-TiO_2-$         |    |

|      | $Ta_2O_5/RuO_x$ [13]                                                                 | 15 |

| 1.6. | Operación de las celdas ECM [5]                                                      | 16 |

| 1.7. | Operación de las celdas VCM [5]                                                      | 18 |

| 1.8. | Operación de las celdas TCM [5]                                                      | 20 |

| 2.1. | Analizador de semiconductores Keitley 4200-SCS                                       | 26 |

| 2.2. | Analizador de parámetros en continua de semiconductores HP 4155B                     | 28 |

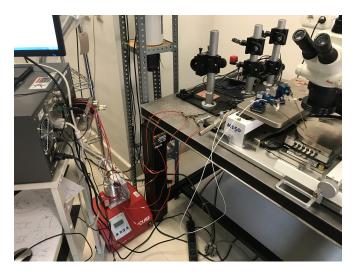

| 2.3. | Criostato usado para la realización de los diferentas experimentos                   | 29 |

| 2.4. | Esquema del criostato de nitrógeno líquido [17]                                      | 30 |

| 2.5. | Controlador de temperatura Oxford Instruments ITC503                                 | 30 |

| 2.6. | Equipo analizador de impedancia Agilent 4294A                                        | 32 |

| 2.7. | Electrómetro Programable Keithley 6517A                                              | 33 |

| 2.8. | Parte exterior del capacímetro Boonton 72B                                           | 33 |

| 2.9. | Equipo Amplificador Lock-In EG&G 5210                                                | 34 |

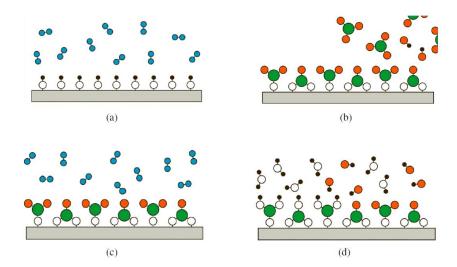

| 3.1. | Ciclo de ALD de $Al_2O_3$                                                            | 37 |

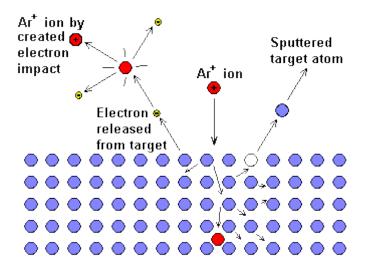

| 3.2. | Extracción de átomos del blanco mediante $sputtering$ [4]                            | 38 |

| 3.3. | Deposición de películas mediante sputtering [4]                                      | 39 |

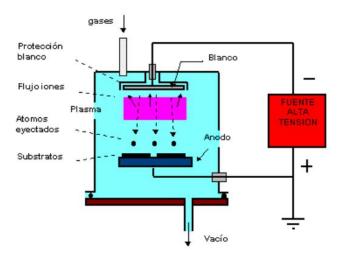

| 3.4. | Vista general de los chips                                                           | 40 |

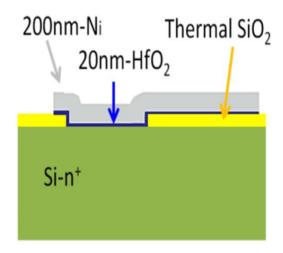

| 3.5. | Estructura muestra 8343-1                                                            | 41 |

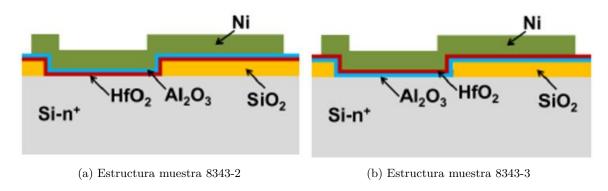

| 3.6. | Estructuras muestras 8343 bicapa                                                     | 41 |

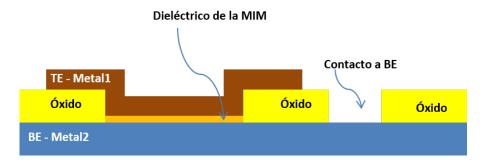

| 3.7. | Esquema fabricación estructuras MIM robustas                                         | 42 |

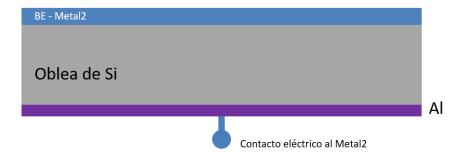

| 3.8. | Conexión BE estructuras MIM robustas                                                 | 42 |

| 3.9. | Conexión BE estructuras MIM robustas                                                 | 43 |

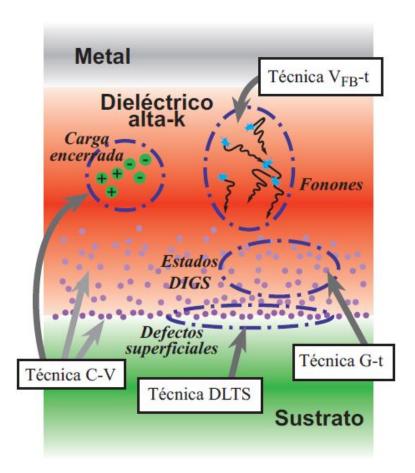

| 4.1. | Esquema cualitativo de las técnicas de caracterización usadas por el grupo GCME [23] | 46 |

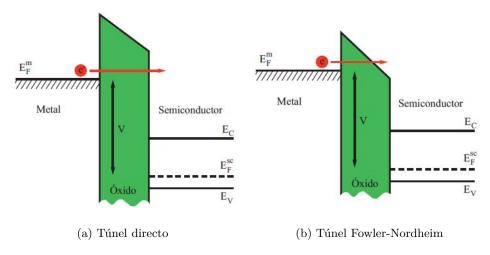

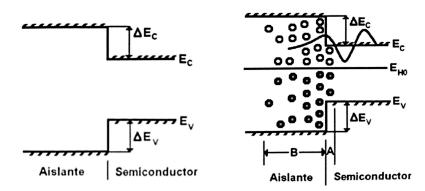

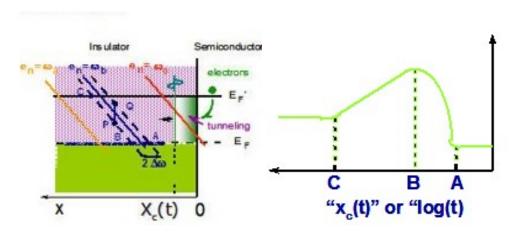

| 4.2. | Mecanismos de conducción túnel en una estructura MIS [23]                            | 48 |

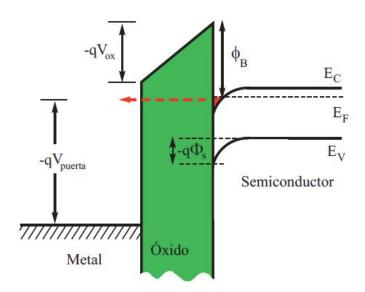

| 4.3.  | Parámetros del diagrama de bandas de energía en una estructura MIS para el                                               |    |

|-------|--------------------------------------------------------------------------------------------------------------------------|----|

|       | cálculo de la corriente túnel [23]                                                                                       | 49 |

| 4.4.  | Emisión Schottky en una estructura MIS [23]                                                                              | 50 |

| 4.5.  | Explicación cualitativa del mecanismo de conducción de Poole-Frenkel $[23]$                                              | 51 |

| 4.6.  | Distribución unidimensional del potencial en el caso del transporte iónico $\left[23\right]$                             | 51 |

| 4.7.  | Ejemplo de un ajuste para la conducción por mecanismo de túnel Fowler-Nordheim                                           | 52 |

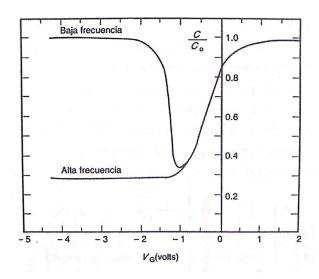

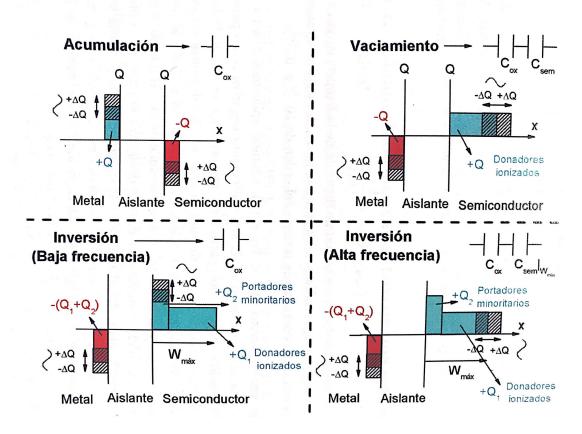

| 4.8.  | Curva C-V de una estructura n-MIS [4] $\dots \dots \dots \dots \dots \dots$                                              | 53 |

| 4.9.  | Cargas en una estructura MIS para acumulación, vaciamiento e inversión $[4]$                                             | 54 |

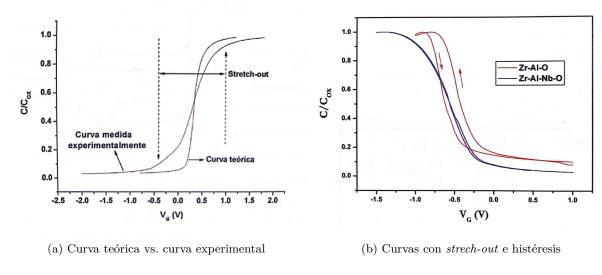

| 4.10. | . Curvas C-V [4]                                                                                                         | 55 |

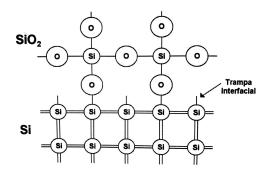

| 4.11. | . Enlaces incompletos en una interface $SiO_2/Si$ [4]                                                                    | 55 |

| 4.12. | . Densidad de estados superficiales [24]                                                                                 | 56 |

| 4.13. | . Modelo DIGS para los estados de interface [4]                                                                          | 56 |

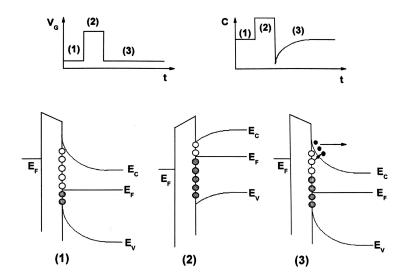

| 4.14. | . Secuencia de polarización de la muestra y transitorio de capacidad resultante [4]                                      | 57 |

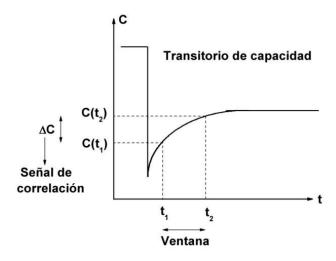

| 4.15. | . Concepto de ventana y de señal de correlación de un transitorio de capacidad                                           | 58 |

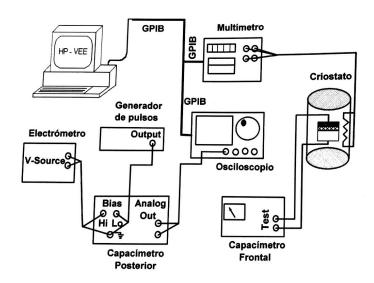

| 4.16. | . Montaje de la técnica DLTS [4]                                                                                         | 59 |

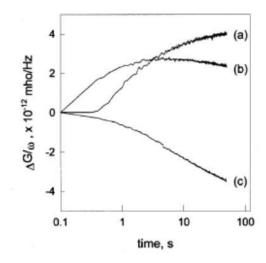

| 4.17. | . Transitorios de capacidad en una estructura MIS a diferentes frecuencias. a) 37                                        |    |

|       | Hz, b) 71 Hz, c) 123 Hz [4]                                                                                              | 60 |

| 4.18. | . Captura de portadores por los estados DIGS en un transitorio de conductancia y                                         |    |

|       | transitorio que produce $[4]$                                                                                            | 61 |

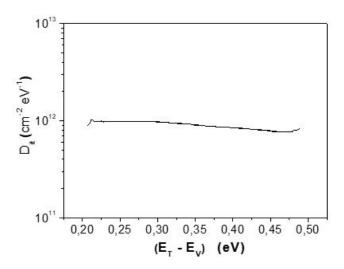

| 4.19. | . Ejemplo de los resultados obtenidos con esta técnica [24]                                                              | 62 |

| 4.20. | . Esquema del montaje de la técnica GTT [4]                                                                              | 62 |

| 4.21. | . Ejemplo cualitativo de la existencia de un transitorio de tensión de banda plana                                       |    |

|       | $[23] \dots \dots$ | 64 |

| 4.22. | . Esquema del montaje de la técnica de transitorios de banda plana                                                       | 64 |

| 4.23. | . Conexión de las mesa de puntas con el equipo Keithley para medidas I-V                                                 | 66 |

| 4.24. | . Conexión de las mesa de puntas con el equipo Keithley para medidas C-V y G-V                                           | 67 |

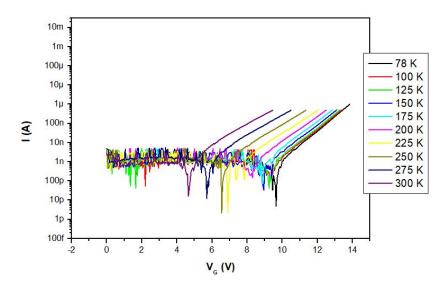

| 5.1.  | Medidas I-V obtenidas para la muestra MIS de 10 nm de $Al_3O_2$ y 10 nm de $HfO_2$                                       | 70 |

| 5.2.  | Ajuste al modelo de conducción de Poole-Frenkel a varias temperaturas de la                                              |    |

|       | muestra de de 10 nm de $Al_3O_2$ y 10 nm de $HfO_2$                                                                      | 70 |

| 5.3.  |                                                                                                                          |    |

|       | y $HfO_2$                                                                                                                | 71 |

| 5.4.  | Perfiles DLTS de todas las muestras de $Al_3O_2$ y $HfO_2$                                                               | 71 |

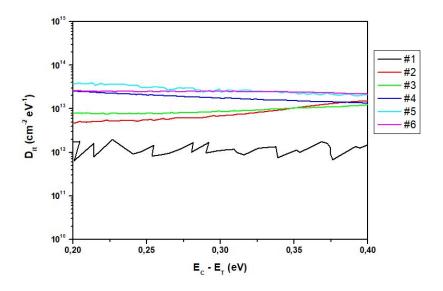

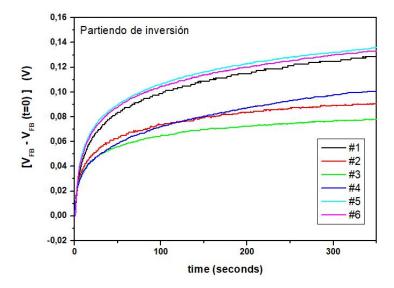

| 5.5.  | Transitorios de banda plana de todas las muestras de $Al_3O_2$ y $HfO_2$                                                 | 72 |

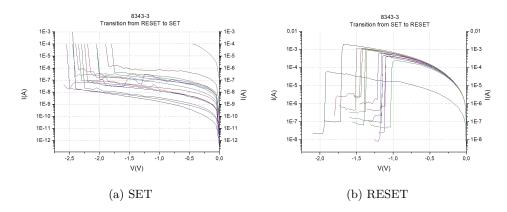

| 5.6.  | SET y RESET de la muestra bicapa de 10 nm de $HfO_2$ y 10 nm de $Al_3O_2$                                                | 73 |

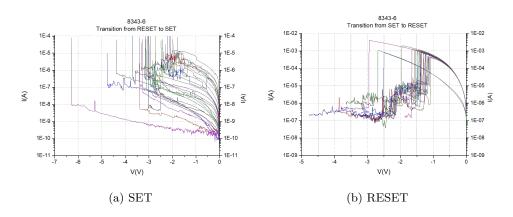

| 5.7.  | SET y RESET de la muestra pentacapa                                                                                      | 73 |

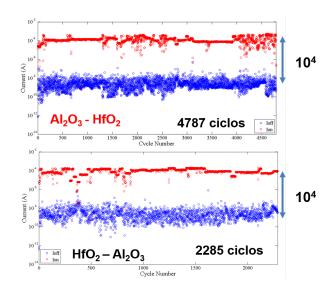

| 5.8.  | Pruebas de robustez de las muestras bicapa de $Al_3O_2$ y $HfO_2$ [25]                                                   | 73 |

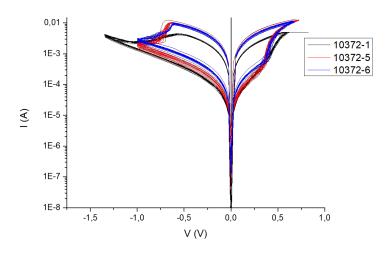

| 5.9.  | Ciclos marco de las muestras MIM                                                                                         | 74 |

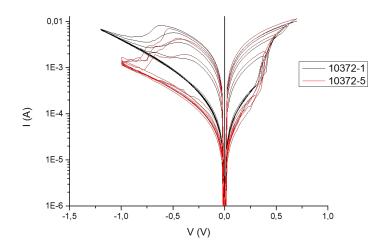

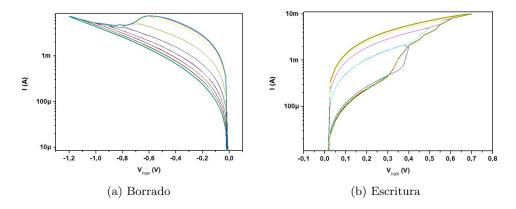

| 5.10. | . Escritura parcial para las muestras de 10 nm de $HfO_2$ y de 2 nm de $Al_3O_2$ y 5                                     |    |

|       | de $HfO_2$                                                                                                               | 75 |

| 5.11. Borrado parcial para las muestras de 10 nm de $HfO_2$ y de 2 nm de $Al_3O_2$ y 5 de    |    |

|----------------------------------------------------------------------------------------------|----|

| $HfO_2$                                                                                      | 75 |

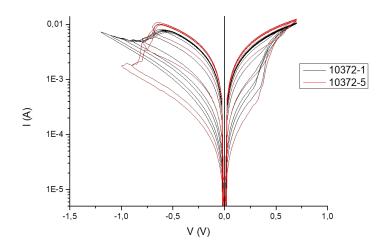

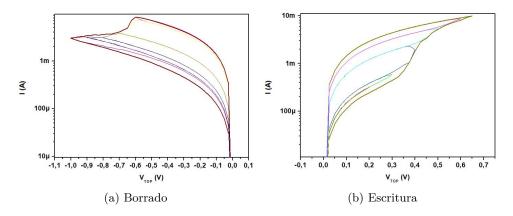

| 5.12. Escritura y borrado acumulados para la muestra de 10 nm de $HfO_2$                     | 76 |

| 5.13. Escritura y borrado acumulados para la muestra de 10 nm de $HfO_2$ y 2 nm de           |    |

| $Al_2O_3$                                                                                    | 76 |

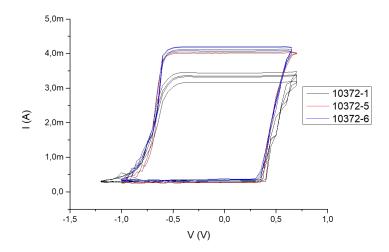

| 5.14. Histerones de corriente para las muestras MIM estudiadas                               | 77 |

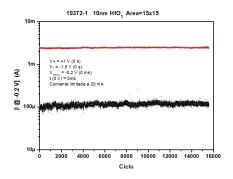

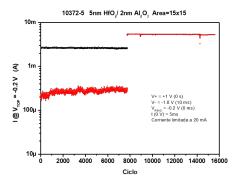

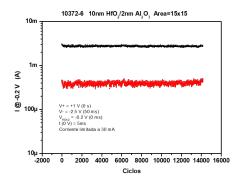

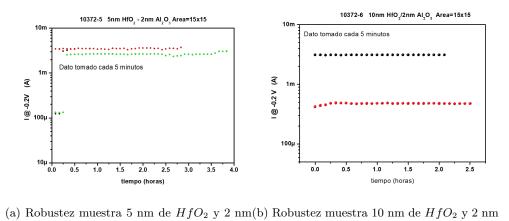

| 5.15. Robustez de las muestras MIM estudiadas medidas cada 5 ms                              | 78 |

| 5.16. Robustez de las muestras MIM con óxido de aluminio estudiadas medidas cada $5$         |    |

| minutos                                                                                      | 79 |

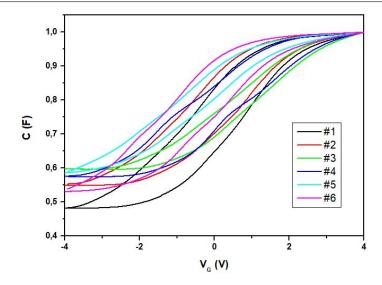

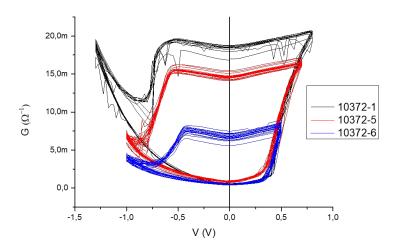

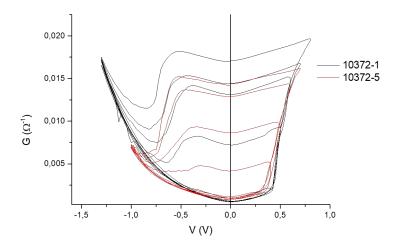

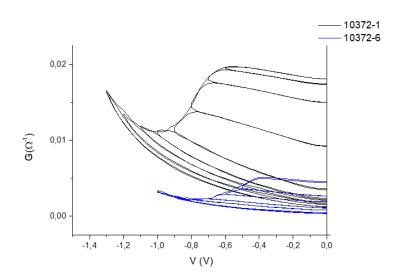

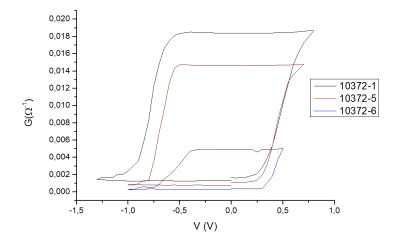

| $5.17.$ Curvas de conductancia para las muestras MIM estudiadas $\ \ldots \ \ldots \ \ldots$ | 80 |

| 5.18. Lazos de escritura parcial de conductancia                                             | 80 |

| 5.19. Borrado acumulado de la conductancia                                                   | 81 |

| 5.20. Histerones de conductancia de las muestras MIM                                         | 81 |

# Índice de tablas

| 1.1. | Comparación entre memorias RAM convencionales y emergentes [8] ( F es el |    |

|------|--------------------------------------------------------------------------|----|

|      | tamaño característico mínimo)                                            | 11 |

| 2.1. | Rangos de fuentes y medidas de la unidad 4200-SMU                        | 27 |

| 4.1. | Mecanismos de conducción habituales en estructuras MIS [23]              | 47 |

# Parte I Introducción y Objetivos

## Capítulo 1

## Introducción

Los elementos que almacenan información sin la necesidad de una fuente de alimentación han representado un cambio de paradigma en la electrónica, ya que han permitido un cálculo y almacenamiento usando baja potencia. Además, si esa información abarcase un rango continuo de valores, el cálculo analógico puede reemplazar el actual digital. Tal concepto también es probable que esté en el origen del funcionamiento del cerebro humano y posiblemente de muchos otros mecanismos en los organismos vivos, de modo que dichos elementos del circuito puedan ayudarnos a comprender el comportamiento adaptativo y espontáneo, o incluso el aprendizaje.

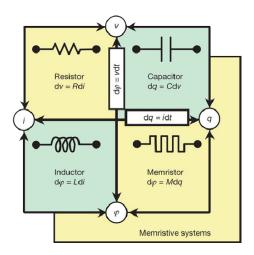

Uno de esos elementos es la resistencia con memoria (o memristor), fue postulada por Chua en 1971 al analizar las relaciones matemáticas entre pares de variables de circuito fundamentales, a saber: la corriente i, el voltaje v, la carga eléctrica q y el flujo magnético  $\varphi$ . [1]

De este modo, se pueden establecer las siguientes seis relaciones, de las que cinco ya son bien conocidas. Por un lado se tiene la que une carga eléctrica y corriente, ya que la segunda es causada por una variación de carga en el tiempo,  $q(t) = \int_{-\infty}^t i(\tau)d\tau$ , y la que relaciona flujo magnético y voltaje, donde el voltaje es causado por la variación de flujo,  $\varphi(t) = \int_{\infty}^t v(\tau)d\tau$ .

Por otro lado, las otras tres dan la definición de los tres elementos clásicos de los circuitos: el resistor (definido por la relación entre v e i), al pasar una corriente por él se obtiene una variación de tensión, el inductor (definido por la relación entre  $\varphi e i$ ), cuando una corriente lo atraviesa se crea un flujo magnético en el interior, y el capacitor (definido por la relación entre q y v), con una tensión de potencial entre sus terminales se almacena carga en su interior.

Solo faltaba una relación sin definir, la de carga y flujo. Por tanto, desde un punto de vista axiomático, Chua postuló la existencia de un cuarto elemento de circuto básico de dos terminales caracterizado por una curva de  $\varphi - q$ . Este dispositivo fue denominado memristor, debido a que su comportamiento es similar al de una resistencia no lineal con memoria. Está definida matemáticamente como la integral en el tiempo de la tensión, que no necesita tener una interpretación de flujo magnético.

Las relaciones anteriores se encuentran de forma gráfica en la figura 1.1.

Algunas de las propiedades teóricas que según Chua tendrían estos dispositivos son:

• El voltaje a través del memristor viene dado por la siguiente expresión:

$$v(t) = M(q(t))i(t) \tag{1.1}$$

Donde  $M(q) = d\varphi(q)/dq$ .

De forma similar la corriente que atraviesa se define como:

$$i(t) = W(\varphi(t))v(t) \tag{1.2}$$

Donde  $W(\varphi) = dq(\varphi)/d\varphi$ .

- El valor de la memresistencia M(q) (memductancia  $W(\varphi)$ ) en cualquier momento depende de la integral de tiempo de la corriente del memristor (voltaje) desde  $t = -\infty$  hasta  $t = t_0$ . Por lo tanto, mientras que el memristor se comporta como una resistencia ordinaria en un instante dado de tiempo, su resistencia (conductancia) depende de la historia pasada completa de la corriente del memristor (voltaje).

- Un memristor caracterizado por una curva  $\varphi q$  controlable por carga es pasivo si, y solo si, su resistencia incremental M(q) es no negativa; es decir, M(q) > 0. Como prueba la potencia instantánea disipada por un memristor es dada por  $p(t) = v(t)i(t) = M(q(t))[i(t)]^2$ . Por lo tanto, si la memresistencia M(q) > 0, entonces p(t) > 0 y el memristor es pasivo.

- Teorema del cierre: Un puerto único que contiene solo memristores es equivalente a un memristor.

- Teorema de existencia y unicidad: Cualquier red que solo contenga memristores con valores positivos incrementales tiene una y solo una solución. [2]

Como se puede ver en la figura 1.1, se puede extender la noción de sistemas memristivos a elementos capacitivos e inductivos, es decir, condensadores e inductores cuyas propiedades dependen del estado y la historia del sistema. Todos estos elementos muestran típicamente bucles histeréticos en las dos variables constitutivas que los definen: corriente-voltaje para el memristor, carga-voltaje para el memcapacitor y corriente-flujo para el meminductor. Estos elementos y su combinación en circuitos abren nuevas funcionalidades en electrónica y es probable que encuentren aplicaciones en dispositivos neuromórficos para simular el aprendizaje, la adaptación y el comportamiento espontáneo.

El proceso por el cual se va a encontrar una resistencia que va a poder tomar un valor diferente en el tiempo y dependiente de la historia del dispositivo se llama conmutación resistiva (resistive switching, RS). Este consiste en el cambio súbito y no volátil de la resistencia eléctrica de una capa de material dieléctrico, como consecuencia de la aplicación de una tensión o corriente eléctrica.

Aunque el fenómeno de conmutación resistiva (RS) se reportó en 1962, recientemente ha estado recibiendo un gran interés debido a su amplio potencial de aplicaciones, como memorias no volátiles, las denominadas memorias resistivas o más conocidas por su acrónimo RRAM o

Figura 1.1: Relaciones entre magnitudes de un circuito eléctrico [3]

ReRAM (Resistive Random Access Memory), computación neuromórfica y sinapsis artificiales, y procesamiento de señal analógica. [4]

Es un hecho que las actuales memoria FLASH están llegando a su límite de escalabilidad, debido en gran medida a las limitaciones tecnológicas del silicio. Por ello, se esta haciendo un gran esfuerzo en el sector de la microelectrónica para encontrar nuevos tipos de materialaes con los que fabricar memorias no volátiles que puedan tener una mayor escalabilidad además de mejores prestaciones. Las memorias RRAM, a las que se va a referir este trabajo, es una de las mejores propuestas para sustituir a la tecnología FLASH.

En estos momentos, las memorias FLASH presentan una serie de desventajas, como alto consumo de potencia en el funcionamiento, tiempos de escritura y borrado elevados, y el número de ciclos que pueden ser usadas. Por todas estos motivos es necesario conseguir una nueva tecnología que permita hacer sistemas cada vez más potentes, por tanto, es necesario ir hacia estas nuevas tecnologías de memorias no volátiles, tecnologías como RAMs ferroeléctricas (FRAM), RAMs de cambio de fase (PRAM) y las memorias en las que se basan este trabajo, las RRAM.

Algunas de las ventajas que hacen interesantes a las RRAM son: las altas velocidades de escritura y borrado (orden de nanosegundos) y una mayor robustez, soportando un mayor número de ciclos de escritura y borrado. Es interesante que son compatibles con la tecnología CMOS, predominante fundamentalmente en la industria; además, tienen la propiedad de ser no volátiles, manteniendo la información almacenada.

Una característica muy importante es que necesitará un voltaje de operación menor, por lo que la potencia consumida por el dispositivo será menor también. Se trata de una tecnología multinivel, por lo que en una celda de memoria es posible almacenar más de un bit, haciendo el estudio de estas memorias muy interesante para un gran número de aplicaciones.

En este trabajo caracterizaremos los fenómenos de conmutación resistiva en los que se basan este tipo de memorias y con ello intentaremos ver una posible viabilidad de estas.

#### 1.1. Motivación y objetivos

Como antes se ha comentado las memorias FLASH están empezando a poner límites al desarrollo tecnológico, por lo que se debe conseguir superar estas limitaciones para continuar progresando en sistemas cada vez con más potencia de cálculo y rápidos que además tengan un menor consumo de energía. Las estructuras que conforman las memorias resistivas pueden suponer un gran apoyo a este salto tecnológico con las características de las que se ha hablado anteriormente. Por una parte estas estructuras, que contarán con un mayor nivel de atomización que la tecnología existente, permitirán mayor densidad de elementos, además de una mayor velocidad; tendrán gran nivel de control sobre su estado que hará que no solo puedan ser incluidas en memorias ReRAM si no también en sistemas de redes neuronales que serán capaces de recrear mecanismos de organismos vivos, abriendo las puertas a un mundo de enormes posibilidades de desarrollo. Por todas estas razones se ha llevado a cabo este estudio de las estructuras que pueden formar estos sistemas con gran proyección de futuro.

#### 1.1.1. Objetivos

Para alcanzar las motivaciones anteriores se perseguirá el estudio y entendimiento de estas estructuras que presentan conmutación resistiva. En este trabajo, realizado en el seno del Grupo de Caracterización de Materiales y Dispositivos Electrónicos de la Universidad de Valladolid, esto se hará por medio de la caracterización eléctrica de muestras metal-aislante-metal (MIM, metal-insulator-metal) y metal-aislante-semiconductor (MIS, metal-insulator-semiconductor), tanto de la estructura completa como de la parte aislante en concreto.

También hay que comentar que este trabajo se enmarca dentro del Máster Universitario de Investigación en Tecnologías de la Información y la Comunicación de la ETS de Ingenieros de Telecomunicaciones de la Universidad de Valladolid, por lo que tendrá un marcado carácter de investigación y se centrará en aspectos como las técnicas desarrolladas y en el estudio e interpretación de los resultados obtenidos después de la investigación de las diferentes muestras. Este proyecto trata de seguir y ampliar el trabajo antes realizado en el Trabajo Fin de Grado que versaba sobre la misma temática.

Una vez establecido el objetivo final, llegaremos a él completando una serie de etapas intermedias:

- 1. Estudio de los fundamentos en los que se basan las memorias RRAM y la capa de material dieléctrico, así como resultados obtenidos hasta ahora para una mayor compresión de los fenómenos que subyacen esta tecnología para aplicar un protocolo para el estudio experimental de su comportamiento más eficiente.

- 2. Aprendizaje del manejo de los diferentes equipos utilizados para el estudio de las muestras con las que se han trabajado, así como un estudio de las principales técnicas con las que han sido obtenidos los resultados de las estructuras analizadas.

- 3. Caracterización eléctrica por medio de los equipos de medida presentes en el laboratorio y representación de los datos obtenidos.

4. Estudio de los resultados obtenidos para analizar el comportamiento de las muestras y ver así una posible viabilidad de las estructuras estudiadas.

#### 1.1.2. Estructura del trabajo

Este trabajo se encuentra estructurado en 5 capítulos y unas conclusiones:

- En el capítulo 1 se va a dar una visión global de las memorias RRAM y del fenómeno de RS. En la sección 1.2 se contextualizará este tipo de memorias, en las secciones 1.3 y 1.4 se darán las bases de las RRAM y del proceso de RS. Finalmente se hablará de los materiales de alta-k con los que se va a trabajar.

- En el capítulo 2 se mostrará el equipamiento utilizado para realizar las medidas con las que se caracterizarán las muestras.

- En el capítulo 3 se presentan las estructuras con las que se ha trabajado, así como los procesos de creación principales de las mismas.

- El capítulo 4 está dedicado a definir los fundamentos teóricos de las técnicas utilizadas para la caracterización eléctrica, tanto para el estudio del dieléctrico como del comportamiento de las estructuras.

- En el capítulo 5 se muestran los resultados obtenidos con las técnicas propuestas en el capítulo anterior para muestras MIS y MIM.

- El último capítulo está dedicado a las conclusiones extraídas de este trabajo y posibles líneas futuras de investigación.

#### 1.2. Tipos de memorias

Ahora se comentarán los principales tipos de tecnologías de memorias, así como sus características, para poder situar las memorias RRAM en un contexto tecnológico global.

Se puede hacer una primera división en 3 grandes grupos: los dispositivos de almacenamiento masivo (MSD, mass storage devices), los dispositivos de acceso no aleatorio y los dispositivos de acceso aleatorio (random access devices).

#### 1.2.1. Dispositivos de Almacenamiento Masivo

Las memorias de almacenamiento masivo tienen como principal característica el almacenamiento de gran cantidad de información a largo plazo. La forma en la que se va a acceder a las posiciones de memoria va a ser secuencial, por lo que los tiempos necesarios para acceder a ellas dependerán de la localización física de los datos relativos a la posición de las unidades de lectura/escritura.

Una de las clasificaciones más interesantes que podemos hacer para estos dispositivos es según su método de escritura:

- Media pregrabada: el proceso de almacenaje de información se hace durante el proceso de fabricación.

- De una sola escritura: puede ser grabada una vez por el usuario.

- Lectura/Escritura: puede ser grabada múltiples veces por el usuario. [5]

#### 1.2.2. Memorias de Acceso no Aleatorio

#### Memorias de Acceso Secuencial

La dirección en este tipo de memorias no es especificada. En el proceso de escritura, la información a grabar se introduce donde se hayan conectado los terminales de entrada, lo que marcará la posición de memoria y la lectura se producirá donde se conecten los terminales de salida, obteniendo así un tratamiento de la información más sencillo.

Se pueden distinguir principalmente 4 clases:

- Registros de desplazamiento: una orden de lectura o escritura desplaza la información una posición en la memoria. Pueden ser estáticos si pueden anularse los pulsos de despazamiento o dinámicos si no pueden ser anulados.

- Memorias cola: la información escrita en primer lugar sale antes que la información introducida en ciclos posteriores, First In-First Out (FIFO).

- Memorias pila: en este caso la información que sale en primer lugar es la de la última operación de escritura realizada, Last In-First Out (LIFO).

- Memorias circulares: la información se desplaza de forma constante en la memoria si no se está ejecutando ninguna operación de entrada o salida de datos.[6]

#### Memorias Asociativas

O también llamadas *Content Addressable Memories* (CAM). Las memorias asociativas presentan una búsqueda de información durante la lectura algo diferente. En este caso no se indicará una posición de memoria y se pasará a leer su contenido, lo que se hace es pasar la información a la memoria y esta buscará si está contenida en alguna de sus posiciones. [6]

#### 1.2.3. Memorias de Acceso Aleatorio

En este tipo de memorias se va a poder acceder rápidamente a cualquier posición de memoria, esto es debido a que las celdas de almacenamiento se organizan en forma de matriz y se puede acceder en paralelo. Utilizan circuitos integrados basados en semiconductores para almacenar la información.

Las memorias basadas en semiconductor se pueden clasificar en función de cuantas veces pueden ser sobreescritas en: memorias de acceso aleatorio (random access memories, RAM) y memorias de solo lectura (read-only memories, ROM).

#### RAM

En este caso no hay límite en el número de ciclos de lectura y escritura. En un segundo nivel de clasificación se pueden diferenciar memorias RAM volátiles y no volátiles, según si son capaces de retener o no la información.

Las memorias RAM volátiles son aquellas que cuando la alimentación es retirada, se pierde la información que contiene. Dentro de las volátiles encontramos:

- SRAM (Static RAM): en esta tecnología los estados se diferencian empleando flip-flops. Tienen unos tiempos de escritura/borrado rápidos del orden de 0.3 ns/0.3 ns. Se suelen utilizar como memorias caché donde el tiempo de acceso es crítico. Cada celda de memoria está compuesta por 6 transistores, lo que hace que tengan un gran tamaño en comparación con el resto de tecnologías que se comentarán. Su principal ventaja es que es diferencial, por lo que se tiene tanto el dato como el dato complementado en la celda. El proceso de lectura puede ser destructivo porque el dato puede ser cambiado durante esta operación de forma no intencionada. [7]

- DRAM (Dinamic RAM): el estado que se tenga va a depender del nivel de carga que haya en una capacidad, por lo que se necesitará un refresco constante de la celda para que el dato no se pierda por corrientes de fuga del capacitor. Constan de un transistor por celda, lo que hace que tengan un tamaño mucho menor que las SRAM, la dificultad está en hacer un capacitor grande en capacidad y que ocupe el menor espacio posible. En este caso solo se cuenta con el dato y no con el dato complementado al haber un solo transistor. La lectura es destructiva, ya que, se moverá carga de la capacidad y por ello necesitaremos un amplificador sensor al no hacer una lectura completa para que el dato no sea destruido por una descarga profunda del capacitor . No obstante, esto no es demasiado problemático debido al refresco constante de la celda. Puede llegar a los 3 × 10¹6 ciclos de lectura/escritura. Son utilizadas como memorias principales donde la capacidad es vital para el almacenamiento y procesamiento temporal de la información. [7]

En las no volátiles se pueden encontrar varios tipos dependiendo del principio por el que se almacene la información, la mayoría de ellas necesitan todavía de una profunda investigación para poder desarrollar dispositivos funcionales que superen a los ya existentes. Suelen estar basadas en materiales electrónicos nuevos que no utilizan las tradicionales tecnologías de semiconductores. Las principales tecnologías que podemos distinguir son:

- Memorias ferroeléctricas (ferroelectric memories, FRAM): al aplicar un campo eléctrico suficientemente fuerte ( $E > E_c$ , siendo  $E_c$  el campo coercitivo) a un material ferroeléctrico, se produce un cambio en la polarización ferroeléctrica del material comportándose de forma histérica. Lo que se encontrará será un lazo de polarización frente al campo eléctrico con lo que se obtienen 2 estados diferenciados, base de las memorias FRAMs.

- Memorias de cambio de fase (phase-change memories, PRAM): están sustentados en ma-

teriales de cambio de fase, como los calcogenuros <sup>1</sup>, los cuales pueden variar la fase del material entre fase amorfa y cristalina. Este cambio de fase hace que cambie la resistencia así como la reflectividad. A diferencia del almacenamiento óptico, la temperatura a la que opera puede estar por encima de la temperatura ambiente.

- Memorias magnéticas (magnetic memories, MRAM): se piensa que pueden llegar a sustituir a memorias como las SRAM o las FLASH. Hay 2 tipos principales de memorias magnéticas: MRAMs de escritura de campo y MRAMs de transferencia de spin (STTMRAM). En las primeras, cada celda de memoria se escribe con un campo magnético alrededor de la línea de corriente. Las STTMRAMs se apoyan en la corriente polarizada de un spin.

- Memorias resistivas (resistance memories, RRAM): Las memorias resistivas incluyen todos los tipos de memorias que usan dos o más estados de resistencia distintivos como los números binarios '0' y '1'. Los materiales para RRAMs cubren todos los materiales que exhiben conmutación resistiva no volátil, donde la conmutación se hace mediante campos eléctricos, que no sean calcogenuros superiores de tipo de cambio de fase.

El conmutador resistivo en cada célula de memoria de un RRAM de tipo 1 transistor 1 resistencia (1T1R) consiste en una capa de conmutación, un electrodo superior (TE) y un electrodo inferior (BE) que encierran la capa intermedia que conmuta. Esta célula de conmutación que se comporta como un condensador se caracteriza por dos estados de resistencia distintivos: un estado de alta resistencia (high resistance state, HRS) y un estado de baja resistencia (low resistance state, LRS). Mediante la aplicación de una tensión y/o una corriente determinados a la célula, se puede lograr una conmutación reversible entre el HRS y el LRS. Una vez que el estado ha sido cambiado, la célula retiene el nivel de resistencia particular durante un largo tiempo.

La tabla 1.1 nos ofrece un resumen de la clasificación de las memorias de acceso aleatorio.

#### ROM

Para este tipo de memoria hay una limitación importante en los ciclos de lectura/escritura. Mediante el uso de máscaras durante el proceso de fabricación se podrá almacenar la información que se desee. Dependiendo si las memorias ROM pueden ser reprogramadas, se pueden encontrar:

- OTPROM (*one-time programmable* ROM): como su nombre indica es un tipo de ROM que no puede volver a ser programada.

- EPROM (*erasable programmble* ROM): en este caso la memoria si puede ser reprogramada de diferentes formas:

<sup>&</sup>lt;sup>1</sup>Los calcogenuros son unos compuestos los cuales tienen un anión formado por un elemento del Grupo 16 (Anfígeno) y un elemento metálico de carácter electropositivo. Los calcogenuros son derivados de sulfuros, seleniuros y teluros.

|                           | Memoria<br>volátil  |                      | Memoria<br>no volátil |                  | Memorias<br>no volátiles emergentes |                |                |                                      |

|---------------------------|---------------------|----------------------|-----------------------|------------------|-------------------------------------|----------------|----------------|--------------------------------------|

| Tipo                      | SRAM                | DRAM                 | NOR-FLASH             | NAND-FLASH       | MRAM                                | PRAM           | FRAM           | RRAM                                 |

| Elementos                 | 6T                  | 1T1C                 | 1T                    | 1T               | 1(2)T1R                             | 1T1R or        | 1T1C           | 1T1R or                              |

| de celda                  |                     |                      |                       |                  |                                     | 1D1R           |                | 1D1R                                 |

| Celda                     | Cerrojo             | Condensador          | Puerta flotante/      | Puerta flotante/ | Magnetoresistencia                  | Cambio         | Cambio de      | Cambio de resistencia                |

|                           |                     | de pila              | trampas de carga      | trampas de carga |                                     | de fase        | polarización   |                                      |

| Mínimo tamaño<br>de celda | $140\mathrm{F}^2$   | $6F^2$               | $10F^2$               | $5F^2$           | $20F^2$                             | $4.8(4)F^{2}$  | $22F^2$        | $4F^2$                               |

| Tiempo de                 | 0.3ns/              | <10ns/               | 1ms/                  | 1ms/             | 10ns/                               | 20ns/          | 10ns/          | 5ns/                                 |

| escritura/borrado         | $0.3 \mathrm{ns}$   | <10ns                | 10ms                  | 0.1ms            | 10ns                                | 50ns           | 10ns           | 5ns                                  |

| Robustez<br>(ciclos)      | $>3 \times 10^{16}$ | $>3 \times 10^{16}$  | $>10^{5}$             | $>10^{5}$        | $>3 \times 10^{16}$                 | $10^{8}$       | $10^{14}$      | $>10^{10}$                           |

| Aplicación                | Caché               | Memoria<br>principal | Almacenamiento        | Almacenamiento   | Almacenamiento                      | Almacenamiento | Almacenamiento | Almacenamiento/<br>Memoria principal |

Tabla 1.1: Comparación entre memorias RAM convencionales y emergentes [8] ( F es el tamaño característico mínimo)

- 1. EPROM (*Erasable Programmable* ROM): puede ser grabada un gran número de veces. Para el proceso de borrado es necesario exponer la memoria a rayos ultra-violeta, lo que conlleva que el tiempo de borrado sea importante (del orden de minutos).

- 2. EEPROM (*Electrically Erasable Programmable ROM*): el borrado en este caso se hace de forma eléctrica, aunque algo mas lento que en las memorias RAM, pudiendo llegar a hacerse 1000000 de veces. La celda de memoria la forman 2 transistores MOSFET. Para trabajar con este tipo de ROM son necesarias tensiones mayores.

- 3. FLASH: al igual que las memorias EEPROM su contenido puede ser borrado de forma eléctrica, no obstante, difieren en el hecho de que el borrado debe hacerse por bloques completos en vez de un valor concreto, como pasaba con las anteriores. Esto hace que memorias de una mayor capacidad puedan ser creadas. Cada celda de memoria esta compuesta por un transistor MOSFET (metal-oxide—semiconductor field-effect-transistor) con una puerta flotante adicional. El tiempo de operación de una memoria FLASH es mucho mas lenta que la de un DRAM (tiempos de escritura/borrado: 1 ms/0.1 ms). [9]

#### 1.3. Bases de las memorias RRAM

Ahora se sentarán las bases de las estructuras que conformarán las memorias RRAM. Primero se hablará de los tipos de RS según la polaridad, luego se dará una pequeña visión de la gran cantidad de materiales con los que fabricar los dispositivos y por último se comentarán los procesos que forman el RS.

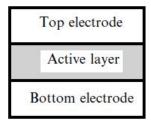

En la figura 1.2 se puede ver el esquema básico de la estructura principal de las celdas de la RRAM, el elemento donde se almacenará la información. La estructura es sencilla, compuesta por electrodos metálicos a ambos lados de una capa activa donde se producirá principalmente el fenómeno del cambio de resistencia del material que afectará al comportamiento de toda la celda. Como se ha mencionado anteriormente, el tamaño de celda es pequeño, del orden de  $4F^2$ , por lo que las celdas de las RRAMs pueden ser integradas en crossbar arrays con facilidad. Si

Figura 1.2: Estructura esquemática de la celda ReRAM

se desarrollase en arquitecturas en 3 dimensiones, el tamaño podría reducirse, obteniendo una relación de  $4F^2/n$ , siendo n el número de capas apiladas.

El principio de funcionamiento de las RRAM es el cambio de la resistencia del material entre un estado de alta resistividad y otro de baja o viceversa debido a un estrés eléctrico. Cuando la estructura presente una de alta resistividad se llamará a ese estado OFF, por el contrario si la resistencia de la muestra es sustancialmente menor ese estado se denomina ON. En términos lógicos el estado de ON se correponde con un "1" y el de OFF con un "0". Los cambios de HRS a LRS lo llamaremos SET o de escritura y para la transición contraria llamaremos a este proceso RESET o de borrado, los cuáles serán comentados más en profundidad más adelante.

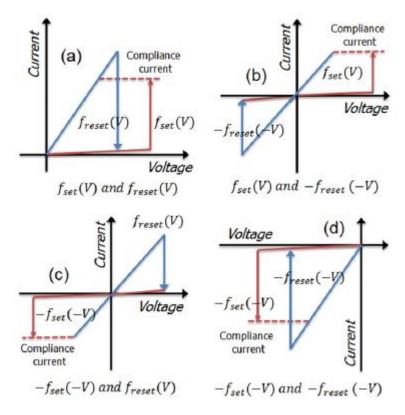

#### 1.3.1. Tipos de RS según su polaridad

Dependiendo de la polaridad a la que ocurren el SET y el RESET se puede hablar de 2 tipos de RS, unipolar y bipolar. En la primera, el paso de HRS a LRS y de LRS a HRS ocurrirá solamente en una polaridad, positiva o negativa, pudiendo manejarse únicamente la amplitud que introducimos a la muestra. En el segundo caso las transiciones entre estados de ON a OFF y viceversa ocurren a polaridades opuestas de voltaje, por lo que se tendrá control sobre 2 variables: la amplitud del voltaje introducido y su polaridad.

Estos 2 efectos se pueden apreciar en la figura 1.3 donde estan definidos los voltajes umbrales donde se producen los estados de SET  $(f_{set})$  y de RESET  $(f_{reset})$ .

En ambos casos, obtendremos al menos 2 estados bien diferenciados en la memoria. Como se ha comentado los 2 estados se obtienen por un cambio en el estado de los materiales de la estructura, prioritariamente en la capa activa formada por el dieléctrico, al aplicar un estrés eléctrico habrá un cambio en esta capa debido a la creación o ruptura de un filamento conductor que une los 2 electrodos que causará un estado de baja o alta resistividad en la estructurra respectivamente. Este filamento se romperá de una forma intencionada, ya que con el tiempo no debería desparecer, por tanto hablamos de que el proceso es no volátil.

Existe un caso especial en el que el SET o el RESET no se producen siempre a una misma polaridad, si no que estos procesos se pueden producir en cualquier polaridad, este tipo de conmutación resistiva es denominada apolar.

Figura 1.3: Posibles combinaciones de curvas I-V de Set y Reset [8]

#### 1.3.2. Materiales usados en RRAMs

La conmutación resistiva ha sido observada en materiales inorgánicos, orgánicos e híbridos orgánicos e inorgánicos. En los materiales inorgánicos el RS esta relacionado con la formación y la ruptura de filamentos conductores que proceden de la migración iónica. Para los materiales orgánicos suele estar debida a la transferencia de carga inducida por campo eléctrico. Como material activo se usarán dos materiales diferentes, uno donador de electrones y otro aceptador, o un material que tenga una parte donadora y otra aceptadora. Con la aplicación de un campo eléctrico externo se puede inducir la transferencia de electrones entre donante y aceptador. Las cargas quedarán atrapadas en esa capa activa de espesor de nanometros haciendo de esa forma que se convierta el material en un interruptor que se pueda manejar externamente. Cuando la película activa está hecha de materiales orgánicos / poliméricos y sus compuestos, puede tener una alta flexibilidad mecánica. Los dispositivos electrónicos flexibles tienen una aplicación importante en algunas áreas, tal como electrónica plegable. Además de la aplicación de memoria, la combinación de RRAMs con otros dispositivos electrónicos puede conducir a nuevas funciones. Por ejemplo, una RRAM flexible combinado con un diodo emisor de luz en serie puede usarse como papeles electrónicos. [10]

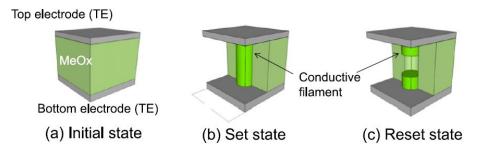

La figura 1.4 muestra la estructura esquemática y el funcionamiento de un dispositivo RRAM. El dispositivo consiste en una capa aislante, normalmente un óxido metálico (MeOx), interpuesto entre un electrodo superior (TE) y un electrodo inferior (BE), ambos generalmente constituidos por capas o pilas metálicas (figura 1.4 (a)).

Figura 1.4: Estructura ReRAM y estados de SET y RESET [11]

Con ello tendríamos una estructura metal-aislante-metal (MIM). Otras veces la estructura está conformada por un material semiconductor, como el silicio, obteniendo una estructura de metal-aislante-semiconductor (MIS). En este caso es importante hacer un estudio de la interface dieléctrico-semiconductor para comprobar el correcto funcionamiento. La mayoría de los materiales van a presentar un comportamiento de conmutación resistiva filamentar, es decir, el elemento formado en el material que hace que cambie la resistencia del material es un filamento conductor entre los 2 electrodos. No obstante, no es la única. También podemos encontrar que este RS puede ser de tipo no filamentar, en este caso encontraremos una estructura diferente en el estado de LRS, pudiendo observar por ejemplo que la unión entre los 2 electrodos se produce mediante un volúmen, sin embargo, la diferencia en los mecanismos de formación de la unión para RS filamentar o no filamentar todavía no han sido probados.

#### 1.3.3. Forming, SET Y RESET

Esta sección se centra en definir los diferentes procesos de forming, de set y de reset presentes en el fenómeno de conmutación resistiva.

- El forming es el proceso por el que se genera por primera vez el filamento que conecta los electrodos superior e inferior del dispositivo. Este proceso se le suele llamar electroforming, ya que el forming se hará por medio de la aplicación de un voltaje o corriente en la celda RRAM. Es el proceso con el que empieza la estructura a tener este comportamiento de conmutación, por lo que se realiza cuando la muestra esta "virgen" y todavía no experimenta RS. Se trata de una ruptura del dieléctrico reversible, por lo que el estrés que debe de ser aplicado será mayor esta primera vez que para los otros 2 procesos. Al crearse el filamento por primera vez, la polaridad del forming suele ser la misma que la del SET. Este proceso es irreversible, una vez hecho la muestra ya no puede volver al estado en el que no presentaba RS.

- En el SET se crea el filamento o los filamentos de conductividad elevada que une los electrodos superior e inferior y hace que la estructura cambie de alta resistividad a una baja. Esta unión puede ser de 1 dimensión o de 2 dimensiones, según sea filamentar o en área. Para que se produzca este proceso es necesario que la celda de memoria esté en un estado de baja conductividad o HRS, es decir, que el filamento conductor entre los

Figura 1.5: Forming y primeros ciclos de una muestra MIM formada por $Pt/Ta_2O_5 - TiO_2 - Ta_2O_5/RuO_x$  [13]

electrodos no exista totalmente. En ese momento se aplicará una tensión concreta con lo que la unión se creará. Este filamento no desparecerá con el tiempo, con lo que tenemos un estado estable y no volátil. Esta operación puede ser revertida.

■ El proceso de RESET es el contrario al de SET. En este caso la celda pasa de desde un estado de baja resistividad a uno de alta por medio de la destrucción, total o parcial, de la unión entre los electrodos previamente generada en el proceso de forming o de SET. Este estado también es no volátil y para pasar de nuevo al estado de SET un voltaje y/o corriente tendrán que ser introducidos. [12]

Estos procesos se muestran en el ejemplo de la figura 1.5, realizados en una muestra MIM a temperatura ambiente.

#### 1.4. Procesos de conmutación resistiva

Hay varios procesos que sustentarán la conmutación resistiva, estos dependerán de los materiales que compongan la estructura tanto en los electrodos como en la capa dieléctrica. A pesar de que se puede estimar el comportamiento físico de ciertas muestras con algunos materiales en concreto, todavía se desconoce exactamente qué procesos están vinculados a qué materiales. También hay que tener en cuenta que es posible que se dé más de un proceso al mismo tiempo para formar o diluir el filamento conductor que dará lugar al cambio de estado. Los tipos de memorias más habituales son:

#### 1.4.1. Memoria de metalización electroquímica

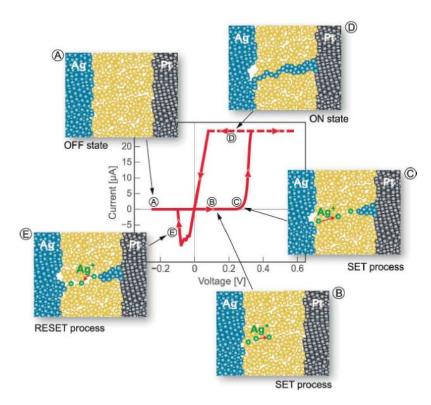

Tambien llamadas de Puente Conductor o celdas de metalización programable. El modo básico de funcionamiento puede ser observado en la figura 1.6, donde se puede apreciar una

Figura 1.6: Operación de las celdas ECM [5]

gráfica I-V. La celda consiste en un electrodo hecho a partir de un electrodo metálico activo electroquímicamente, como Ag o Cu, el otro electrodo sería también metálico pero en este caso inerte, como Pt, Ir, Au o W, entre medias de ambos electrodos habría una fina capa conductora de iones del metal activo. Esta capa puede ser un electrolito sólido que contiene cationes del metal o como aislante, dopado con cationes del metal. Como ya se ha hablado anteriormente, hay una larga lista de materiales en los cuales se ha encontrado este tipo de memoria si se depositan en una capa mediante "sputtering", ALD (Atomic Layer Deposition) o CSD (Chemical Solution Deposition). [5, 12]

En el HRS de la celda no hay eletrodeposición del metal activo en el inerte (A), esta en estado de OFF. Durante el proceso de SET (B - C), una tensión positiva es aplicada al electrodo activo, en este caso el compuesto por Ag y este se oxida en iones  $Ag^+$  que derivarán hacia el electrodo inerte debido al campo eléctrico. Siendo el electrodo inerte el cátodo, se produce una reducción electroquímica y una electrocristalización de Ag en la superficie del electrodo inerte. Este proceso tiene como resultado la creación de un filamento de Ag que crece hacia el electrodo activo hasta que se produzca un contacto eléctrico con el otro electrodo, lo que nos dará el estado de ON (D). Para resetear la muestra el voltaje aplicado será de una polaridad opuesta, lo que hace que se disuelva el filamento anteriormente creado (E), llevando de nuevo la celda al estado de OFF (A).

#### Forming y SET

El proceso de SET sigue estos pasos consecutivos:

1. Oxidación del ánodo y disolución del metal de acuerdo con la reacción:

$$M \to M^{z+} + ze^- \tag{1.3}$$

donde  $M^{z+}$  representa los cationes del metal en la capa de electrolito sólida.

- 2. Se produce una migración de los cationes  $M^{z+}$  a través de la capa de electrolito sólida debido a la acción de un campo eléctrico intenso, la migración de estos cationes puede verse facilitada por diversos defectos en la estructura de la celda.

- 3. Reducción y electrocristalización del metal activo en la superficie del electrodo inerte siguiendo la reacción de deposición catódica:

$$M^{z+} + ze^- \to M \tag{1.4}$$

4. El proceso de electrocristalización lleva a la formación de un filamento conductor que crece en la dirección del electrodo activo, hasta que se forme un contacto eléctrico con una resistencia  $R_{ON}$  limitado por la corriente límite ( $I_{cc}$  o  $I_{compliance}$ ).

Generalmente el contacto eléctrico viene dado por un solo filamento conductor, aunque en un primer momento se vayan creando varios filamentos, cuando el primer filamento haga contacto el voltaje caerá y se alcanzará la corriente límite. El diámetro del filamento y lo fuerte que sea el contacto eléctrico puede ser controlado por el nivel de  $I_{cc}$  que sea elegido. Esto hace que este tipo de celdas presente la posibilidad de una programación multinivel, ya que existe la posibilidad de elegir la  $R_{ON}$ , que viene dado por el estado del filamento.

#### RESET

El proceso de RESET depende del SET establecido anteriormente. Se pueden distinguir los siguientes pasos dentro del proceso de RESET:

- 1. La conducción electrónica del filamento metálico dará lugar a que se produzca el efecto Joule siendo la parte con más temperatura la más estrecha del filamento, que será la más cercana al electrodo activo. En la superficie del filamento en contacto con el electrolito que le rodea se producen procesos de disolución y redeposición electroquímica, que llevan a la disolución del filamento. Este proceso tendrá más fuerza en la parte más caliente del filamento.

- 2. Una vez que el filamento rompe, el proceso electroquímico empieza a dominar el mecanismo de RESET, disolviendo la parte de filamento restante en contacto con el electrodo inerte. Mientras el gap sea pequeño puede haber corrientes de túnel.

Figura 1.7: Operación de las celdas VCM [5]

3. En una última fase, se produce una completa disolución del filamento restante y del resto de filamentos que se hayan podido formar durante el proceso de SET. De esta forma volvemos a llegar al estdo de OFF. [5]

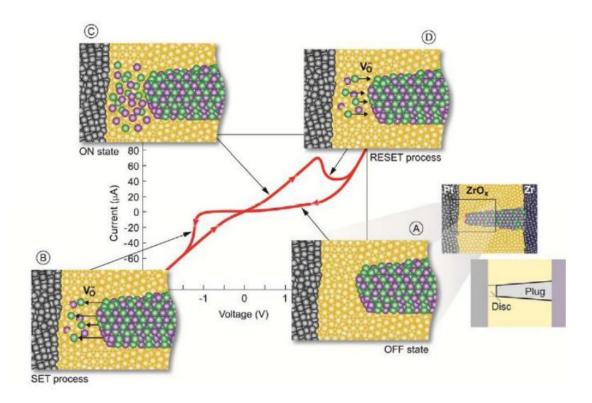

#### 1.4.2. Memoria de cambio de valencia

Para este tipo de celdas de memoria, la estructura MIM esta compuesta por una interfaz activa, electrodo activo, donde el proceso de conmutación tiene lugar, una capa intermedia de conducción iónico-electrónica y un electrodo ohmico al otro lado. En este caso nos centraremos en una capa intermedia de óxido conductor tipo n, aunque puede haber variantes en este material. En la figura 1.7 se muestra una curva I-V típica.

En el estado de OFF, el filamento esta formado por un óxido conductor tipo n y una barrera de potencial. Cuando aplicamos una tensión de SET negativa, las vacantes de oxígeno son atraidas desde el óxido del filamento hacia la barrera, lo que hace que la longitud y la anchura de la barrera decrementen debido a un proceso local de reducción, que lleva a la celda a un estado de ON. Para el proceso de RESET se aplica un voltaje positivo al electrodo activo, lo que hace que las vacantes de oxígeno sean repelidas produciendo una reoxidación local que vuelve a hacer que la celda este en OFF.

#### **Forming**

La tensión necesaria para hacer el forming es mayor que con la que luego haremos los SETs. Dependiendo del metal que componga el electrodo, el forming será posible para ambas polaridades. El proceso conlleva la oxidación del metal. Típicamente no es uniforme y lleva a la formación de filamentos conductores tipo n. Durante el forming habrá unas altas temperaturas locales debido a las corrientes que se concentran en esa zona y a los altos voltajes que se dan. Esto puede acelerar el proceso de forming dando lugar a cambios en la morfología de la celda. El voltaje de forming necesario es menor cuanto más fina sea la capa de óxido.

#### SET y RESET

El proceso redox que tiene lugar durante el proceso de forming hace que haya una conexión tipo n que será un filamento deficiente en oxígeno. Los procesos de SET y RESET tendrán lugar en la parte de la barrera de potencial. El tamaño del filamento quedará determinado por las condiciones de forming y tendrá influencia en los parámetros eléctricos de los procesos de SET y RESET. En el estado de OFF la resistencia de la celda será en su mayor parte la que tiene esa barrera de potencial y en menor medida la parte del filamento que sigue formado. En este estado de OFF hay una barrera de energía significativa debido a que esta zona está oxidada.

Durante el SET los iones de oxígeno son apartados de la zona de barrera de potencial. Esta extracción lleva a la reducción de esta zona, lo que resulta en un decremento de la anchura de la barrera. En el estado de ON como consecuencia hay un incremento de la conducción iónica. En ON la resistencia estará determinada por la resistencia de la barrera de potencial, ahora reducida, y la resistencia del filamento. Esta última no será muy grande debido a que el óxido conductor representará un semiconductor.

En el proceso de RESET, los iones de oxígeno son atraídos a la zona de la barrera, llevando la celda al estado de OFF de nuevo. [5, 12]

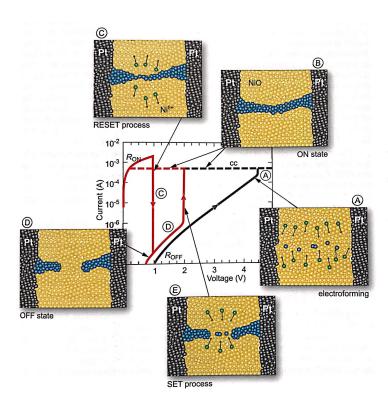

#### 1.4.3. Memoria termoquímica

En las celdas de memoria termoquímica los procesos termoquímicos tienen más fuerza que los electroquímicos y por ello la conmutación suele tener un carácter unipolar. Durate la conmutación, los gradientes de temperatura que se producen dan lugar a variaciones locales estequiométricas y reacciones redox y esto hace que haya un cambio en la conductividad electrónica. La conmutación en este tipo de memorias suelen ser observadas en óxidos metálicos que muestran una gran resistividad en el estado más oxidado y menor en el estado reducido, como por ejemplo:  $ZrO_x, TiO_x, Fe_2O_3$  o  $Al_2O_3$ . En este caso el metal usado para el electrodo superior puede ser distinto, a diferencia de lo que pasaba en las memorias de cambio de valencia que era requerida una asimetría.

Podemos ver una curva I-V característica de estas memorias en la figura 1.8.

Durante el forming hay un aumento de corriente debido a una ruptura termoeléctrica y a la creación de un filamento conductor en la celda. El proceso esta limitado por  $I_{cc}$ , controlando así la resistencia en ON. Cuando ocurre el ciclo de RESET la corriente límite es superada por un

Figura 1.8: Operación de las celdas TCM [5]

pico de corriente que disuelve parcialmente el filamento conductor. El estado de ON en la celda muestra una relación lineal ente corriente y tensión, debido al filamento conductor metálico formado. En el caso del estado OFF la relación corriente tensión puede llegar a ser incluso exponencial debido a un comportamiento semiconductor de este estado. Esta relación puede ser atribuida a una alta densidad de defectos profundos en la banda de gap.

#### Forming y SET

El forming comienza con el mecanismo de conducción de la muestra aún virgen. El voltaje aplicado y la corriente que se deriva por ello, se traducen en calentamiento Joule. Ya que la conductividad de la muestra sin estresar se activa térmicamente, al calentarse aumenta más la corriente, lo que lleva a una ruptura termoeléctrica. Este suceso está caracterizado por una descarga del canal en la que la temperatura es elevada, lo que lleva a reaciones redox locales y que forman el filamento conductor. El gradiente de temperatura entre el filamento caliente y la región que lo rodea resulta en una fuerte termodifusión, que conlleva que haya una difusión de aniones de oxígeno fuera de la zona del filamento y difusión de cationes en sentido contrario. La formación de este filamento lleva la celda al estado de ON, y tan pronto como es alcanzada la corriente límite el voltaje cae haciendo que la temperatura local baje, manteniendo ese estado ON estable.

El voltaje necesario para los SETs siguientes es menor que para el forming, ya que el RESET no disolverá por completo el filamento. Lo que hace que al haber menos distancia entre el

filamento restante y el electrodo la tensión necesaria para activar la ruptura termoeléctrica se vea reducida, aunque el proceso es muy similar al forming.

#### RESET

En la operación de RESET, la tensión aplicada y la corriente dan lugar de nuevo al efecto Joule con lo que la temperatura se incrementa y, por ello, el filamento conductor se disuelve debido a procesos activados térmicamente. La temperatura alcanzada durante el RESET es menor que la de SET, ya que, aunque la corriente es mayor el voltaje aplicado es bastante menor. [5, 12]

#### 1.5. Dieléctricos de alta-k

Una de las dificultades que habrá que superar será la del uso de nuevos materiales dieléctricos usados en las estructuras con las que se harán los dispositivos RRAM. En la tecnología actual el uso del silicio está muy extendido, tanto para su uso en transistores como en el uso de su óxido como material dieléctrico, debido a las buenas características que presenta, como: su estabilidad térmica y dinámica sobre sustratos de Si a temperaturas superiores a 1100 °C favorecido por su estructura amorfa, su amplia banda prohibida (9eV), su fácil oxidación que genera un muy buen aislamiento, alta resistividad (10 a 15  $\Omega \dot{c}m$ ), densidades de defectos inferiores a  $10^{10}cm^{-2}eV^{-1}$  y elevados campos de ruptura del óxido que sobrepasan los 15MV/cm.Sinembargo, un inconveniente que se encuentra es que su constante dieléctrica es relativamente baja, que unido a la necesidad de un escalado menor hace que se deban buscar materiales que lo sustituyan para conseguir sistemas mejores. Los dieléctricos de alta permitidad parecen ser la solución más cercana aunque es una solución que necesitan cumplir unos requisitos antes de poder ser incluidos. Por ejemplo, la estabilidad y fiabilidad deben de ser por lo menos igual de buenas, estabilidad térmodinámica (el dieléctrico debe ser estable en contacto con el silicio si no podría reaccionar con el sustrato y formarse siliciuros, silicatos y  $SiO_2$ ), baja densidad de defectos, barreras altas para evitar efectos túnel, preferiblemente con una morfología amorfa, buena calidad en la interface, etc. [14]

En este tipo de estructuras se habla de espesores nanométricos de dieléctrico, por lo que esta capa de la estructura tendrá una gran importancia y por lo que se deberá de estudiar en gran profundidad para ver si cumple las condiciones anteriormente requeridas, además es donde se forma el filamento conductor del que depende el proceso de conmutación resistiva. Esta capa suele estar formada por uno o varios óxidos delgados de alta-k. En la escala a la que se trabaja, del orden de nm, si se redujesen más de 1.2 nm pueden darse ciertos problemas asociados a la reducción de este óxido. Los principales serían corrientes de fugas por efecto túnel y de fiabilidad.

Reduciendo el espesor del dieléctrico se consigue aumentar la densidad de capacidad del óxido:

$$C_{ox} = \frac{\kappa \epsilon_0}{t_{ox}} \tag{1.5}$$

siendo  $\kappa$  es la costante dieléctrica relativa del material,  $\epsilon_0$  permitividad del vacío y  $t_{ox}$  es el espesor del óxido.

En la ecuación 1.5 se puede ver que aumenta la densidad de capacidad disminuyendo el espesor o cambiando el material aislante que tenga una  $\kappa$  mayor, con lo que no habrá problemas de los antes comentados. Las ventajas que esto va a proporcionar será una menor densidad de corrientes de fuga y menor consumo en standby. Los dieléctricos que se proponen para ser incluidos antes deben de ser estudiados para ver una serie de parámetros y propiedades y poder comprobar sus bondades.

Lo primero será saber cual es la constante dieléctrica del aislante, ya que esto puede hacer que disminuya el espesor, pero tampoco puede hacerse demasiado delgado para que no aparezcan problemas relacionados con este aspecto.

Otra propiedad importante es el gap del dieléctrico y la altura de su barrera con respecto al Si. Es importante que esta sea alta, debido a que la corriente de fugas crece exponencialmente si la altura de la barrera disminuye. El gap y la altura se relacionan de la siguiente forma: cuanto mayor sea el gap, mayor será la altura de las barreras. En el caso de los materiales con constante dieléctrica elevada poseen menor gap que los que tienen menor constanste dieléctrica.

También será relevante la calidad de la interface aislante/semiconductor. En la interface, existen defectos en todo el gap del semiconductor debido a que se rompe la red cristalina del sustrato. Para aplicaciones en dispositivos como transistores es deseable que la densidad de defectos en la interface  $(D_{it})$  fuera baja. Ya que una mala calidad de la interface significa que la movilidad efectiva de los portadores en el canal empeoraría y supondría un mayor número de corrientes de fuga. Si en el proceso de fabricación se hace un recocido puede mejorar la calidad de la interface.

Por último, la morfología que presente el dieléctrico influirá en su comportamiento. El uso de dieléctricos que presenten una esctructura amorfa tiene algunas diferencias sobre la policristalina. En estos últimos, existe unas fronteras entre las diferentes zonas cristalográficas que facilitan la conducción en el aislante que puede hacer que aumente la corriente de fugas. Además de que el tamaño y orientación de las zonas cristalográficas (grano) pueden dar lugar a variaciones en la constante dieléctrica. Los dieléctricos de alta permitividad suelen ser policristalinos, lo que es un problema que esta siendo investigado. [4]

En el caso que ocupa este trabajo, para las estructuras MIS que pueden dar lugar a memorias RRAM interesará que haya una serie de defectos tanto en la interface como en el interior del dieléctrico que puede hacer que se vea favorecido el mecanismo RS, como pudiera ser la potenciación de vacantes de oxígeno sin que haya mayor cantidad del resto defectos y además que estén donde se desee y no de forma descontrolada ya que si no empeoraría la repetitividad en la estructura.

# Parte II Procedimiento Experimental

# Capítulo 2

# Instrumentos de Medida

En este capítulo pasaremos a describir el equipamiento con el que se ha hecho la caracterización eléctrica de cada una de las muestras medidas. Se dará una breve descripción de las características más relevantes y su finalidad, ya que, los equipos son solamente un medio para llegar al objetivo de caracterizar las estructuras bajo estudio. Más adelante se hablará de como han sido los montajes realizados para ejecutar las diferentes técnicas de caracterización.

Los equipos con los que se trabajó principalmente y que permitieron la caracterización eléctrica de las muestras fueron:

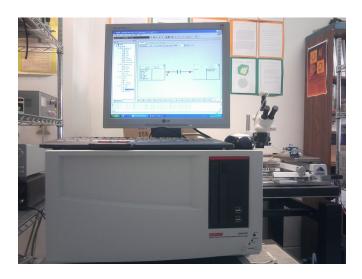

# 2.1. Sistema de caracterización de semiconductores Keithley 4200-SCS

El sistema de caracterización de semiconductores Keithley 4200-SCS se utilizó para medir y analizar las características de los dispositivos semiconductores. Es un equipo complejo con muchas funcionalidades, por ello, para un mayor conocimiento del mismo consultar el manual completo del equipo que contiene toda la información hardware y software. [15]

El equipo Keithley, figura 2.1, es un sistema automatizado que permite hacer medidas I-V, C-V y G-V para la caracterización de dispositivos semiconductores. Permite tanto la medida con un barrido en voltaje o corriente como medidas pulsadas. El sistema esta sustentado sobre una arquitectura PC y puede ser manejado desde las diferentes aplicaciones que tiene, las cuales estan intaladas en un sistema operativo *Microsoft Windows*. Las diferentes medidas se hacen mediante las llamadas unidades SMUs (*Source-Measure Units*), cuyas capacidades pueden ser ampliadas por medio de componentes externos.

En cuanto a las características hardware generales podemos destacar:

- 8 ranuras para módulos: estas ranuras servirán para ampliar unidades con diferentes funcionalidades al equipo, estas pueden ser SMUs, unidades de pulsos...

- Display: para la visualización del sistema tenemos según el modelo: un display de 12.1 pulgadas incluido en el equipo (modelo 4200-SCS/F) u otro que necesite de un monitor externo (modelo 4200-SCS/C) conectado mediante VGA.

Figura 2.1: Analizador de semiconductores Keitley 4200-SCS

- Ordenador: gobierna el funcionamiento del equipo. Se trata de un ordenador compatible con IBM PC que corre sobre Microsoft Windows XP Professional.

- Interfaz GPIB (IEEE-488): permite el control de dispositivos externos conectados mediante GPIB o ser controlado de forma remota.

- Puertos RS-232 y paralelo: interfaz para el manejo de periféricos como una mesa de puntas, una impresora, un plotter...

- Conector LAN: conexión Ethernet, por tanto para una conexión a una red local.

- Puertos USB: 4 puertos USB 2.0 que proveen una interfaz para periféricos como impresoras, memorias flash, escáner, discos duros externos...

Las diferentes unidades que utiliza para las medidas de los dispositivos son:

- Source-Measure Unit (SMU): el módulo fundamental del equipo, son unidades de tipo aplicación-medida cuyas operaciones fundamentales de medida son: se aplica una fuente de tensión y se mide corriente/voltaje y se aplica una corriente y se mide voltaje/corriente. Los rangos de corrientes y voltajes que pueden ser aplicados y medidos podemos verlos en la tabla 2.1.

- Unidad CVU: Se trata de una tarjeta de medición de impedancia de varias frecuencias (10 kHz a 10 MHz) que se instala en el propio Keithley 4200-SCS. La señal de test AC (entre 10 mV RMS y 100 mV RMS) puede estar polarizada en tensión continua de -30 V a +30 V. La unidad CVU mide la impedancia introduciendo una tensión alterna a través del dispositivo que se vaya a medir (DUT) y después mide la corriente alterna resultante y la diferencia de fase. La capacitancia y la conductancia son parámetros derivados de la impedancia y fase medidas.

| Función                       | Danmag                          | Función                       | D                                     |  |

|-------------------------------|---------------------------------|-------------------------------|---------------------------------------|--|

| (fondo de escala/resolución)  | Rangos                          | (fondo de escala/resolución)  | Rangos                                |  |

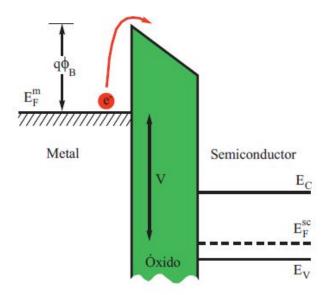

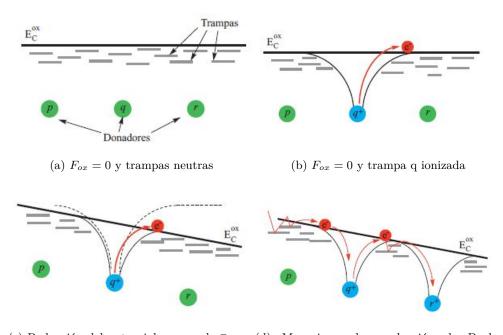

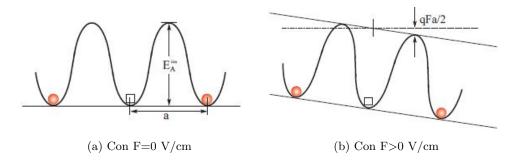

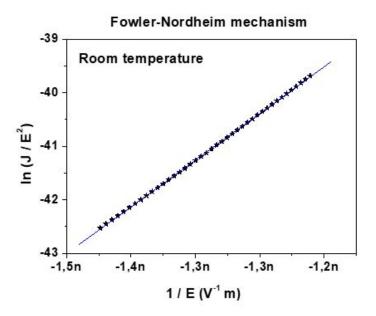

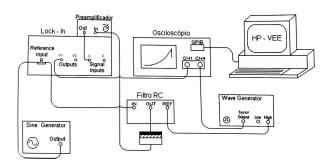

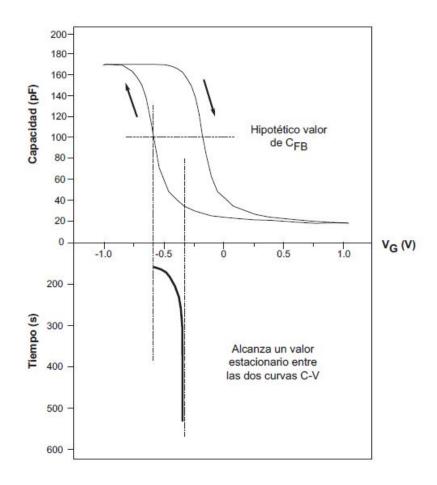

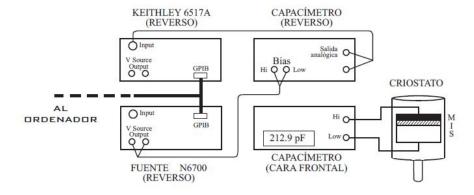

|                               | 105 nA / 5 pA                   |                               | 105 nA / 1pA                          |  |