# Universidad de Valladolid

ESCUELA TÉCNICA SUPERIOR DE INGENIERÍA INFORMÁTICA

DEPARTAMENTO DE INFORMÁTICA

TESIS DOCTORAL:

# Parallel Approaches to Shortest-Path Problems for Multilevel Heterogeneous Computing

Presentada por

D. Héctor Ortega Arranz

para optar al grado de doctor por la Universidad de Valladolid

Dirigida por:

Dr. Diego R. Llanos Ferraris Dr. Arturo González Escribano

> Valladolid, 2015

ii

#### Resumen

Desde hace mucho tiempo, diferentes algoritmos de grafos han solucionado problemas relacionados con la computación del camino más corto. Este tipo de problemas se considera como uno de los problemas más importantes dentro de la categoría de optimización combinatoria, debido a sus múltiples aplicaciones a problemas prácticos relacionados con la vida real. Entre algunos de estos ejemplos se encuentra la navegación de coches y/o robots en carreteras u otras superficies, las simulaciones de tráfico, optimización de recursos para compañías de envío de paquetes, rutado de paquetes en Internet, búsquedas en la web, o la explotación de beneficios con cambios de monedas. Sin embargo, durante las últimas décadas, el interés de la comunidad científica por este tipo de problemas ha crecido significativamente, no sólo por la amplia aplicabilidad de sus soluciones, sino también por el actual popular uso eficiente de la computación paralela. Además, la aparición de nuevos modelos de programación junto con los modernos aceleradores hardware, como los procesadores de gráficos (GPUs) y las tarjetas XeonPhi, ha enriquecido el rendimiento de los algoritmos paralelos anteriores, y ha propiciado la creación de nuevos algoritmos más eficientes. Por otra parte, el uso conjunto de estos aceleradores hardware junto con las clásicas CPUs conforman la herramienta perfecta para enfrentarse, dentro de un contexto de cómputo de altas prestaciones, a los problemas más costosos relacionados con el cálculo de caminos más cortos.

Sin embargo, la programación de estos aceleradores hardware, su optimización, y su coordinación con otros elementos de computación de diferente naturaleza, son tareas aún muy complicadas para los programadores no expertos. Una de las razones por las que estas tareas son demasiado complejas es la falta de estudios que puedan guiar al programador a utilizar valores apropiados para los parámetros de ejecución de las GPUs. Respecto a la coordinación de diferentes unidades computacionales, tampoco existen muchos modelos o herramientas que simplifiquen la programación de diferentes capas de cómputo paralelo. Por ejemplo, el uso conjunto de los diferentes cores de una CPU dentro de un sistema de memoria compartida, o incluso de otros sistemas externos.

Este trabajo de Tesis Doctoral aborda ambos contextos mencionados anteriormente mediante: el desarrollo de nuevos planteamientos orientados a plataformas GPU para la resolución de problemas de caminos cortos, junto con el estudio del ajuste óptimo de los parámetros de ejecución; y el diseño de soluciones donde algoritmos secuenciales y paralelos son desplegados, de manera concurrente, en entornos heterogéneos.

#### **Palabras clave**

Modelo paralelo abstracto, APSP, tuning automático de kernels, Boost Graph Library, configuración de la Cache L1, ejecución concurrente de kernels, CUDA, Dijkstra, GPGPU, sistemas heterogéneos, framework HPC, modelo de caracterización de kernels, proceso de caracterización de kernels, balanceo de carga, MPI, comparativa de plataformas de NVIDIA, OpenMP, técnicas de optimización, algoritmos paralelos, SSSP, geometría del bloque de hilos.

### Abstract

Many graph algorithms have given solution to the problem of finding shortest paths between nodes in a graph. These problems are considered among the fundamental combinatorial optimization problems. They have many applications, such as car/robot navigation systems, traffic simulations, tramp steamer problem, courier-scheduling optimization, Internet route planners, web searching, or exploiting arbitrage opportunities in currency exchange, among others. During the last decades, the interest of the scientific community in these problems has significantly increased not only due to this wide-applicability, but also thanks to the currently popular and efficient parallel computing. Additionally, the advent of new parallel programming models together with modern powerful hardware accelerators, such as the Graphics Processing Units or the many-core XeonPhis boards, may highly improve the performance of previous parallel algorithms, and also has open the possibility to study new and more efficient parallel approaches to exploit these specific architectures. Furthermore, the emerging of heterogeneous parallel computing combining these powerful hardware accelerators with the classical and increasingly powerful CPUs, provides a perfect environment to face the most costly shortest-path problems in the context of High Performance Computing (HPC).

However, the programming of hardware accelerators, the optimization of their running times, and also, the coordination of these devices with other computational units of different nature, are still very complex tasks for non-expert programmers. One important indicator of the added complexity found in these environments is the lack of studies to guide the programmer into the correct use of proper values for GPU runtime configuration parameters. Regarding the coordination of different computational devices, there are also few models or frameworks that simplifies the programming when different parallel computing layers are used, to combine the use of many-cores and classical CPU cores present in a shared-memory system, or even from different systems.

This Ph.D. thesis addresses both mentioned problems, the algorithmic GPU programming and the heterogeneous parallel coordination in the context of: Developing new GPUbased approaches to the shortest path problem; the study of the tuning of the GPU configuration parameters; and also, designing solutions where both sequential and parallel algorithms are deployed concurrently in heterogeneous environments.

### Keywords

Abstract parallel model, APSP, automatic kernel tuning, Boost Graph Library, cache L1 configuration, concurrent kernel execution, CUDA, Dijkstra, GPGPU, heterogeneous systems, HPC framework, kernel characterization model, kernel characterization process, load-Balancing, MPI, NVIDIA platform comparison, OpenMP, optimization techniques, parallel algorithms, SSSP, threadblock size.

"Donde no falta voluntad siempre hay un camino"

"If there is a will, there is a way"

J.R.R. Tolkien (1892 - 1973)

vi

### Acknowledgments

Aún recuerdo cuando de pequeño, y no tan pequeño, hablaba de recorrer esta ruta, que aún era desconocida para mí. Recuerdo cuando empecé a andarla, y en particular, el momento cuando descubrí, qué misterios se discernían tras estos caminos. Recuerdo sentir cómo ese crucero se transformaba en odisea, y el desafío se tornaba más difícil de lo que a veces uno desea. Muchas otras cosas seguro habré dejado en el pasado, pero de lo que no me he olvidado, es que no estaba yo sólo en esa senda. Gracias a los que me han acompañado, puedo recordar que he sido capaz de enfrentarme a todo por perseguir esa meta. Es a ellos a quienes van dedicados estos párrafos.

En primer lugar quiero agradecer a Diego y Arturo por aceptarme y darme la oportunidad de empezar este viaje, por su ayuda y apoyo durante el largo y duro recorrido, y su trabajo para que todo esto llegara a buen puerto. Quiero agradecer también, y resaltar la importancia de haber tenido unos inmejorables compañeros de travesía, y amigos, Yuri, Sergio, Javier, Álvaro y Ana. Sin su compañía, comprensión, empatía y ayuda esta andadura habría sido siempre muy oscura.

Igualmente quiero agradecer el insuperable trato que recibí durante mi pequeña y entrañable aventura en St. Andrews. No sólo de la gente de la universidad que me acogió, apoyó y confió en mí como si siempre hubiera trabajado con ellos, sino también a todas las personas que allí conocí, y con las que mucho más que anécdotas inolvidables compartí.

Por último, agradecer a mis amigos, a mis padres, y a mi hermano Alex, que tantas veces me han visto partir, siempre me han ayudado y siempre han confiado en mí, y nunca me han faltado cuando regresaba y les necesitaba. Y a quien siempre ha estado ahí, también, GRACIAS!

> Héctor Ortega-Arranz Valladolid, 2015

This research has been partially supported by the FPI-UVa 2011 and HiPEAC 2014 scholarships, the Ministerio de Economía y Competitividad (Spain) and ERDF program of the European Union: CAPAP-H5 network (TIN2014-53522-REDT), MOGECOPP project (TIN2011-25639); Junta de Castilla y León (Spain): ATLAS project (VA172A12-2); HomProg-HetSys project TIN2014-58876-P; and the COST Program Action IC1305: NESUS.

viii

## Contents

| R | Resi        | ımen de la tesis                                                    | 1  |

|---|-------------|---------------------------------------------------------------------|----|

|   | <b>R</b> .1 | Pregunta de Investigación                                           | 3  |

|   |             | R.1.1 Metodología de Investigación                                  | 3  |

|   | <b>R</b> .2 | Objetivos                                                           | 4  |

|   | <b>R</b> .3 | Estructura de la Tesis                                              | 7  |

|   |             | R.3.1 Síntesis de Capítulos y Contribuciones                        | 8  |

|   | <b>R</b> .4 | Conclusiones                                                        | 12 |

| 1 | Intro       | oduction                                                            | 13 |

|   | 1.1         | Motivation                                                          | 13 |

|   |             | 1.1.1 Parallel Computing                                            | 14 |

|   |             | 1.1.2 GPUs for Parallel Computing                                   | 16 |

|   |             | 1.1.3 Heterogeneous Computing                                       | 18 |

|   | 1.2         | Objectives of the dissertation                                      | 18 |

|   |             | 1.2.1 Research Methodology                                          | 18 |

|   |             | 1.2.2 Milestones                                                    | 19 |

|   | 1.3         | Document Structure                                                  | 21 |

| 2 | State       | e of the Art of the Shortest-Path Problem                           | 23 |

|   | 2.1         | Brief Introduction to Graph Theory                                  | 23 |

|   | 2.2         | The Single-Source Shortest-Path (SSSP) Problem                      | 27 |

|   |             | 2.2.1 Taxonomy of SSSP Algorithms                                   | 27 |

|   |             | 2.2.2 Dijkstra's Algorithm                                          | 29 |

|   | 2.3         | Parallel Solutions for the SSSP ( $\Pi$ -SSSP)                      | 31 |

|   |             | 2.3.1 Parallelizing the Internal Operations of the SSSP Algorithm   | 31 |

|   |             | 2.3.2 Deploying Sequential SSSPs in Disjoint Subgraphs Concurrently | 33 |

|   |             | 2.3.3 Deploying Parallel SSSPs in Disjoint Subgraphs Concurrently   | 34 |

|   | 2.4         | The All-Pair Shortest-Path (APSP) Problem                           | 34 |

|   |             | 2.4.1 Taxonomy of APSP Algorithms                                   | 34 |

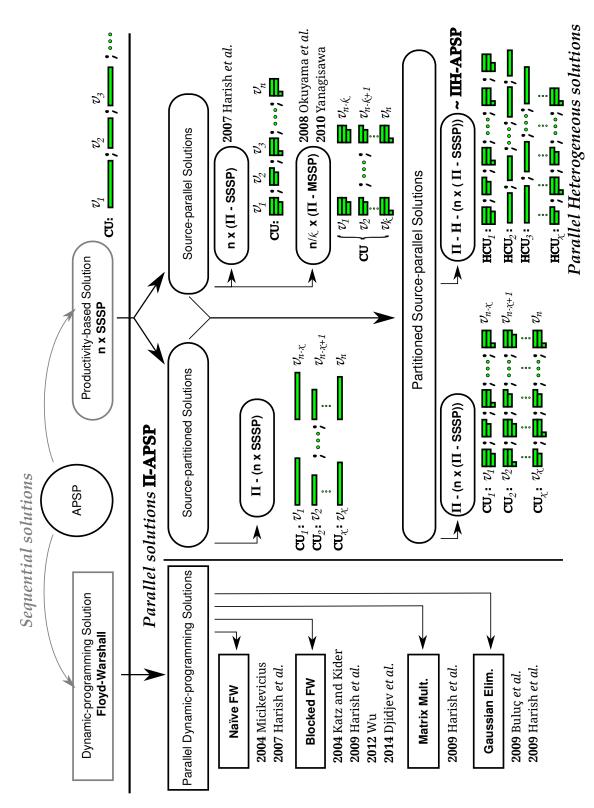

|   | 2.5         | Parallel Solutions for the APSP (II-APSP)                           | 38 |

|   |             | 2.5.1 Strategy A: Parallel Dynamic-programming Solutions            | 39 |

|   |             | 2.5.2 Strategy B: Parallel Productivity-based Solutions             | 41 |

|   | 2.6         | Application Example: Shortest-Path Algorithms applied to roadmaps   | 44 |

### CONTENTS

|   |      | 2.6.1 One-Pair Shortest-Path Problem                                   | 45       |

|---|------|------------------------------------------------------------------------|----------|

|   |      | 2.6.2 The Importance of Preprocessing: Routing Algorithms as Example   | 47       |

|   | 2.7  | Summary                                                                | 51       |

| 3 | Ugir | g GPUs to solve the Single-Source Shortest-Path Problem                | 53       |

| 5 | 3.1  | Defining the Frontier Set and the $\Delta$ Threshold                   | 53       |

|   | 5.1  | 3.1.1 Martín's GPU Algorithm                                           | 55<br>54 |

|   | 3.2  |                                                                        | 57       |

|   | 3.2  | Applying Crauser's Ideas to Increase the $\Delta$ Threshold            |          |

|   |      | 3.2.1 Crauser's Algorithm                                              | 57       |

|   | • •  | 3.2.2 Porting Crauser's Ideas to a GPU Implementation                  | 60       |

|   | 3.3  | Experimental Evaluation of the GPU-SSSP Algorithm                      | 60       |

|   |      | 3.3.1 Methodology                                                      | 60       |

|   |      | 3.3.2 Input set characteristics                                        | 63       |

|   |      | 3.3.3 Experimental Results I - State of the Art Comparison             | 65       |

|   |      | 3.3.4 Experimental Results II - Boost Graph Library Comparison         | 70       |

|   |      | 3.3.5 Experimental Results III - Architectural Comparison              | 76       |

|   | 3.4  | Conclusions                                                            | 76       |

| 4 | Exh  | ustive Search for GPU Optimal Parameter Values                         | 81       |

|   | 4.1  | Problem Description: The Importance of Using                           |          |

|   |      | Proper Values for Tuning Parameters                                    | 81       |

|   | 4.2  | State of the Art: Scarce Models for GPU Configuration Parameter Tuning | 82       |

|   | 4.3  | Kernel Characterization Model: Code-Dependent Parameters               | 84       |

|   | 4.4  | Kernel Characterization Model: Graph-Dependent Parameters              | 85       |

|   | 4.5  | Characterizing the Kernels of the SSSP Algorithm                       | 86       |

|   |      | 4.5.1 Predictions for the Threadblock-size Values                      | 87       |

|   |      | 4.5.2 Predictions for L1-cache Management                              | 89       |

|   | 4.6  | Experimental Evaluation                                                | 89       |

|   | 1.0  | 4.6.1 Methodology                                                      | 90       |

|   |      | 4.6.2 Input set characteristics                                        | 92       |

|   |      | 4.6.3 Experimental Results: Exhaustive Evaluation of CUDA Runtime      | 12       |

|   |      | Configuration Parameters                                               | 92       |

|   |      | 4.6.4 Study I - CK Compatibility with Model Predictions                | 92<br>95 |

|   |      | 4.6.5 Study II - Validation of Model Predictions                       | 95<br>95 |

|   |      |                                                                        |          |

|   | 4.7  | 4.6.6 Study III - Usefulness of Model Predictions                      | 96<br>99 |

|   |      |                                                                        |          |

| 5 |      |                                                                        | 101      |

|   | 5.1  | 1 11                                                                   | 101      |

|   | 5.2  |                                                                        | 102      |

|   | 5.3  |                                                                        | 103      |

|   |      | 1 0                                                                    | 104      |

|   |      | 5.3.2 Work-queue retrieving Scheduling                                 | 104      |

|   | 5.4  | Experimental Evaluation on a Heterogeneous Shared-Memory System        | 105      |

|   |      | 5.4.1 Methodology                                                      | 105      |

|   |      | 5.4.2 Input Set Characteristics                                        | 107      |

|   |      |                                                                        |          |

### CONTENTS

|   |     | 5.4.3    | Experimental Results I - Complete APSP Evaluation                 |     |

|---|-----|----------|-------------------------------------------------------------------|-----|

|   |     | 5.4.4    | Experimental Results II - Random Scalability Evaluation           | 110 |

|   | 5.5 | Conclu   | isions                                                            | 111 |

| 6 | TuC |          | Programming Model                                                 | 113 |

|   | 6.1 |          | m Description: The Need for Speed and the Lack of an Unified      |     |

|   |     |          | on                                                                | 113 |

|   | 6.2 |          | f the Art: Looking for One Tool to Rule All Parallel Levels       | 114 |

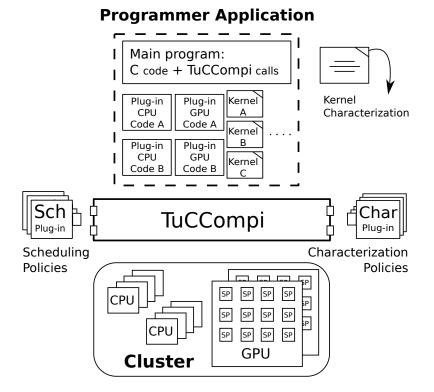

|   | 6.3 |          | ompi: The Distributed Heterogeneous Computing Model               | 115 |

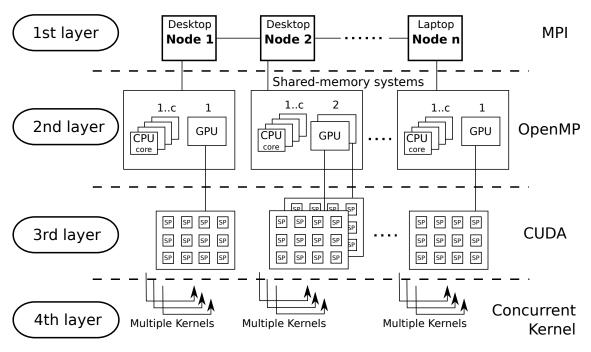

|   |     | 6.3.1    | The Multi-Layer Architecture                                      | 116 |

|   |     | 6.3.2    | TuCCompi Model Usage                                              | 118 |

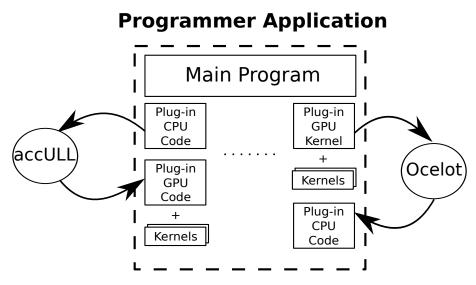

|   |     | 6.3.3    | The External-Work Attachable to TuCCompi                          | 121 |

|   | 6.4 |          | ototype Internals                                                 | 123 |

|   | 6.5 |          | g the SSSP Implementation to TuCCompi                             | 128 |

|   | 6.6 | Experi   | mental Evaluation of TuCCompi Prototype                           | 131 |

|   |     | 6.6.1    | Methodology                                                       | 131 |

|   |     | 6.6.2    | Input Set Characteristics                                         | 133 |

|   |     | 6.6.3    | Experimental Results I - Checking TuCCompi's Layers               | 133 |

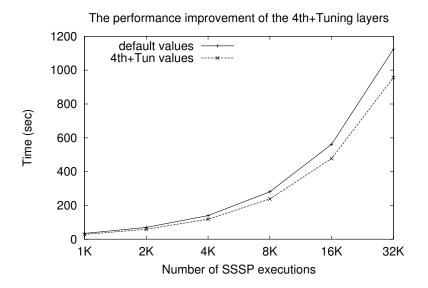

|   |     | 6.6.4    | Experimental Results II - The Innovative 4th and Tuning Layers .  | 135 |

|   | 6.7 | Conclu   | isions                                                            | 135 |

| 7 | Con | clusions | 5                                                                 | 137 |

|   | 7.1 | Answe    | er to the Research Question                                       | 137 |

|   | 7.2 | Summa    | ary of Contributions                                              | 138 |

|   |     | 7.2.1    | Surveys and classification studies for the algorithms involved in |     |

|   |     |          | Shortest Path problems                                            | 138 |

|   |     | 7.2.2    | Development of a new GPU-based algorithm outperforming a pre-     |     |

|   |     |          | vious state-of-the-art GPU SSSP solution                          | 140 |

|   |     | 7.2.3    | Extension of the kernel characterization model                    | 140 |

|   |     | 7.2.4    | Studies of novel heterogeneous approaches for the APSP problem    | 141 |

|   |     | 7.2.5    | Development of a multilayer programming model: TuCCompi           | 142 |

|   | 7.3 | Future   | Directions                                                        | 143 |

| A | Gra | phical F | Results from the Exhaustive Search                                | 145 |

xi

### CONTENTS

# List of Figures

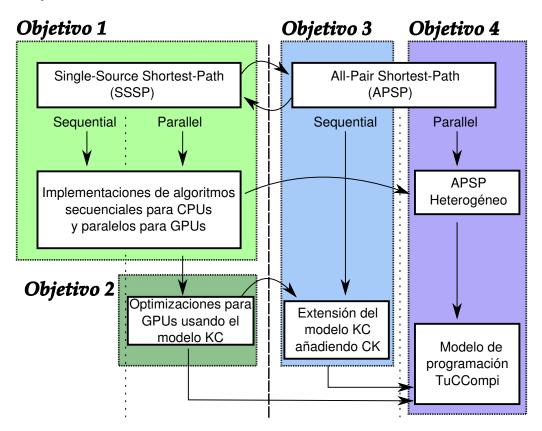

| <b>R</b> .1 | Diferentes objetivos propuestos para el desarrollo de esta tesis doctoral.     | 5  |

|-------------|--------------------------------------------------------------------------------|----|

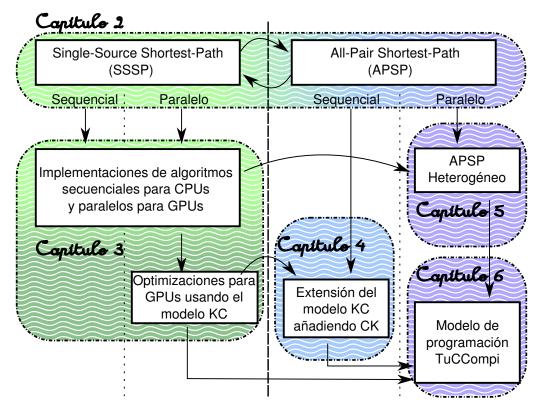

| <b>R</b> .2 | Estructura del documento.                                                      | 7  |

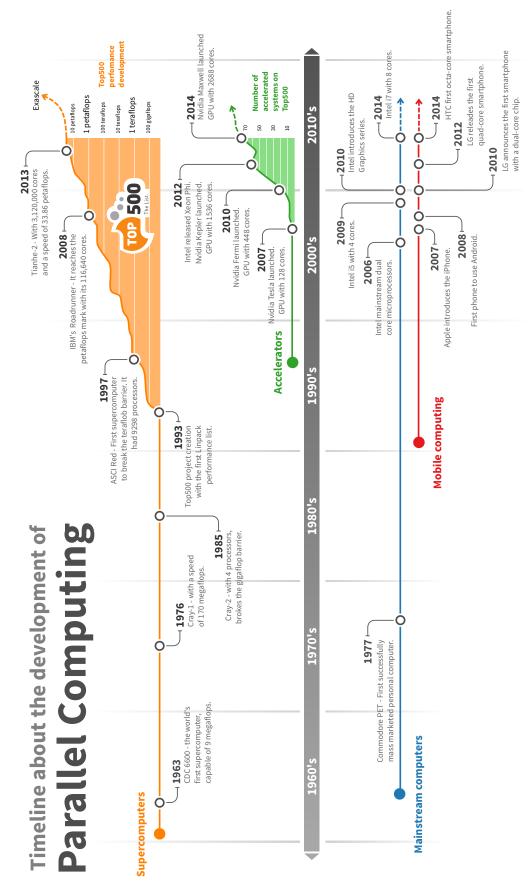

| 1.1         | Evolution timeline of parallel computing.                                      | 15 |

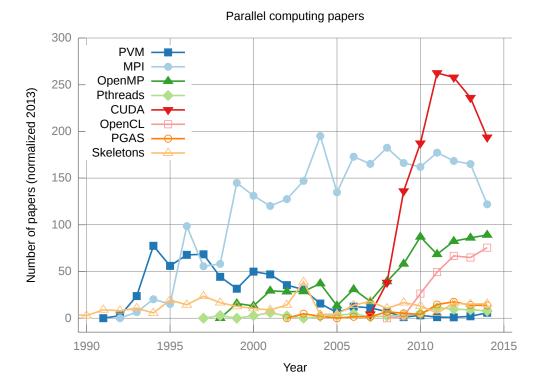

| 1.2         | Number of papers related with different parallel computing technologies.       | 16 |

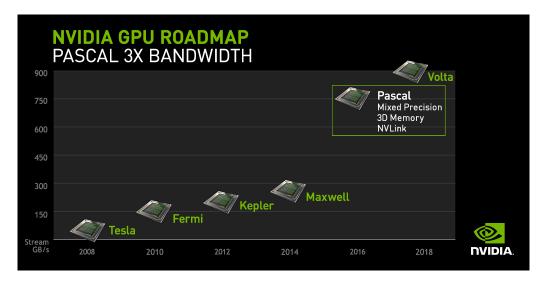

| 1.3         | Bandwidth estimated for future architectures of NVIDIA GPU devices.            | 17 |

| 1.4         | Goals and subgoals to be accomplished in this Ph.D. thesis                     | 19 |

| 1.5         | Document structure                                                             | 22 |

| 2.1         | Examples of paths in an undirected graph and a directed graph.                 | 25 |

| 2.2         | Examples of a shortest path and a shortest path tree                           | 26 |

| 2.3         | Dijkstra's algorithm steps.                                                    | 29 |

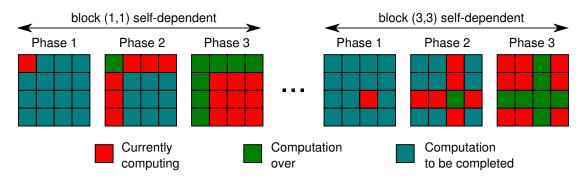

| 2.4         | Phases of the FW algorithm proposed by Venkataraman, that lately was           |    |

|             | used by Katz and Kider for GPUs                                                | 38 |

| 2.5         | Taxonomy of parallel solutions for the APSP.                                   | 42 |

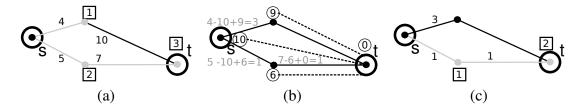

| 2.6         | Settled nodes reordering from Dijkstra's to A*.                                | 46 |

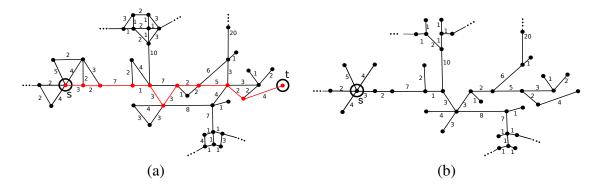

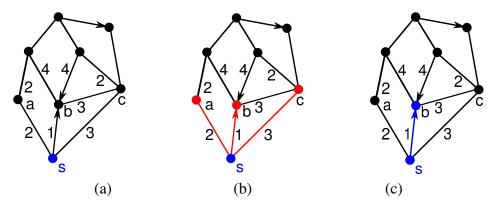

| 3.1         | Examples of a graph with Crauser's out values highlighted                      | 58 |

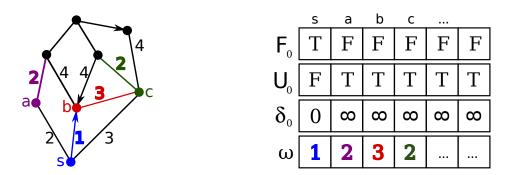

| 3.2         | Crauser's algorithm steps.                                                     | 58 |

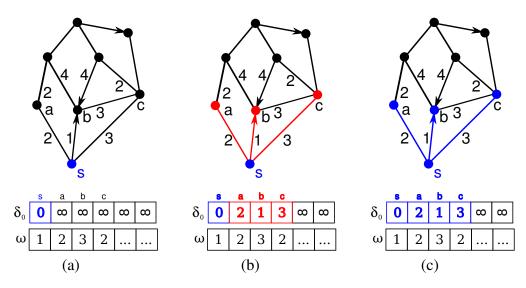

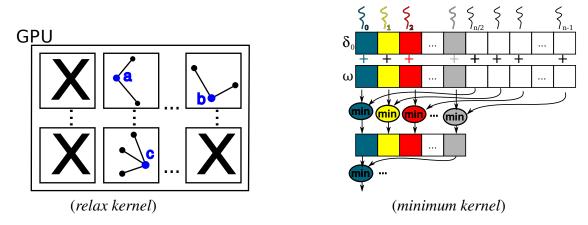

| 3.3         | Graphical description of the <i>relax kernel</i> and the <i>minimum kernel</i> | 58 |

| 3.4         | Temporal cost of the different source nodes in the graph for the Kepler GPU.   | 63 |

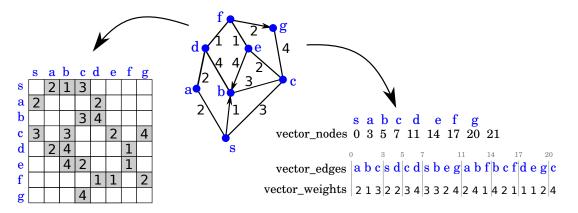

| 3.5         | Graph represented through an adjacency matrix and the CSR storage format.      | 65 |

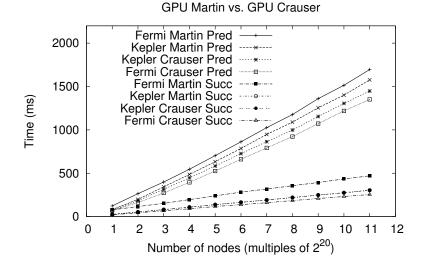

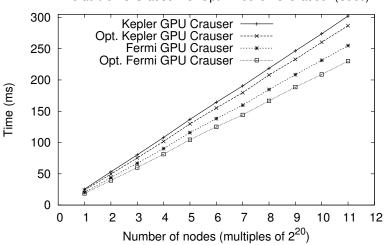

| 3.6         | GPU Martín vs GPU Crauser using Martín graphs.                                 | 65 |

| 3.7         | GPU Martín vs GPU Crauser using Random graphs                                  | 67 |

| 3.8         | GPU Martín vs GPU Crauser using Real-world graphs.                             | 69 |

| 3.9         | GPU Crauser vs its optimized version using Martín graphs                       | 70 |

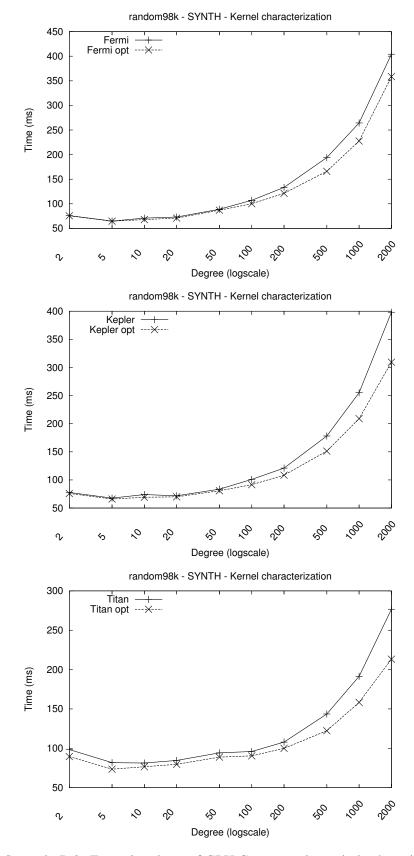

| 3.10        | GPU Crauser vs its optimized version using Random graphs                       | 71 |

| 3.11        | GPU Crauser vs its optimized version for social networks and kronecker         |    |

|             | graphs                                                                         | 72 |

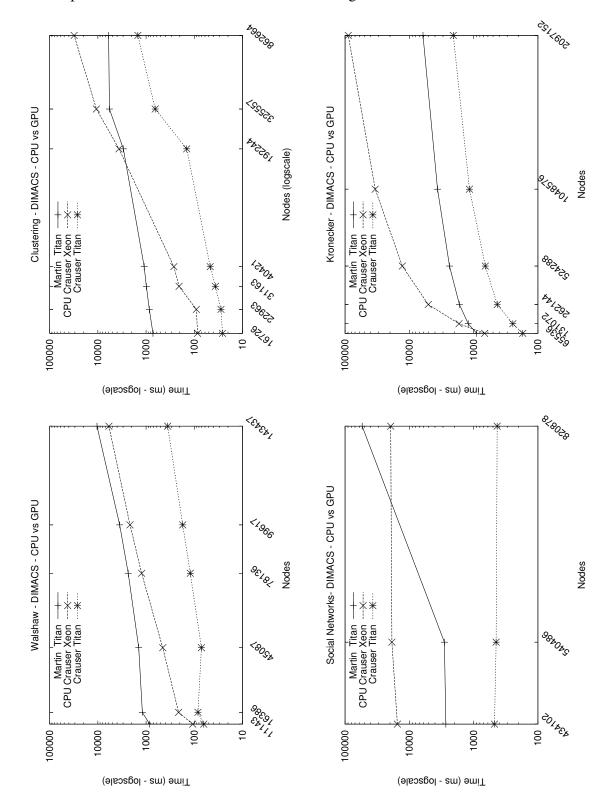

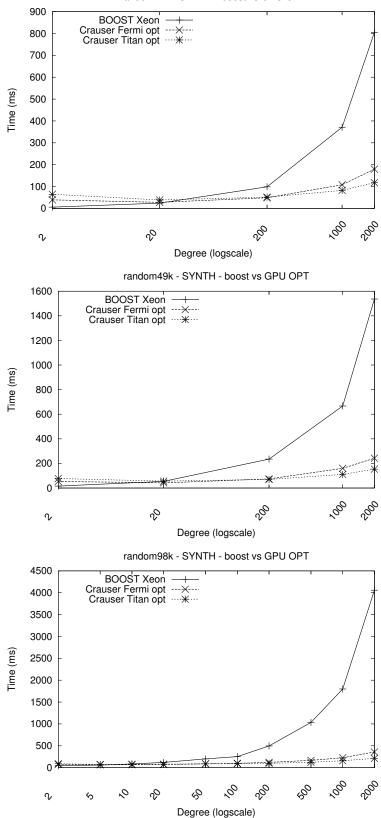

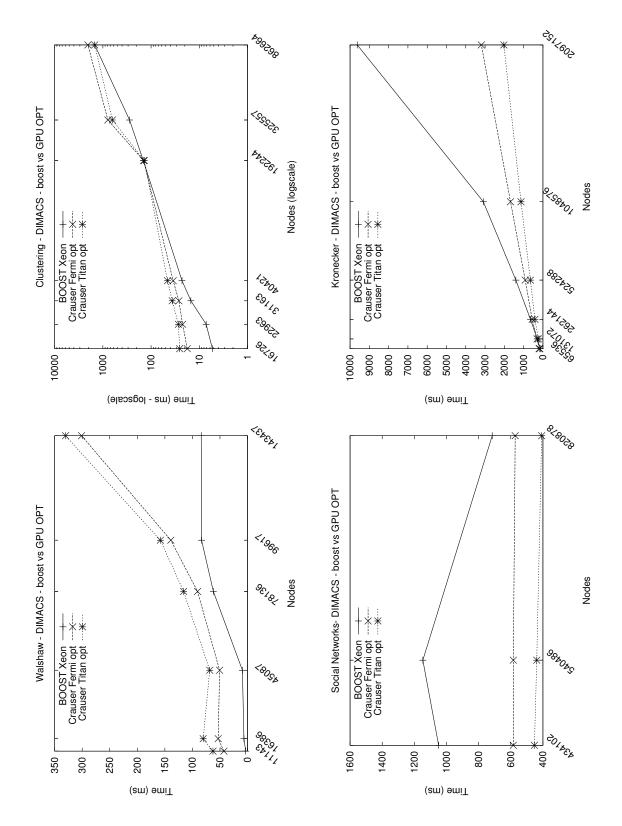

|             | Optimized GPU Crauser vs Dijkstra's Boost Library in Random graphs             | 73 |

|             | Optimized GPU Crauser vs Dijkstra's Boost Library in Real-world graphs.        | 74 |

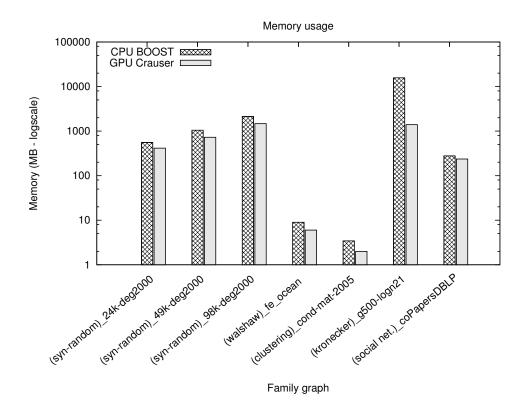

|             | Memory usage of the Boost Library and the GPU Crauser version                  | 75 |

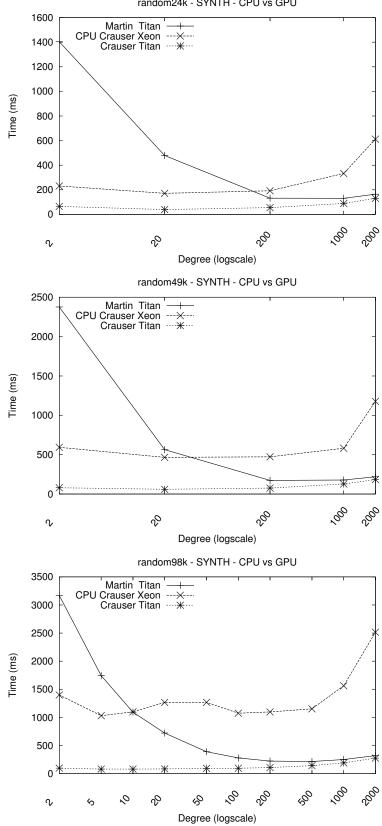

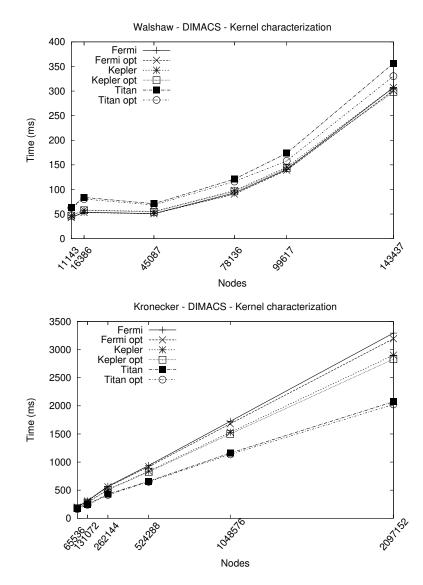

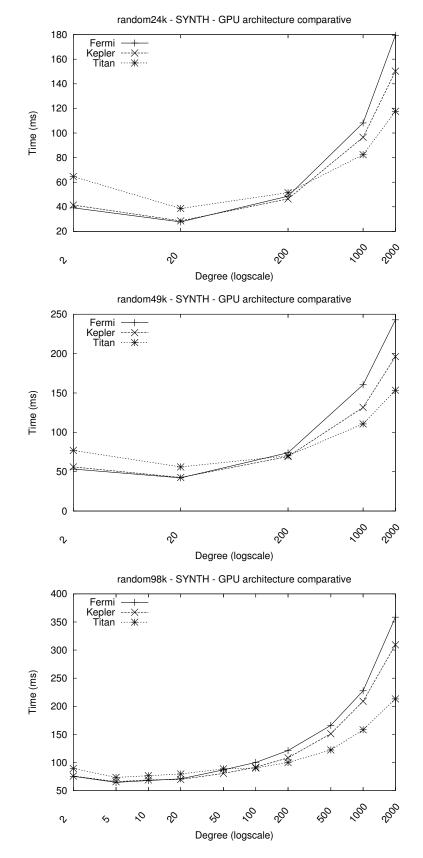

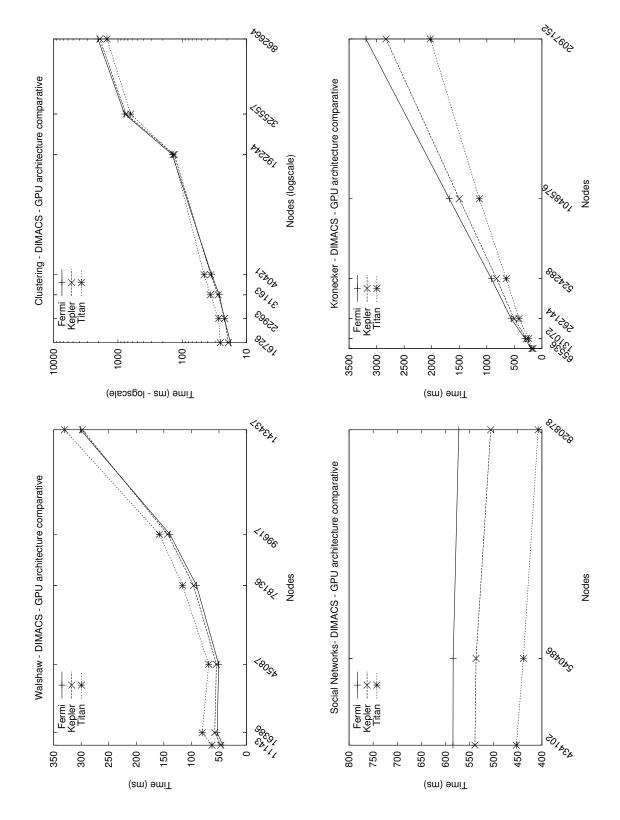

| 3.15        | CUDA architectural comparison for the random and real-world graphs             | 77 |

| 3.16                                                                       | CUDA architectural comparison for the random and real-world graphs                                                                                                                | 78                                                                                                                                                                                               |

|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

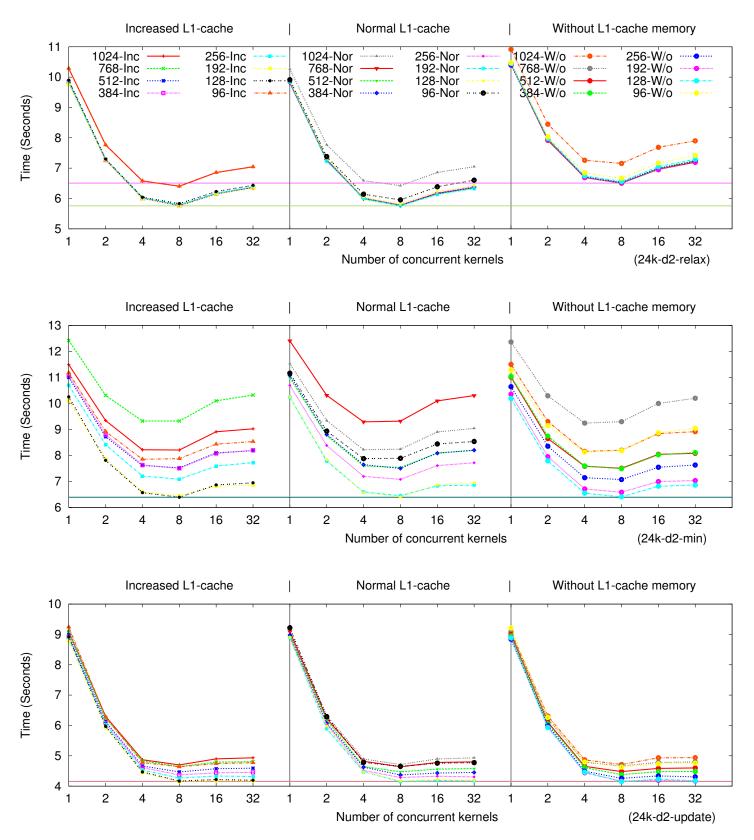

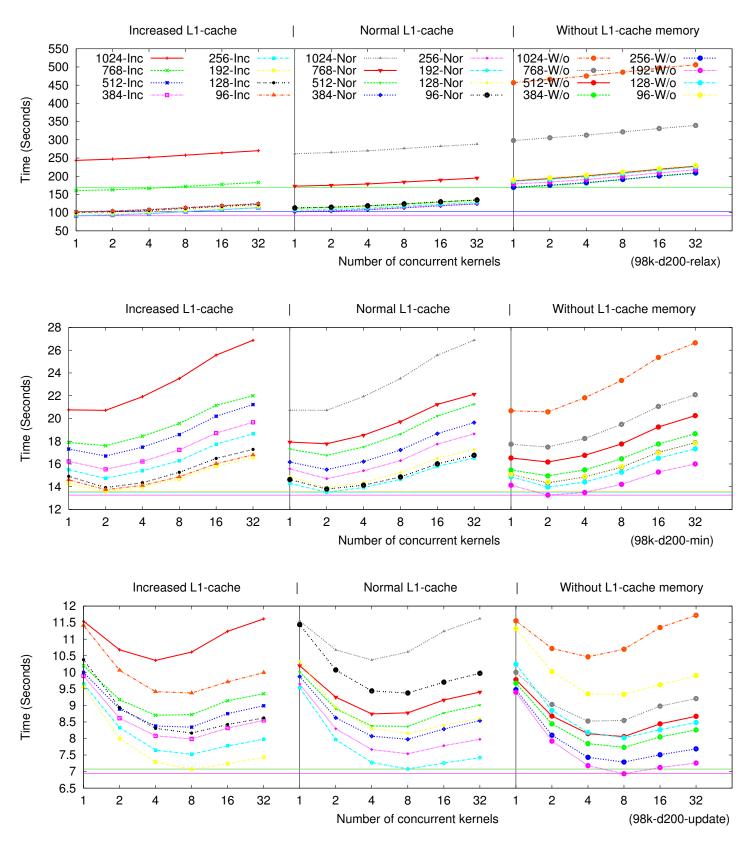

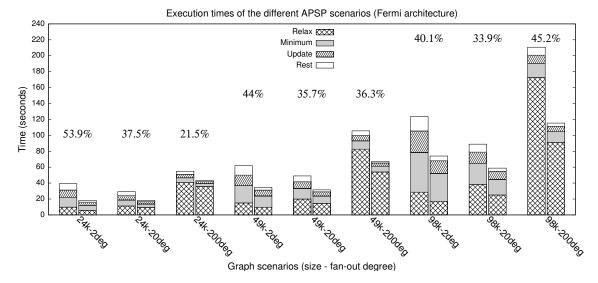

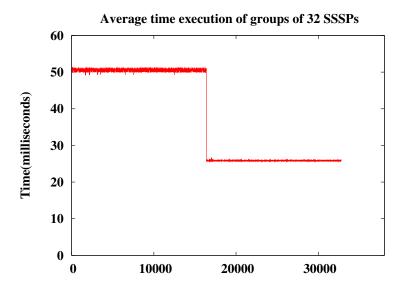

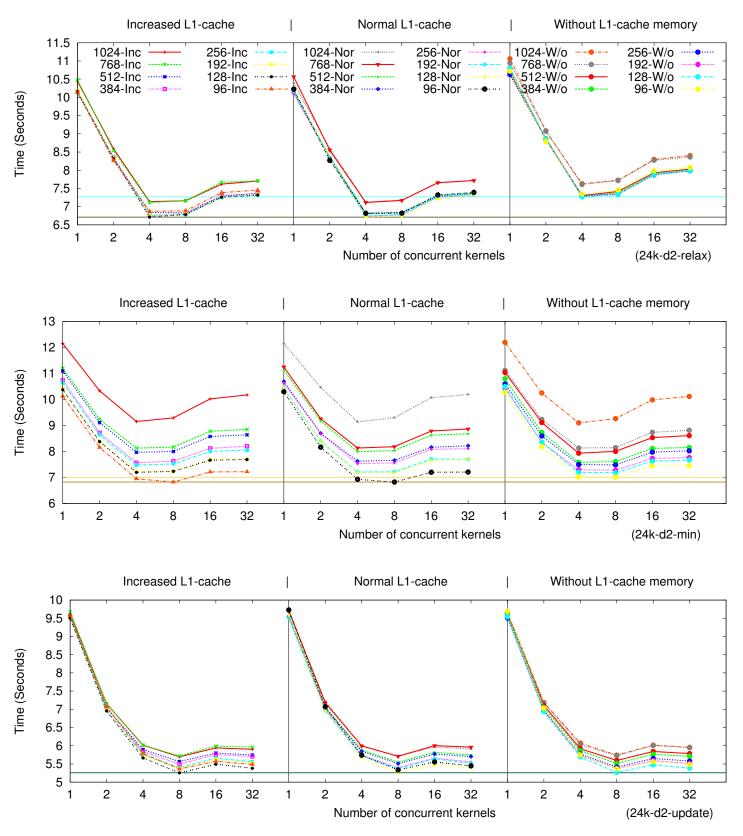

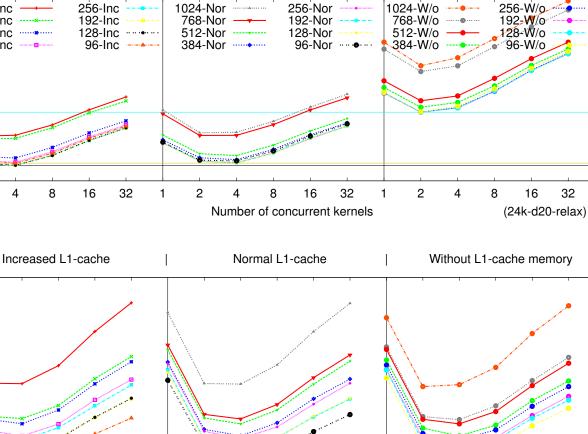

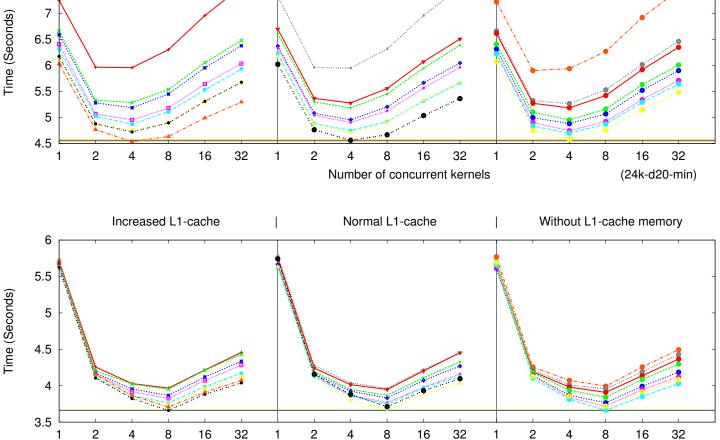

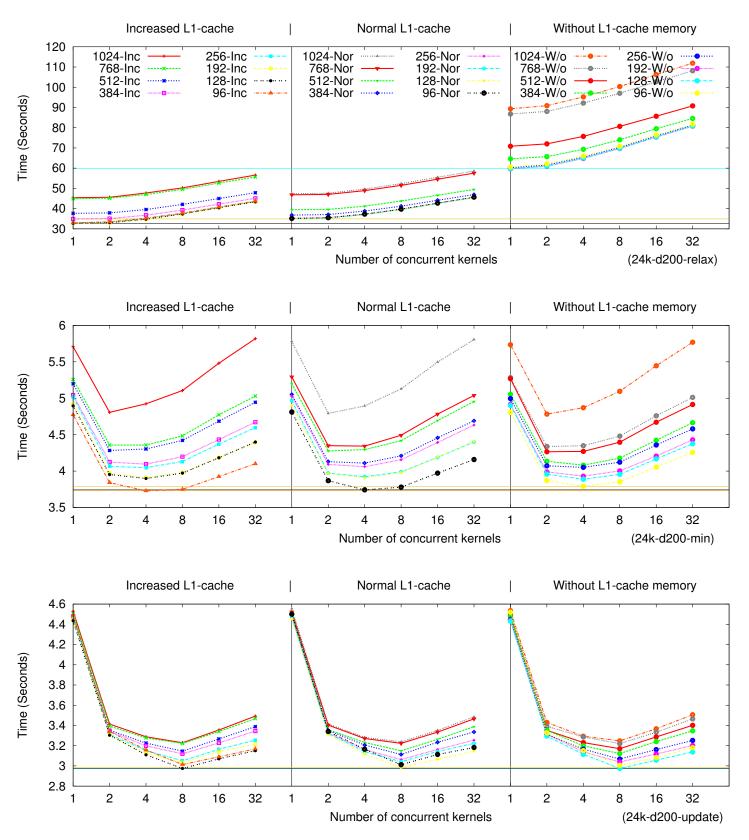

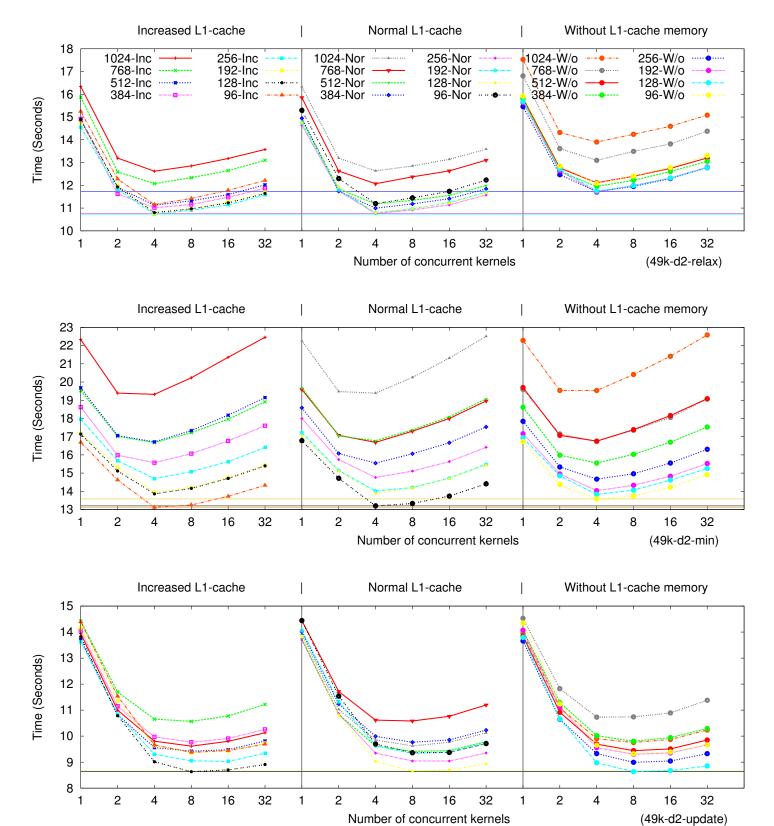

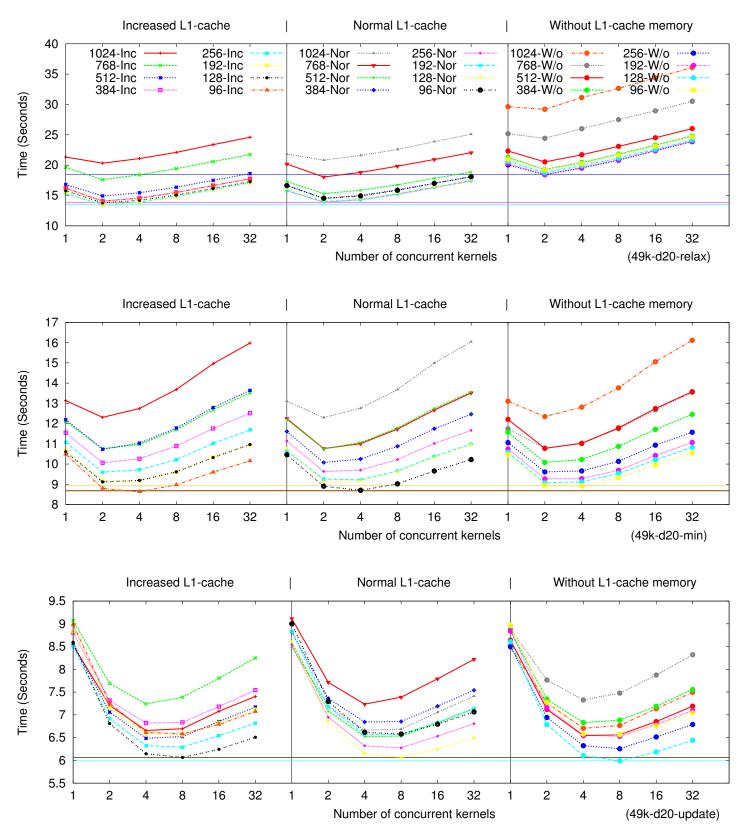

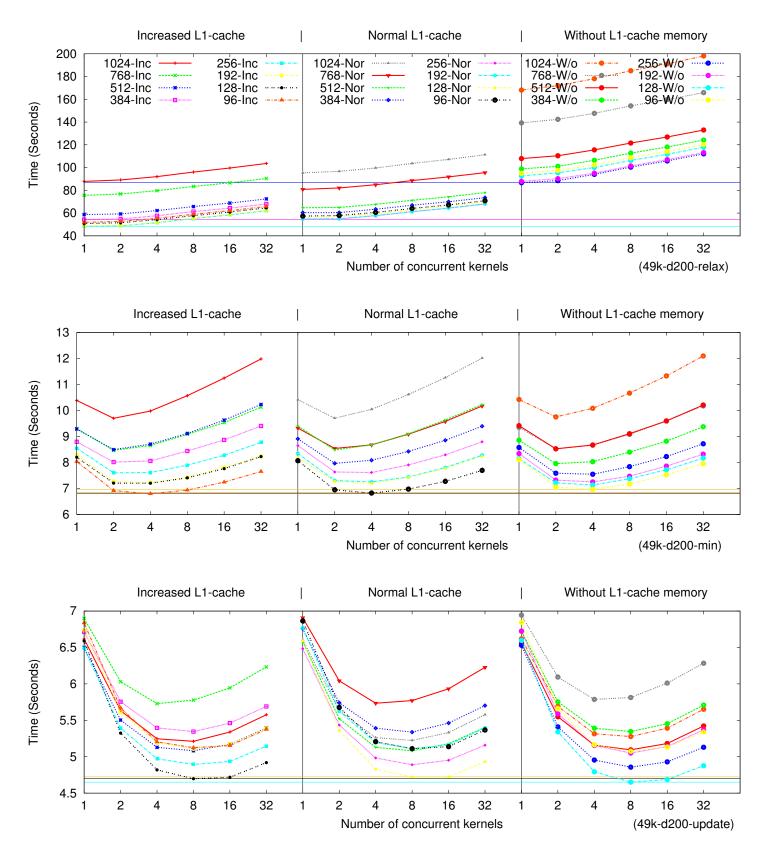

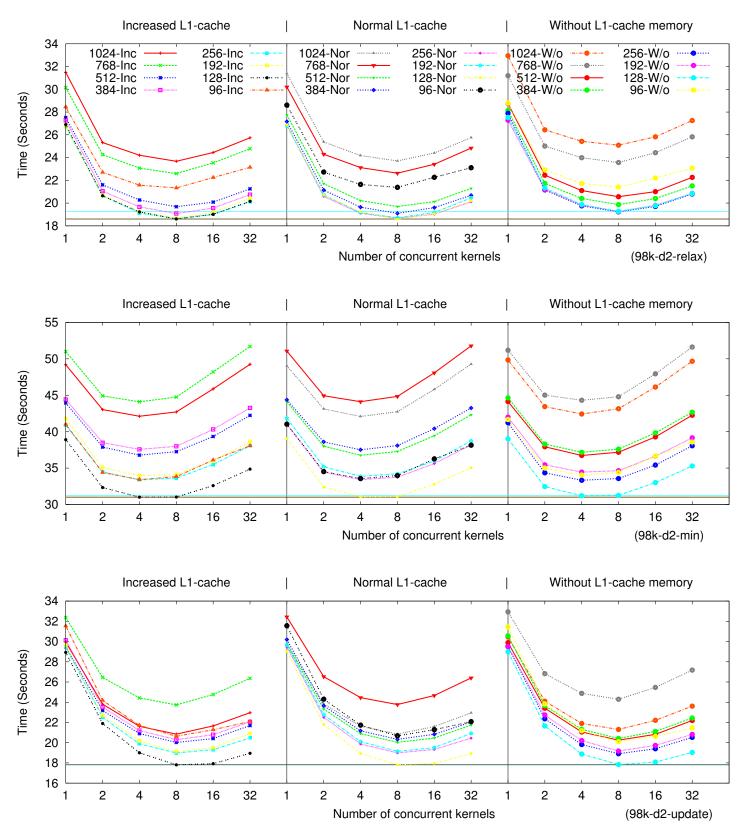

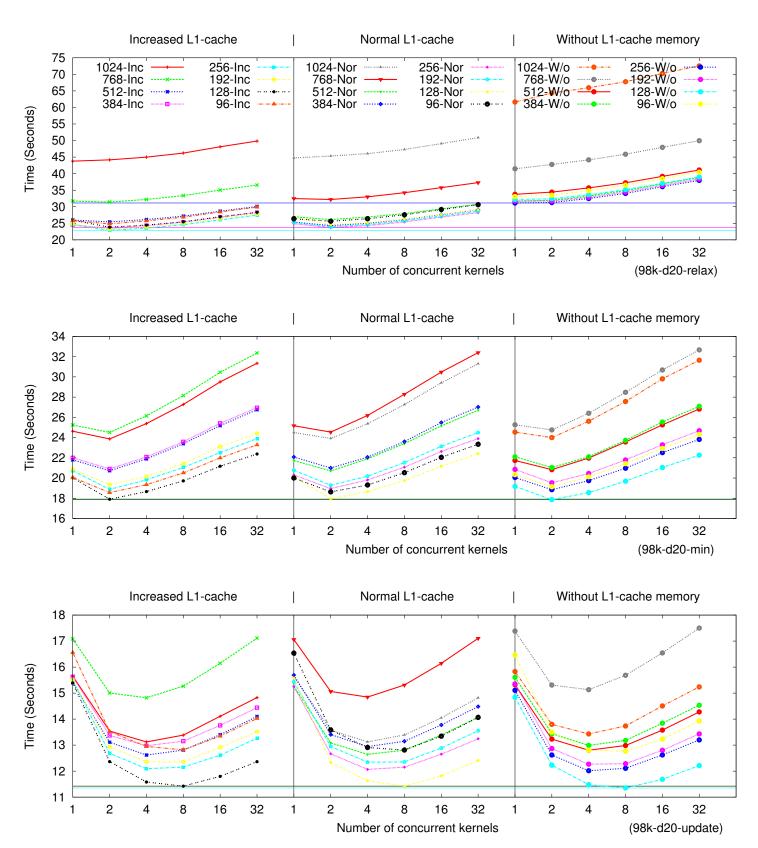

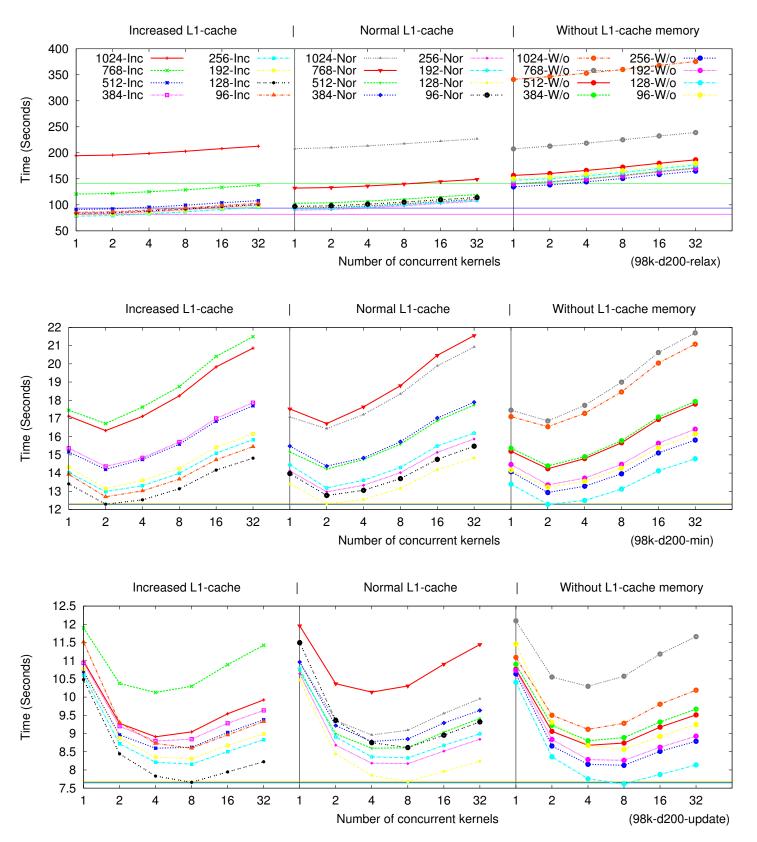

| 4.1<br>4.2<br>4.3                                                          | Exhaustive search for optimal values in the graph 24k-d2 scenario Exhaustive search for optimal values in the graph 98k-d200 scenario Execution time breakdown of the GPU kernels | 93<br>94<br>98                                                                                                                                                                                   |

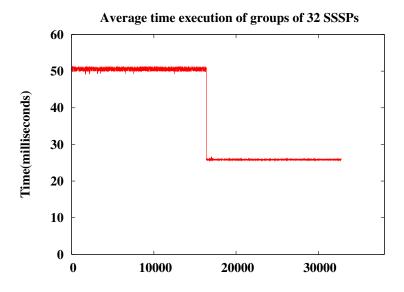

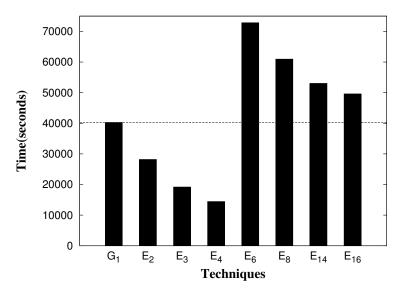

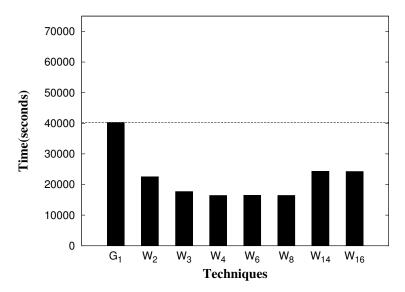

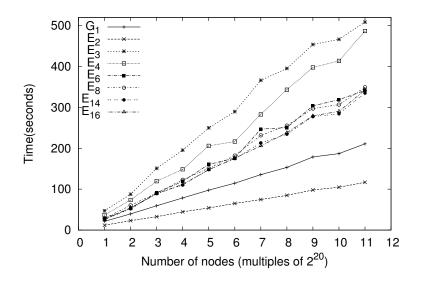

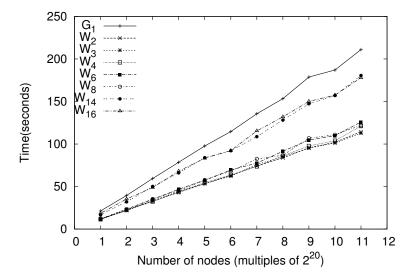

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6                                     | SSSP Execution time for different source nodes of the Martín graphs Execution times using the Equitable Scheduling policy                                                         | 108<br>109<br>110                                                                                                                                                                                |

| <ul><li>6.11</li><li>6.12</li><li>6.13</li><li>6.14</li><li>6.15</li></ul> | Some declaration examples for the automatic GPU kernel optimizations<br>Master/Slave function implementations                                                                     | <ol> <li>119</li> <li>119</li> <li>120</li> <li>122</li> <li>122</li> <li>124</li> <li>125</li> <li>126</li> <li>127</li> <li>128</li> <li>129</li> <li>129</li> <li>134</li> <li>134</li> </ol> |

| 7.1                                                                        | Subgoals accomplished in this Ph.D. thesis.                                                                                                                                       |                                                                                                                                                                                                  |

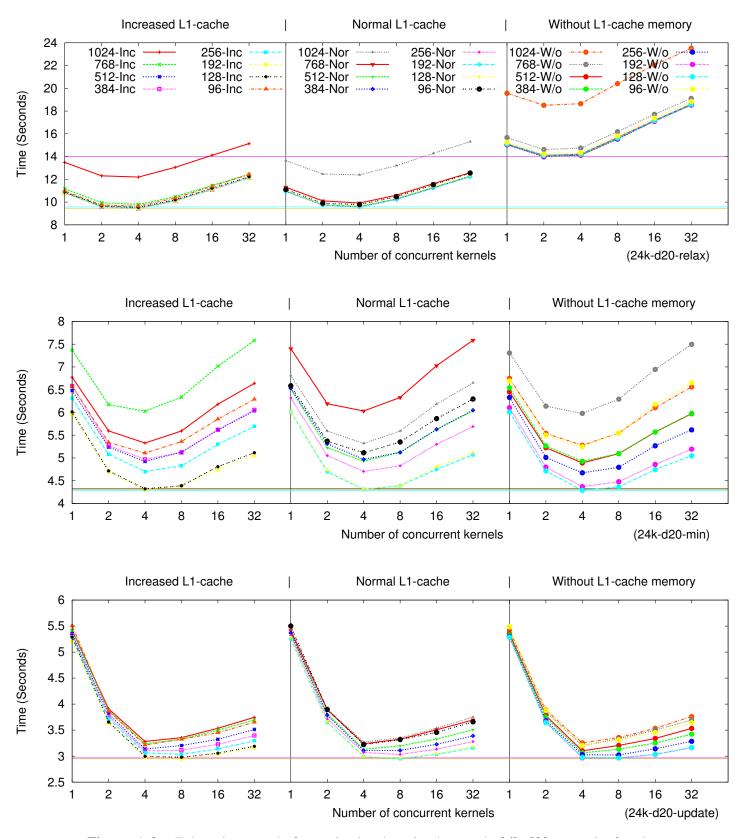

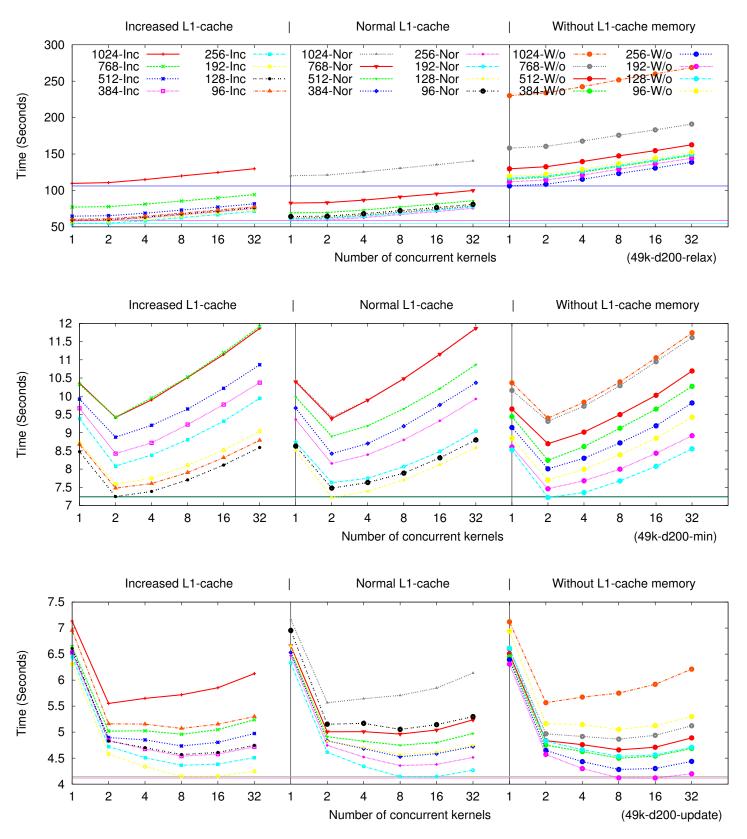

| A.1<br>A.2                                                                 | Exhaustive search for optimal values in the graph 24k-d20 scenario for                                                                                                            | 147<br>148                                                                                                                                                                                       |

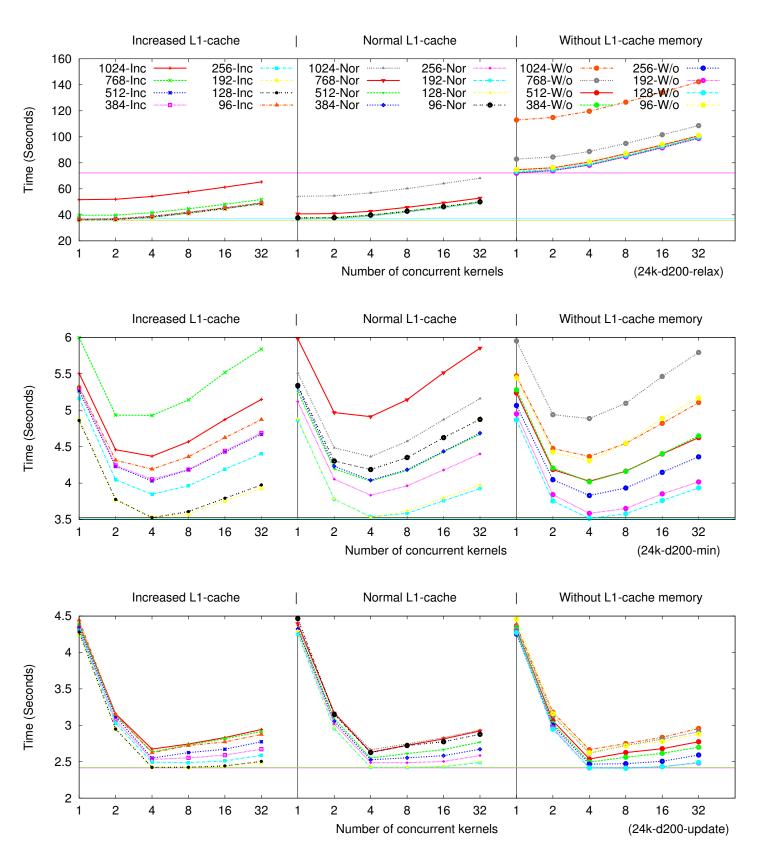

| A.3                                                                        | Exhaustive search for optimal values in the graph 24k-d200 scenario for                                                                                                           | 149                                                                                                                                                                                              |

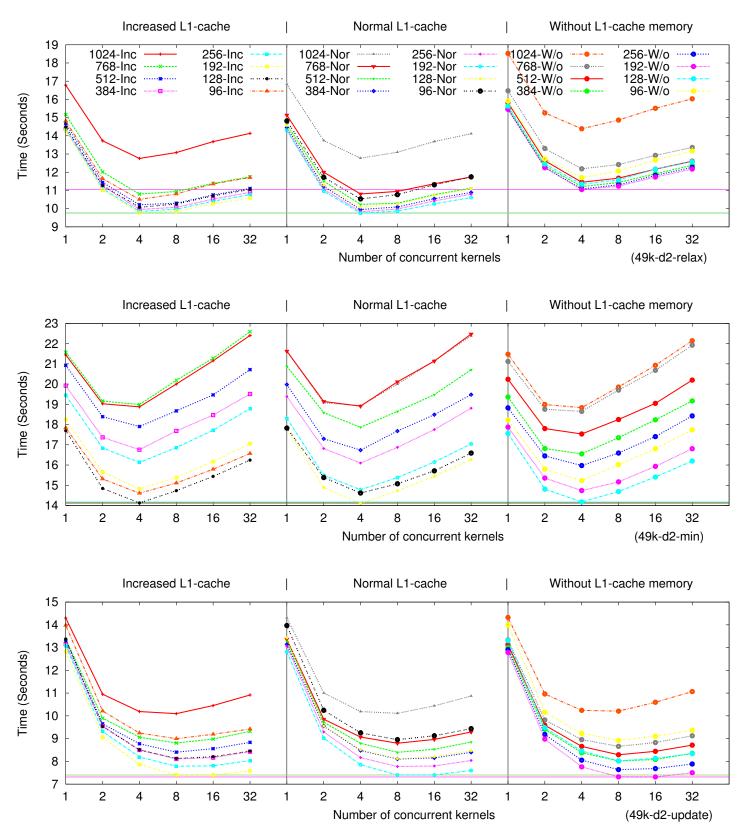

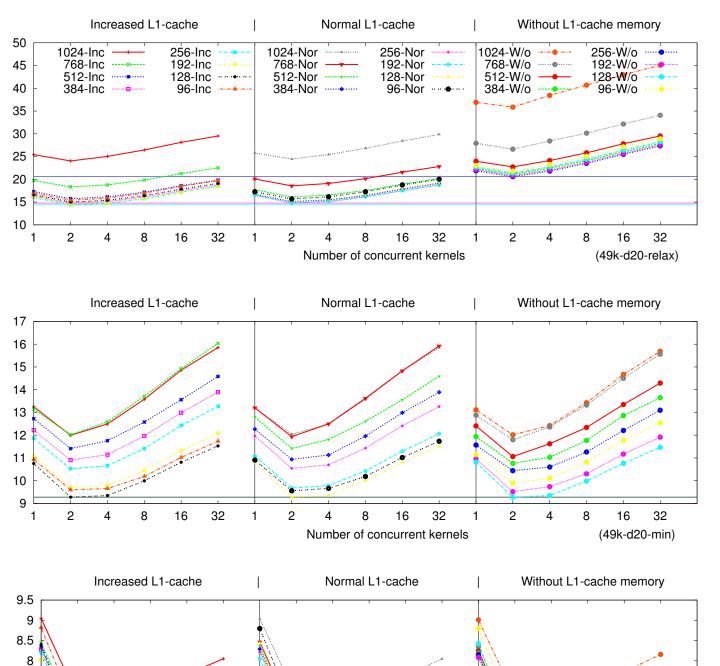

| A.4                                                                        |                                                                                                                                                                                   | 150                                                                                                                                                                                              |

| A.5                                                                        | Exhaustive search for optimal values in the graph 49k-d20 scenario for                                                                                                            | 151                                                                                                                                                                                              |

| A.6                                                                        | Exhaustive search for optimal values in the graph 49k-d200 scenario for the Fermi GF100 architecture.                                                                             | 152                                                                                                                                                                                              |

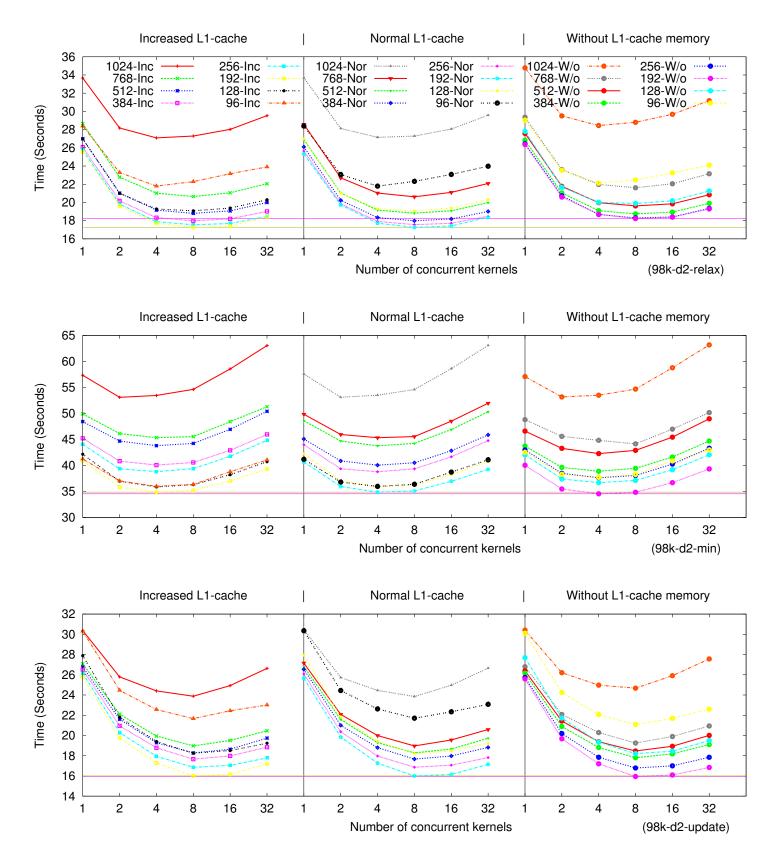

| A.7                                                                        | Exhaustive search for optimal values in the graph 98k-d2 scenario for the Fermi GF100 architecture.                                                                               | 153                                                                                                                                                                                              |

### LIST OF FIGURES

| A.8  | Exhaustive search for optimal values in the graph 98k-d20 scenario for    |     |

|------|---------------------------------------------------------------------------|-----|

|      | the Fermi GF100 architecture.                                             | 154 |

| A.9  | Exhaustive search for optimal values in the graph 98k-d200 scenario for   |     |

|      | the Fermi GF100 architecture.                                             | 155 |

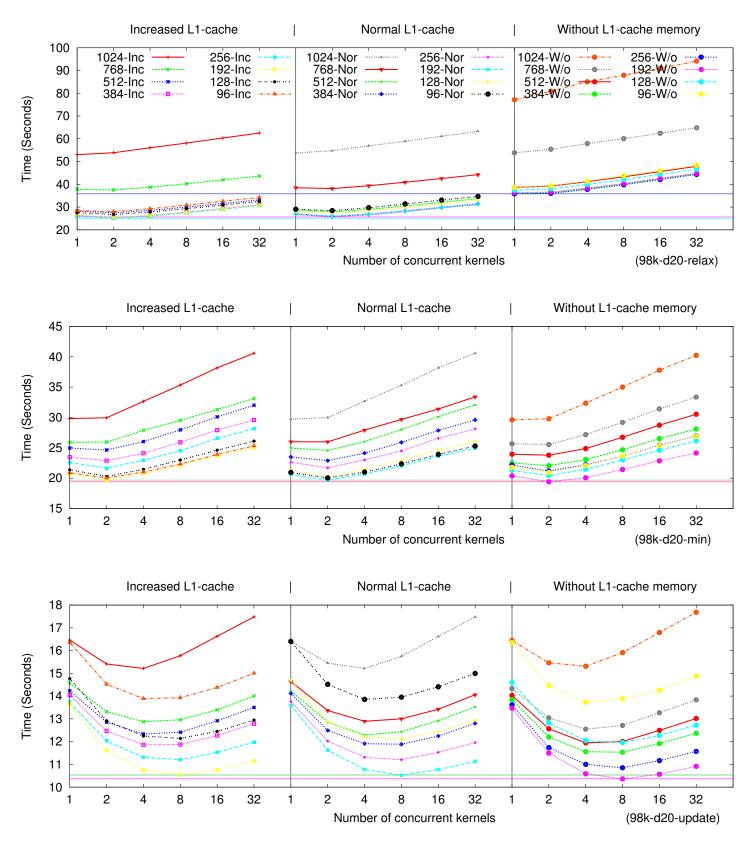

| A.10 | Exhaustive search for optimal values in the graph 24k-d2 scenario for the |     |

|      | Kepler GK104 architecture                                                 | 156 |

| A.11 | Exhaustive search for optimal values in the graph 24k-d20 scenario for    |     |

|      | the Kepler GK104 architecture                                             | 157 |

| A.12 | Exhaustive search for optimal values in the graph 24k-d200 scenario for   |     |

|      | the Kepler GK104 architecture                                             | 158 |

| A.13 | Exhaustive search for optimal values in the graph 49k-d2 scenario for the |     |

|      | Kepler GK104 architecture.                                                | 159 |

| A.14 | Exhaustive search for optimal values in the graph 49k-d20 scenario for    |     |

|      | the Kepler GK104 architecture.                                            | 160 |

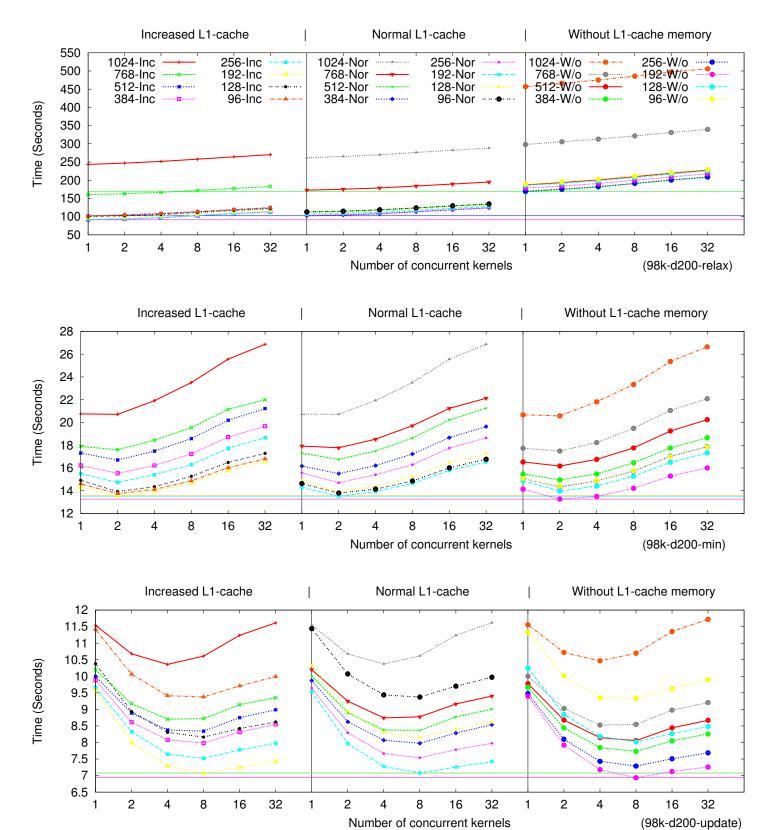

| A.15 | Exhaustive search for optimal values in the graph 49k-d200 scenario for   |     |

|      | the Kepler GK104 architecture.                                            | 161 |

| A.16 | Exhaustive search for optimal values in the graph 98k-d2 scenario for the |     |

|      | Kepler GK104 architecture.                                                | 162 |

| A.17 | Exhaustive search for optimal values in the graph 98k-d20 scenario for    |     |

|      | the Kepler GK104 architecture.                                            | 163 |

| A.18 | Exhaustive search for optimal values in the graph 98k-d200 scenario for   |     |

|      | the Kepler GK104 architecture.                                            | 164 |

$\mathbf{X}\mathbf{V}$

### LIST OF FIGURES

# List of Tables

| 2.1        | Best-bounds SSSP algorithms for different input graphs.                                                      | 27  |

|------------|--------------------------------------------------------------------------------------------------------------|-----|

| 2.2        | Parallel SSSP algorithm classification.                                                                      | 31  |

| 2.3        | Best time-complexity bounds of APSP algorithms for different graphs                                          | 36  |

| 2.4        | Time-bound evolution for FW-based algorithms.                                                                | 37  |

| 2.5        | Different existent implementations that parallelize the APSP problem                                         | 39  |

| 2.6        | Different parallel opportunities to parallelize the preprocessing phase                                      | 50  |

| 3.1        | Proper values selected for the threadblock-size and the L1 cache manage-<br>ment for the optimized version.  | 62  |

| 3.2        | Speedups of GPU Crauser vs. GPU Martín using synthetic random graphs.                                        | 68  |

| 3.3        | Best speedups of GPU Crauser vs. GPU Martín for each real-world family.                                      | 68  |

| 3.4        | Percentages of performance gain between GPU Crauser and its optimized version using synthetic random graphs. | 72  |

| 4.1        | Characterization of the <i>relax</i> , <i>minimum</i> and <i>update</i> kernels                              | 88  |

| 4.2        | Prediction values resulting from the kernel characterization process.                                        | 88  |

| 4.3        | Tested values in our experimental scenario for the different configuration                                   |     |

|            | parameters                                                                                                   | 91  |

| 4.4        | Best configuration parameter values and performance gain obtained com-                                       | ~-  |

|            | pared with the baseline                                                                                      | 97  |

| 5.1        | Experimental instances used on the shared-memory system                                                      | 106 |

| 6.1<br>6.2 | TuCCompi kernel-characterization classification                                                              |     |

| A.1        | Figure links for all graph scenarios considered.                                                             | 145 |

### LIST OF TABLES

xviii

# List of Algorithms

| 1  | The generic label-correcting algorithm                             | 28 |

|----|--------------------------------------------------------------------|----|

| 2  | The dynamic programming Floyd-Warshall algorithm.                  | 37 |

| 3  | Pseudo-code for the naïve parallel Floyd-Warshall algorithm        | 39 |

| 4  | Pseudo-code for recursive parallel APSP algorithm of Buluç         | 41 |

| 5  | Pseudo-code of Martín's GPU implementation for Dijktra's algorithm | 54 |

| 6  | Pseudo-code of the <i>relax kernel</i>                             | 55 |

| 7  | Pseudo-code of the <i>update kernel</i>                            | 55 |

| 8  | Pseudo-code of the <i>relax kernel</i> in Predecessors variant     | 56 |

| 9  | Pseudo-code of our Crauser minimum kernel.                         | 59 |

| 10 | Pseudo-code of our Crauser update kernel                           | 59 |

### LIST OF ALGORITHMS

# Chapter R

### Resumen de la tesis

Muchos problemas que surgen en las redes del mundo real requieren calcular los caminos más cortos, y sus distancias, entre uno o varios puntos de origen a uno o varios puntos de destino. Existen diferentes variantes del problema. El problema del SSSP, o Single-Source Shortest-Path, tiene como objetivo calcular los caminos más cortos y sus distancias entre un punto origen y el resto. Por otro lado, el problema del APSP, o All-Pair Shortest-Path, tiene como objetivo calcular los caminos más cortos y sus distancias entre cualquier par de puntos de la red. Algunos ejemplos de contextos donde este tipo de cómputo es necesario son los sistemas de navegación [1], simulaciones de tráfico [2], medios de transporte con horario fijo [3], control logístico [4], bases de datos espaciales [5, 6], planificación de rutas en Internet [7], o búsquedas en la web [8, 9]. A pesar de la importancia del problema de cálculo de caminos más cortos, los algoritmos actuales son aún muy costosos en términos computacionales, y en muchos casos los productos comerciales implementan abortamientos heurísticos para generar soluciones aproximadas en vez de soluciones óptimas.

El objetivo de paralelizar estos algoritmos implica no sólo la inmediata reducción de los tiempos de ejecución sino también su aplicación en otros planteamientos más complejos donde estos algoritmos representan una fase dentro del método global. De esta manera, estos métodos, que previamente eran sólo teóricos debido a prohibitivos tiempos de ejecución, pueden ser ahora factibles y viables gracias a esta reducción. Un ejemplo de este tipo de fases son los costosos preprocesos necesarios para ejecutar consultas en el cálculo de rutas de un mapa de carreteras. En este preproceso se obtienen valores que son almacenados para ser utilizados a posteriori en la consulta, donde se pide calcular la ruta más corta entre dos puntos del mapa. Normalmente, este preproceso tiene un coste muy alto en términos temporales, pero mientras sólo haya que ejecutarlo una vez cada mucho tiempo, podría considerarse como una tarea de coste asequible. Gracias a estos valores precomputados, que en ocasiones representan el cálculo de todas las distancias de todas las parejas de puntos de la red, la fase de consulta puede ser computada en el orden de nanosegundos [10, 11].

La configuración de los mapas de carreteras no cambia frecuentemente, por lo que podría ser plausible pagar el alto coste de la fase de preproceso una vez. Sin embargo, en otros contextos donde las redes tienden a cambiar con más frecuencia, o su topología es desconocida en un momento determinado, la reducción de tiempos de esta fase de preproceso se convierte en algo crucial. Además, en el contexto de los mapas de carreteras, podemos encontrar también este comportamiento dinámico si queremos tener en cuenta otros factores en tiempo real como pueden ser el estado de las carreteras o el tráfico.

La aparición de los dispositivos móviles presenta un tercer desafío debido a su poca capacidad de almacenamiento que limita la cantidad de datos precomputados que podríamos almacenar. La mayoría de los métodos actuales son más rápidos cuanta más datos precomputados puedan almacenar. Sin embargo, los dispositivos móviles actuales tienen una gran capacidad de cómputo incorporando varios procesadores cuyo explotación en paralelo podría aliviar la mencionada falta de almacenamiento.

La computación paralela consiste en utilizar a la vez dos o más dispositivos para realizar cálculos, normalmente con el propósito de reducir los tiempos de ejecución. Aunque la paralelización de un algoritmo no reduce su tiempo asintótico, a veces es la única manera de conseguir tiempos de ejecución razonables y/o competitivos. La tendencia de los ordenadores actuales es incorporan un mayor número de procesadores en vez de un único procesador con mucha velocidad de cómputo. Esta evolución ha derivado en la creación de tipos diferentes de dispositivos de cómputo: los sistemas multi-core y los sistemas many-core. Los primeros incluyen dos o más núcleos de procesamiento, o cores, que son de propósito general dentro de un mismo chip. Sin embargo, un sistema es considerado many-core, cuando tiene más de una docena de estas unidades de procesamiento. En esta categoría podemos encontrar no sólo superordenadores con un gran número de CPUs con muchos cores, sino también los aceleradores hardware como los procesadores gráficos (GPUs) o los coprocesadores como los dispositivos Xeon-Phi.

Actualmente, los dispositivos con arquitectura many-core más representativos son las GPUs [12]. Estos están diseñados para ayudar a la CPU en el procesamiento de gráficos. Sin embargo, debido sus altas capacidades computacionales han hecho que se utilicen para otro tipo de propósitos de ámbito general. Con el fin de facilitar este tipo de programación, NVIDIA desarrolló un nuevo modelo de programación, llamado CUDA [13], en 2007. Desde entonces muchas soluciones sofisticadas y eficientes se han desarrollado para diferentes aplicaciones y problemas [14].

Gracias a este modelo de programación es posible desarrollar fácilmente soluciones básicas para GPUs que obtienen mejoras en el rendimiento. En contraposición, obtener una optimizar la explotación de los recursos computacionales es una tarea difícil. Se necesita conocer en profundidad muchos de los detalles relacionados con la arquitectura de estos dispositivos y su correspondiente gestión, para poder predecir su comportamiento. Esta responsabilidad recae de manera directa sobre los propios programadores, que han de proveer varios valores para los parámetros de ejecución de las GPUs, como por ejemplo el tamaño y forma de los bloques de hilos, o el estado/tamaño de la memoria cache de primer nivel, entre otros. Las guías de programación que ofrece CUDA sugieren el uso de determinados valores para obtener buenos rendimientos. Sin embargo, algunos estudios [15, 16] han demostrado que en algunos estas recomendaciones no siempre devuelven rendimientos óptimos, obligando a los programadores a realizar test de prueba-y-error para encontrar los valores que se ajustan a los mejores rendimientos.

Dentro de la computación paralela se encuentra la computación heterogénea [17, 18], que se refiere al uso de sistemas o entornos de computación que están compuestas por unidades de procesamiento de diferente naturaleza. Algunos ejemplos clásicos son los

convencionales sistemas de memoria compartida o distribuida que contienen multi-core CPUs junto con dispositivos many-core como las GPUs. Una de las principales ventajas de usar este paradigma de computación, a diferencia del modelo homogéneo, es la posibilidad de asignar un tipo particular de tareas/funciones a aquellos dispositivos computacionales que mejor se ajusten a los requisitos de procesamientos de esas tareas. Otra ventaja, es la posibilidad de aprovechar cualquier unidad computacional presente dentro del sistema heterogéneo, aunque sus características no se ajusten perfectamente para la realización óptima de un trabajo específico, siempre y cuándo podamos ahorrar tiempo de la ejecución global de tareas.

Sin embargo, la programación de este tipo de entornos heterogéneos resulta bastante difícil comparado con la programación de entornos homogéneos. El programador debe conocer los diferentes modelos y lenguajes de programación necesarios para aprovechar los diferentes recursos computacionales, sus limitaciones y particularidades, para proveer diferentes implementaciones dependiendo de la plataforma donde se vaya a ejecutar. Además el programador ha de conocer qué tipo de tareas se ajusta mejor a qué dispositivo para obtener un mejor rendimiento y cuánto trabajo ha de asignar a cada uno. Todos estos problemas hacen que la programación sobre sistemas heterogéneos sea casi el resultado de un trabajo artesanal en el que hay que invertir mucho tiempo y esfuerzo debido a la falta de modelos de programación de propósito general que puedan lidiar con este tipo de complejidad de una manera transparente.

### **R.1** Pregunta de Investigación

La identificación de los problemas expuestos en la anterior sección, nos conduce a la siguiente pregunta de investigación, que se resuelve en esta Tesis Doctoral:

¿Es posible desarrollar técnicas y herramientas para conseguir implementaciones más eficientes que resuelvan problemas relacionados con el cálculo de caminos más cortos utilizando: (1) los modernos dispositivos de procesamiento de gráficos (GPUs), y su optimización mediante técnicas de ajuste de los parámetros correspondientes, (2) entornos heterogéneos compuestos por este tipo de aceleradores hardware en conjunto con el uso de las tradicionales CPUs?

### **R.1.1** Metodología de Investigación

La metodología de investigación llevada a cabo en esta tesis doctoral está basada en el método de la ingeniería de software que se compone de las cuatro siguientes fases: Observar las soluciones existentes; proponer mejores soluciones; desarrollar las soluciones propuestas; y medir y analizar los resultados [19]. Se trata de una metodología iterativa que puede ser repetida para refinar las soluciones propuestas. Esta metodología se parece al clásico método científico: Proponer una pregunta; formular una hipótesis; realizar una predicción; y validar la hipótesis.

1. Observar las soluciones existentes. Esta etapa de exploración tiene el propósito de encontrar problemas/limitaciones que serán abordados durante el proceso de inves-

tigación, y de detectar posibles mejoras y/o nuevas soluciones aún no contempladas. Esto conlleva un completo estudio del estado del arte con el objetivo de encontrar trabajos relacionados con nuestra investigación.

- 2. *Proponer mejores soluciones*. En esta etapa se realiza el análisis y diseño necesarios para abordar los límites o aprovechar las posibles mejoras encontradas en el paso anterior.

- 3. *Desarrollar las soluciones propuestas*. La metodología de esta fase consiste en el desarrollo o construcción de un prototipo de la solución que demuestre que el planteamiento propuesto es factible.

- 4. *Medir y analizar la nueva solución*. En esta última fase de la metodología, las implementaciones de los prototipos de las soluciones son evaluados a través de un estudio experimental. El objetivo de este estudio es corroborar si estas soluciones realmente resuelven los problemas descubiertos en la primera etapa.

### **R.2** Objetivos

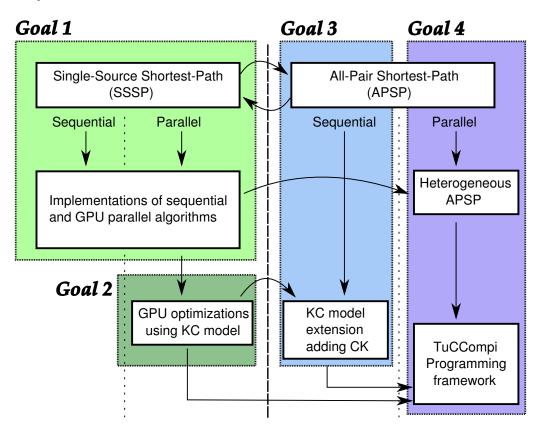

Para poder responder a la pregunta de investigación propuesta, hemos realizado las tareas que se describen a continuación (ver Fig. R.1). Se han aplicado las diferentes etapas de la metodología descrita anteriormente para cada una de ellas.

### Objetivo 1: Desarrollar un planteamiento nuevo para el problema del SSSP.

- (Observación) Se ha realizado un completo estudio del trabajo previo, visitando tanto las soluciones secuenciales como sus variantes paralelas para el problema del SSSP.

Después de este análisis, el foco de la investigación se centrará sobre los algoritmos para un tipo de grafo en particular, grafos no densos.

- (Propuesta y) desarrollo) Combinando diferentes ideas de la literature, un nuevo algoritmo para GPUs será propuesto. Implementaremos este algoritmo utilizando CUDA para poder optimizarlo y ejecutarlo sobre GPUs de NVIDIA.

- (*Medidas*) La viabilidad de nuestra propuesta será evaluada comparándola con el último algoritmo del estado-del-arte para GPUs, y también con una versión secuencial optimizada de referencia, usando un conjunto de grafos sintéticos y de redes reales como benchmarks. Para ambos casos se espera que la nueva propuesta obtenga mejores rendimientos.

### Objetivo 2: Optimizar nuestra implementación con apropiado ajuste de los parámetros de ejecución de las GPUs.

(*Observación*) El despliegue en las GPUs de las implementaciones desarrolladas requiere la elección de muchos valores para ciertos parámetros de ejecución, como son por ejemplo, el tamaño de los bloques de hilos, o la activación de la memoria

#### R.2. Objetivos

Figure R.1: Diferentes objetivos propuestos para el desarrollo de esta tesis doctoral.

caché de primer nivel, entre otros. Su adecuado ajuste, o tuneado, puede conllevar a importantes mejoras de rendimiento. Se debe revisar el estado-del-arte en busca de algún tipo de estudios o guías de tuneado que ayuden al programador con estas importantes decisiones que sirven para mejorar la solución propuesta.

(Propuesta y) desarrollo) Debemos encontrar un modelo que provea de guías o pasos a seguir para poder ajustar de manera adecuada nuestra solución. Idealmente, ese modelo debería basarse en las características de los códigos que se ejecutan en la GPU, lo que se conoce como caracterización de los kernels (KC). Después de proveer al modelo con esta caracterización, éste debería recomendarnos cuáles son los valores que nos permitirán ejecutar nuestros kernels con un rendimiento óptimo o cerca del óptimo.

(*Medidas*) Llevaremos a cabo experimentos que usen ambas versiones, tuneado y sin tunear, con el fin de comprobar si este proceso de predicción de valores es útil.

# **Objetivo 3: Resolver el problema del APSP usando funcionalidades nuevas de las GPUs modernas, y extender el modelo de caracterización de kernels con ellas.**

(Observación) Se ha realizado un completo estudio del trabajo previo, visitando tanto las soluciones secuenciales como sus variantes paralelas para el problema del APSP. Después de este análisis, el foco de la investigación se centrará sobre planteamientos basados en paralelización por productividad. Una de las nuevas características que poseen las GPUs modernas es la capacidad de ejecutar varios kernels independientes a la vez, siempre y cuando haya recursos que no estén siendo utilizados en ese momento. Realizar un estudio de esta funcionalidad y su comportamiento nos permitirá entender mejor cómo funciona esta característica, aprovecharla para mejorar nuestros planteamientos, y ver si afecta al resto de parámetros de ejecución de las GPUs.

- $\binom{Propuesta\ y}{desarrollo}$  Modificaremos nuestra solución del SSSP para que incluya la ejecución concurrente de kernels. Esta técnica nos permitirá resolver el problema del APSP a través del método basado en productividad conocido como  $n \times SSSP$ , donde se ejecuta cada SSSP con un nodo origen diferente de manera independientemente. Refinaremos un modelo de caracterización de kernels ya existente [16], considerando no sólo la nueva funcionalidad de la ejecución concurrente de kernels, sino también para que tenga en cuenta algunas de las características de los grafos de entrada.

- (*Medidas*) Llevaremos a cabo un completo conjunto de estudios sobre diferentes arquitecturas de las GPUs para verificar, no sólo la correctitud de la nueva solución que resuelve el APSP, sino también la validez de los valores del nuevo modelo.

### **Objetivo 4: Explorar la explotación de entornos heterogéneos para resolver el problema del APSP.**

- (*Observación*) Durante el anterior exploración de la literatura del problema del APSP no se encontraron no se encontraron estudios que combinaran algoritmos paralelos con métodos basados en productividad paralela.

- (*Propuesta y*) Proponemos combinar ambas versiones de un algoritmo SSSP, secuencial y paralela para GPUs, en la misma implementación para resolver el APSP. De esta manera podemos aprovechar todo tipo de unidades computacionales de diferente naturaleza presentes en un mismo sistema de computación, asignando la versión secuencial a cada CPU core, y la versión paralela a cada GPU disponible. Además, implementaremos diferentes políticas de distribución de carga.

Por último queremos crear un nuevo modelo de programación que incorpore este novedoso planteamiento, y que además combine la obtención de valores adecuados para los parámetros de ejecución a través de la caracterización de los kernels. Por lo tanto, desarrollaremos un prototipo para este framework de programación que integre todas estas contribuciones descritas anteriormente.

(*Medidas*) Llevaremos a cabo diferentes experimentos que usen grafos con diferentes características, y diferentes técnicas de distribución de carga, con el objetivo de evaluar la eficiencia del nuevo planteamiento en contraposición al tradicional uso de un único dispositivo de cómputo. Por último, probaremos el prototipo resolviendo el problema del APSP en diferentes clústers heterogéneos.

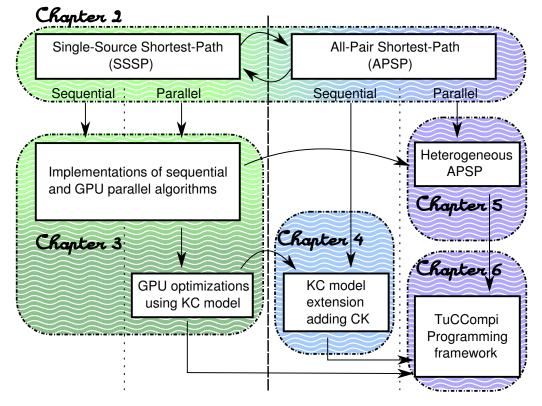

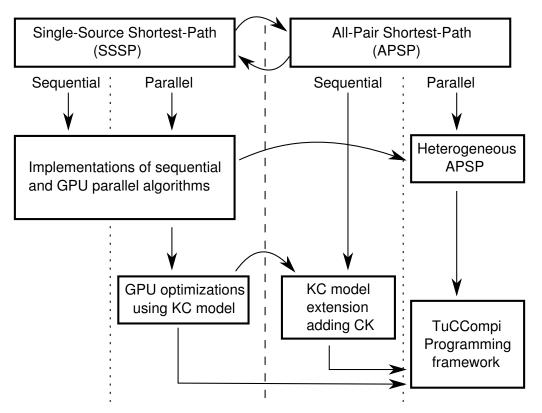

Figure R.2: Estructura del documento.

### **R.3** Estructura de la Tesis

Este documento está organizado de la siguiente manera (ver Fig. R.2). El capítulo 2 presenta un estudio del estado del arte de los algoritmos secuenciales y paralelos que resuelven los problemas del SSSP y del APSP, y un ejemplo de aplicación al mundo real de estos métodos. El capítulo 3 describe en profundidad el último algoritmo del estado del arte para GPUs que resuelve el problema del SSSP, y nuestra nueva implementación junto con una versión optimizada. El capítulo 4 introduce una extensión de un modelo que utiliza la caracterización de los kernels para predecir los valores óptimos de los parámetros de ejecución de las GPUs. El capítulo 5 presenta una solución para el problema del APSP que combina el uso de algoritmos paralelos diseñados para GPUs junto con algoritmos secuenciales, a través de métodos de productividad paralelos diseñados para un sistema heterogéneo. Además, presenta el uso de diferentes técnicas de balanceo de carga para este problema. El capítulo 6 describe un modelo de programación que simplifica la programación de sistemas heterogéneos que incluyen aceleradores hardware porque el modelo se encarga automáticamente de esconder los detalles de sincronización, despliegue y ajuste de estos dispositivos. Por último, el capítulo 7 contiene las conclusiones de esta tesis de doctorado, enumera las contribuciones que aporta y las publicaciones surgidas de este trabajo.

### **R.3.1** Síntesis de Capítulos y Contribuciones

En esta sección se describe una síntesis de los contenidos que se muestran a lo largo de esta tesis doctoral junto con los resultados y las contribuciones obtenidas. Además se enumeran los artículos publicados que recogen el trabajo de cada uno de ellos.

### Capítulo 2: Estado del arte de los problemas de caminos más cortos

El objetivo de este tipo de problemas está relacionado con el cálculo de los caminos más cortos, y sus distancias, entre los diferentes nodos de un grafo. Dependiendo de que solución particular sea necesaria calcular, podemos identificar diferentes variantes de estos problemas. El problema del SSSP (Single-Source Shortest-Path) tiene como objetivo calcular todos los caminos más cortos entre un origen específico y el resto de nodos del grafo. Una extensión de este problema, la variante APSP (All-Pair Shortest-Path), tiene como objetivo calcular todos los caminos más cortos de todas las posibles parejas de nodos del grafo. Además, existen más derivaciones de este tipo de problemas, como por ejemplo el cálculo de un caminos entre una única pareja de nodos, entre un subconjunto de nodos a otro subconjunto, o incluso, de un subconjunto de nodos al resto del grafo. Las mejoras hechas sobre las variantes más generales (SSSP y APSP) normalmente pueden ser aplicadas sobre estos planteamientos derivados. Este capítulo de esta tesis se centra en el estudio de los algoritmos, secuenciales y paralelos, de estas variantes más generales.

El trabajo presentado incluye nuevas clasificaciones para los planteamientos paralelos en función de sus características, y hemos localizado algunas soluciones que no han sido exploradas que han sido el objetivo de estudio de esta tesis. Estos estudios han sido publicados en los siguientes artículos:

- "Parallel Approaches to the Shortest Path Problem A Survey," H. Ortega-Arranz, Y. Torres, D. R. Llanos, and A. Gonzalez-Escribano, *To be submitted to ACM Computing Surveys*

- "The Shortest Path Problem: Analysis and Comparison of Methods," H. Ortega-Arranz, D. R. Llanos, A. Gonzalez-Escribano, *Book*, 1st edition, ser.(Synthesis Lectures on Theoretical Computer Science series), Morgan & Claypool. Online, DOI: 0.2200/S00618ED1V01Y201412TCS001 [20]

# Capítulo 3: Un nuevo planteamiento para resolver el problema del SSSP usando GPUs

La alta capacidad de cómputo de los aceleradores hardware ha hecho que se dispare su explotación para obtener programas más rápidos. La programación de estos dispositivos se ha simplificado gracias a la aparición de lenguajes paralelos de alto nivel, como es el ejemplo de CUDA [21]. La aplicación de estos dispositivos para obtener mejoras dentro del contexto de los problemas de cálculo de caminos más cortos ha incrementado considerablemente durante los últimos años. Algunos ejemplos de estas implementaciones para las GPUs podemos encontrarlos en los trabajos de [22, 23], donde se utilizan modificaciones del algoritmo de Dijkstra.

#### R.3. Estructura de la Tesis

Este capítulo presenta una nueva solución, basada en el algoritmo de Crauser [24], para resolver el problema del SSSP utilizando las GPUs. Esta solución supera al anterior planteamiento del estado del arte, propuesto por Martín *et al.* [23], en todas las familias de grafos evaluadas. Estas familias incluyen no sólo los grafos utilizados en sus propias experimentaciones, sino también casos de redes existentes en el mundo real. Utilizando los mismos valores para los parámetros de ejecución de las GPUs para ambas propuestas, nuestra solución funciona hasta 45 veces más rápido.

También hemos conseguido mejorar el tiempo de ejecución a través de un adecuado ajuste/tuning de los parámetros de ejecución particulares de los dispositivos GPU de NVIDIA, obteniendo hasta un 22.43% de mejora cuando se compara con la versión no ajustada/tuneada. Esta versión no tuneada utiliza los valores originales seleccionados por Martín *et al.* en su estudio. Además, hemos comparado nuestra versión mejorada con la versión secuencial optimizada procedente de la librería especializada en grafos Boost [25]. Nuestra versión funciona hasta 19 veces más rápido para algunas de las familias de grafos utilizadas consumiendo hasta 11.25 veces menos memoria.

Finalmente, también hemos realizado un estudio de las diferentes arquitecturas de los dispositivos GPUs de NVIDIA en función de las características del grafo a computar, dentro del contexto del problema del SSSP. Los resultados muestran como unas arquitecturas funcionan mejor en unos tipos de grafos, existiendo diferencias de hasta un 40.5% en los tiempos de ejecución.

El trabajo descrito se ha publicado en los siguientes artículos:

- "Comprehensive Evaluation of a New GPU-based Approach to the Shortest Path Problem," H. Ortega-Arranz, Y. Torres, A. Gonzalez-Escribano, and D. R. Llanos, *International Journal of Parallel Programming*, Springer, p. 1–21, 2015. Online, DOI: 10.1007/s10766-015-0351-z [26]

- "A New GPU-based Approach to the Shortest Path Problem," H. Ortega-Arranz, Y. Torres, D. R. Llanos, and A. Gonzalez-Escribano, in *Proceedings of the 11th International Conference on High Performance Computing and Simulation*, ser.(HPCS'13), Helsinky, Finland: IEEE, 2013, pp. 505–511. Online, DOI: 10.1109/HPCSim.2013.6641461 [27].

### Capítulo 4: Uso y extensión de un modelo para predecir configuraciones óptimas para la GPU aplicado al problema del APSP

Conseguir una implementación altamente paralela para GPUs es un trabajo asequible. Sin embargo, la optimización de los códigos ejecutados en estos aceleradores hardware representa todo un desafío. La razón principal de esta dificultad es el gran número de combinaciones con las que se puede ejecutar el mismo programa: numerosos valores para los parámetros de ejecución, decisiones de programación, técnicas de ajuste disponibles, etc. Existe una estrategia para poder atacar estos problemas de optimización de un modo sistemático: la caracterización de los kernels que se ejecutan en la GPU. Con esta caracterización es posible obtener una apropiada configuración para obtener mejores tiempos de ejecución sistemáticamente. Este capítulo utiliza estos criterios de caracterización para ajustar la ejecución de nuestra implementación propuesta para resolver el problema del APSP. Esta implementación es una adaptación de nuestra solución del SSSP, propuesta en capítulo anterior, que resuelve el APSP a través del planteamiento por productividad  $n \times SSSP$ .

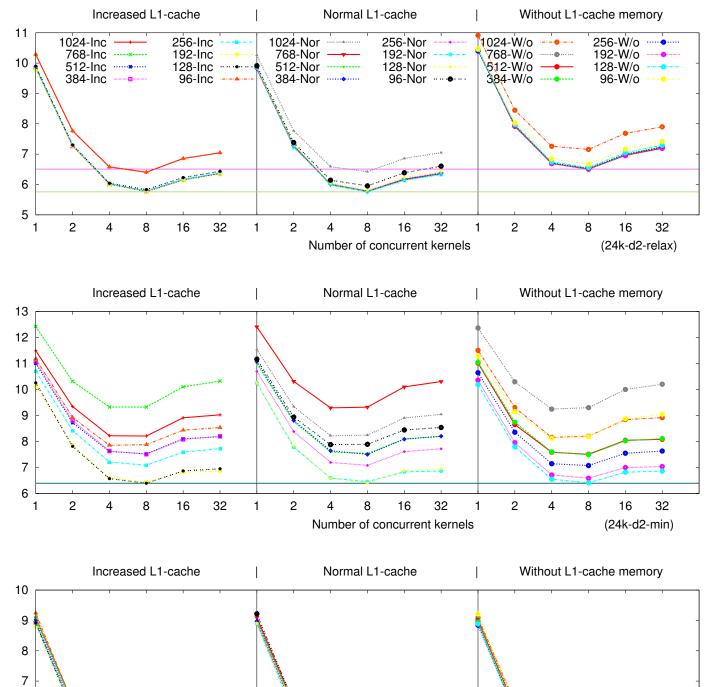

Hemos comprobado la validez del modelo de caracterización de kernels mediante una exhaustiva búsqueda en el espacio de soluciones, evaluando los valores más relevantes para los parámetros de ejecución de las GPUs de NVIDIA, y de las características de los grafos de entrada. También hemos evaluado su utilidad comparando los tiempos resultantes de utilizar la configuración predicha el modelo, con una de las configuraciones que sugiere la guía de programación de CUDA [21], obteniendo la primera una mejora de hasta un 62% con respecto a la segunda.

El trabajo descrito ha sido publicado en los siguientes artículos:

"Optimizing an APSP Implementation for NVIDIA GPUs Using Kernel Characterization Criteria", H. Ortega-Arranz, Y. Torres, A. Gonzalez-Escribano, and D. R. Llanos, *The Journal of Supercomputing*, Springer, vol. 70, no. 2, pp. 786-798, 2014.

Online, DOI: 10.1007/s11227-014-1212-z [28]

"A Tuned, Concurrent-Kernel Approach to Speed Up the APSP Problem," H. Ortega-Arranz, Y. Torres, D. R. Llanos, and A. Gonzalez-Escribano, in *Proceedings of the 13th International Conference on Computational and Mathematical Methods in Science and Engineering*, ser.(CMMSE'13), Almería, Spain: eds. I.P. Hamilton and J. Vigo-Aguilar, 2013, vol. 4, pp. 1114-1125. Online: CMMSE Proceedings [29]

### Capítulo 5: Uso de sistemas heterogéneos y diferentes políticas de balanceo de carga para resolver el problema del APSP

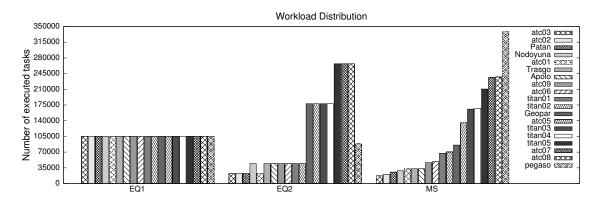

Este capítulo estudia soluciones para el problema del APSP en grafos dispersos que combina el uso de algoritmos paralelos diseñados para GPUs junto con algoritmos secuenciales, a través de métodos de productividad paralelos diseñados para un sistema heterogéneo. Además, se han aplicado dos diferentes políticas de balanceo de carga para distribuir las tareas entre las diferentes unidades computacionales (CPUs y GPUs). La primera política divide equitativamente el espacio de trabajo entre todas las unidades computacionales independientemente de su naturaleza o capacidad de procesamiento. La segunda política mantiene una cola de trabajo de donde cada unidad computacional adquiere una nueva tarea cada vez que termina la anterior.

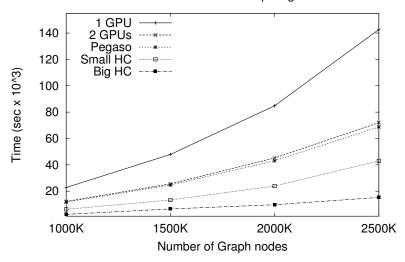

Hemos estudiado la importancia de este tipo de soluciones heterogéneas para grafos irregulares que dan lugar a dos tipos de tareas, pesadas y ligeras. Las tareas pesadas son procesadas más rápidamente por las GPUs que por las CPUs, mientras que con las tareas ligeras ocurre al revés. El primer estudio compara la resolución del APSP conociendo la distribución de la naturaleza de las tareas de los grafos para diferentes instancias de los dos tipos de políticas de distribución implementadas. El segundo estudio realiza la misma comparativa pero escogiendo tareas aleatorias para que la distribución sea desconocida. Se obtienen mejoras de algunas de las instancias heterogéneas de hasta un 65% y un 47%, para el primer y segundo estudio, comparado contra el uso de una única GPU

Los resultados también nos permiten concluir que el conocimiento de la naturaleza de los datos de entrada es muy importante porque permite al programador a asignar las tareas más costosas a los dispositivos con una mayor capacidad de cómputo. Esta información puede ser utilizada por las políticas equitativas para obtener los mejores tiempos de ejecución aunque su rendimiento se vería muy afectado por los cambios de la entrada. Por otro lado, las implementaciones que utilizan la cola de recuperación de trabajo tienen un rendimiento más estable porque son independientes de la naturaleza de los grafos de entrada.

El trabajo descrito ha sido publicado en los siguientes artículos:

"The All-Pair Shortest-Path Problem in Shared-Memory Heterogeneous Systems," H. Ortega-Arranz, Y. Torres, D. R. Llanos and A. Gonzalez-Escribano, in book *High-Performance Computing on Complex Environments*, ser. Series on Parallel and Distributed Computing. John Wiley & Sons, Inc., 2014, ch. 15, pp. 283-299. Online, DOI: 10.1002/9781118711897.ch15 [30]

### Capítulo 6: Desarrollo de un modelo de programación multi-capa

Durante la última década las arquitecturas de procesamiento paralelo se han convertido en una poderosa herramienta para enfrentarse a problemas masivamente paralelos, como el APSP. Como muestra el capítulo anterior, la combinación de unidades computacionales de diferente naturaleza es la solución más prometedora para este tipo de problemas que requieren soluciones de cómputo de altas prestaciones (HPC). Pero también se ha visto que maximizar el rendimiento de los dispositivos como las GPUs requiere un extenso conocimiento en detalle de la arquitectura subyacente de estos aceleradores, convirtiéndose en una tediosa tarea manual asequible sólo para programadores experimentados.

Este capítulo presenta a TuCCompi, un modelo abstracto multi-capa que simplifica la programación de entornos heterogéneos que incluyen GPUs. Este modelo detecta automáticamente los diferentes recursos presentes en el clúster híbrido y trata de maximizar su explotación seleccionado la configuración más adecuada para el caso de los dispositivos GPUs gracias a la caracterización de los kernels que provee el programador. También se presenta la descripción de un prototipo de este modelo, junto con su evaluación en diferentes entornos heterogéneos, usando el problema del APSP como caso de estudio.

El trabajo descrito ha sido publicado en los siguientes artículos:

- "TuCCompi: A Multi-Layer Model for Distributed Heterogeneous Computing with Tuning Capabilities," H. Ortega-Arranz, Y. Torres, A. Gonzalez-Escribano, and D. R. Llanos, *International Journal of Parallel Programming*, Springer, p. 1–22, 2015. Online, DOI: 10.1007/s10766-015-0349-6 [31]

- "TuCCompi: A Multi-Layer Programing Model for Heterogeneous Systems with Auto-Tuning Capabilities," H. Ortega-Arranz, Y. Torres, D. R. Llanos, and A. Gonzalez-Escribano, in *Proceedings of Workshop on High-level Programming for Heterogeneous and Hierarchical Parallel Systems*, ser.(HLPGPU'14), Vienna, Austria: HiPEAC 2014, pp. 18-25. Online: HLPGPU Proceedings [32]

### **R.4** Conclusiones

El trabajo presentado en esta tesis doctoral nos permite responder a las preguntas de investigación propuestas con una respuesta afirmativa

- (1) Gracias al estudio de la literatura sobre problemas de cálculo de caminos más cortos, hemos sido capaces de desarrollar una nueva solución paralela para el problema del SSSP, siguiendo las ideas propuestas por Crauser *et al.* [24], que es capaz de aprovechar la potente capacidad de cómputo de los dispositivos GPU. Esta implementación mejora el rendimiento de la anterior solución del estado-del-arte propuesta por Martín *et al.* [23]. Siguiendo las pautas propuestas en [28], hemos refinado el método de caracterización de kernels para obtener valores más adecuados para los parámetros de ejecución de las GPUs que conlleven a ejecuciones óptimas o cercanas al óptimo. La aplicación de esta metodología a nuestra implementación ha hecho que pudiéramos obtener valores más apropiados, que implicaron mejoras muy significativas en comparación con los valores recomendados por las guías de programación de CUDA [21].

- (2) La combinación de diferentes modelos y lenguajes de programación nos ha permitido realizar implementaciones y novedosos estudios de soluciones, que estaban sin explorar, dentro del contexto de planteamientos basados en productividad paralela para el problema del APSP. Estas implementaciones abordan el uso de nuevas características de las GPUs para ejecutar de manera concurrente flujos de kernels diferentes, resolviendo cada uno de estos flujos distintos subproblemas SSSP en paralelo. Por otro lado, el uso combinado de CUDA y OpenMP permitió a otras implementaciones explotar al mismo tiempo ambas unidades computacionales presentes en el mismo sistema de memoria compartida, las GPUs y los núcleos de las CPUs. Por último, hemos propuesto un modelo de programación multicapa, y hemos desarrollado su prototipo con el que es posible coordinar de manera transparente todo un clúster heterogéneo de unidades computacionales de diferente naturaleza, utilizando internamente diferentes tecnologías como CUDA, OpenMP y MPI. Todos los experimentos llevados a cabo para esta novedosa formulación heterogénea demostraron que su uso conlleva mejoras en los rendimientos muy significativas comparadas contra las versiones homogéneas.

l Chapter

### Introduction

### **1.1 Motivation**

Many problems that arise in real-world networks imply the computation of the shortest paths, and their distances, from a source to any destination point. Some examples include car navigation systems [1], traffic simulations [2], scheduled means of transport [3], logistic control [4], spatial databases [5, 6], Internet route planners [7], or web searching [8, 9]. Despite the importance of the shortest-path problem, algorithms to solve it are computationally costly, and in many cases commercial products implement heuristic approaches to generate approximate solutions instead. Although heuristics are usually faster and do not need much amount of data storage or precomputation, they do not guarantee the optimal route.

The aim of parallelizing these algorithms is, not only the immediate reduction of their execution time, but also their application in complex approaches, that use them as a step in their algorithms. In this way, this reduction makes their computation feasible where they were previously impracticable due to prohibitive temporal costs. An example related with the shortest-path context is the costly preprocessing phase of the modern methods and techniques used for routing in roadmaps. The preprocessing phase obtains values that will be stored and constantly used in later queries, where it is requested to calculate shortest paths, and their distances, between two vertices of the graphs. The preprocessing phase usually has costly execution times, but as long as it is going to be performed only once for long periods of time, it is an affordable cost. Thanks to these previous precomputed values, that in some cases, represent the calculation of shortest path distances between all vertices of the network, the query phase can be computed in the order of nanoseconds [10, 11].

The configuration of the roads of a map do not frequently change, so it could be plausible to pay the high temporal and spatial costs of computing these values once and store them. However, in other contexts, where this kind of static nature is not present in the network, or it is unknown, the reduction of these costs is highly significant. Additionally, in the previously mentioned context of route planning, the application of efficient parallel methods is compulsory if it is desired to take into account the current state of the roads in real-time, such as the information of the traffic, the road cuts due to maintenance or natural events, or even the avoidance of low-speed/bad-quality roads for a particular driver.

The advent of mobile devices present a third challenge because of their small memory size, that limits the amount of precomputed data that can be stored. Most of the current approaches present a trade-off between the amount of memory used and the query time needed: The more memory used, the better the query time. However, the new devices nowadays have bigger computational capabilities, incorporating several processors that could alleviate this mentioned lack of memory, and therefore, giving a chance to faster parallel approaches instead of storing the data obtained through costly preprocessing.

### **1.1.1 Parallel Computing**

Parallel computing, or also parallel processing, consists in using two or more devices for carrying out the computations at the same time, usually with the aim to reduce the high temporal costs needed in a single device. Although the application of parallel computing to complex problems does not lead to asymptotic-order reductions of the temporal costs of a problem, it frequently represents the only way to achieve solutions in competitive or reasonable execution times, and its use has proven to be critical when researching high performance solutions. Due to this fact, the evolution of computing not only has focused on developing faster processors, where the upper threshold of clock speeds is stalled for the moment, but also it has focused on the creation of new computer architectures involving more processing units, also improving the efficiency of the parallel computing. This architectural evolution has lead to two non-exclusive different trends, the multi-core and the many-core systems. Both have in common the huge increment of computational capabilities by the integration of several processing units.

The multi-core architecture refers to CPUs that contain two or more processing cores. These cores operate as separate all-purpose processors within a single chip. The use of multiple cores gets an increment of the total CPU performance without the need of raising the processor clock speed. Note that the concept of multiple cores is different than multiple CPUs. A multi-core computer can hold, for example, four cores on a single chip, whereas a multi-processor system may have four CPUs, each with only one core. Since the last trends favor energy savings, the high efficiency at low energy costs of these multi-core systems is imposing this architecture over the multi-processor architecture for domestic purposes. On the other hand, in academic or high performance contexts, the current machines combine both technologies, including multiple CPUs with multiple cores.

A system is considered as a many-core architecture when it has a number of processing units over dozens. However, with the fast increase of processing units of the computing systems, this value is subject to raise. In this category are included not only these supercomputers with a high number of CPUs with multiple cores, but also hardware accelerators, such as Graphics Processing Units (GPUs), or co-processors, such as the Xeon-Phi devices. Hardware accelerators are designed to integrate many specialized processing units to fulfill the need of processing high parallel applications in a high performance computing context.

Figure 1.1 shows a timeline evolution of the parallel computing from 1960, when the first supercomputing supporting this kind of computing was introduced, until these days, according to four different categories: Supercomputers, accelerators, mainstream

Figure 1.1: Evolution timeline of parallel computing.

Figure 1.2: Number of papers related with different parallel computing technologies.

computers, and mobile computing, according to [33]. In spite of this impressive raise of computational capabilities, it is still a difficult task for the programmers to create optimal parallel solutions. These modern systems require to correctly manage some new practical issues, such as the data partitioning, data sharing, data transfers, the coordination and synchronization, or the migration to new computing paradigms as the SIMD model for some many-core systems. However, although programming in these devices it is not trivial, their use in the research activities is significantly growing, with the GPUs as the device for parallel computing that generates more scientific interest nowadays. Figure 1.2 depicts the trends of the scientific interest taken as the number of papers published in the literature inside the parallel computing category. These values have been obtained using the IEEE Xplore XML Gateway API [34].

### **1.1.2 GPUs for Parallel Computing**

The most representative devices of the many-core architectures are the GPUs [12]. They were originally designed to help the CPU in processing the graphic data that will be display in the user's screen. However, due to their powerful computational capabilities, their use for different purposes became more popular, creating the trend of GPGPU (General-Purpose GPU) computing. In order to facilitate the programming on these devices, NVIDIA released in 2007 CUDA [13], a new programming model for GPGPU computing. Since then, the CUDA programming interface allowed to implement many sophisticated and efficient solutions for massively-parallel problems [14]. During these

#### 1.1. Motivation

Figure 1.3: Bandwidth estimated for future architectures of NVIDIA GPU devices.

decades, the computational capabilities and resources available for GPU computing have been increased in an exponential fashion, and the plans of NVIDIA include to make these enhancements even more bigger for the future GPU architectures (see Fig. 1.3).

The implementations developed using the CUDA programming model are only deployable on NVIDIA GPUs devices. On the other hand, there are other programming languages that create an unified interface for all kinds of GPUs that support GPGPU computing. This is the case of BrookGPU [35], developed at Stanford's University, and OpenCL [36], that constitutes a standard API for programming, not only GPUs but also multi-core CPUs. Although the portability offered by these general approaches is key to exploit both GPUs and CPUs with less effort, NVIDIA continues releasing new and more competitive versions of its CUDA compiler and toolkits. This is due to the fact that there are many advanced features and configurations on the NVIDIA boards that can only be manipulated by using this programming model, and a correct handling of these parameters leads to optimized implementations that offer a significantly increment in terms of performance.

Depending on the particular application, it is relatively easy to develop a naïve GPU solution that returns good speedups, thanks to the high-level abstraction offered by the programming model described before. Nevertheless, to correctly tune the code in order to efficiently exploit all underlying GPU resources is a difficult task. It is necessary to have an in-depth knowledge of the device architecture and its resource management in order to predict its behavior, and tune up the configurations for an optimal performance. This responsibility lies directly on the programmers, that need to provide several values for the GPU running parameters, such as the threadblock size and shape for each different GPU function, or for the management of the L1 cache memory, among other examples.

The CUDA programming guidelines suggest the use of threadblock sizes that maximize the occupancy, for obtaining a good performance. However, some studies [15, 16] have shown that, in some cases, these values recommended by CUDA do not always lead to the optimum performance, leaving to the programmers the task of searching for the best values through time-consuming, trial-and-error tests.

### **1.1.3 Heterogeneous Computing**

Heterogeneous computing [17, 18] refers to computing environments or systems that are built with computational devices of different nature. Some classic examples are conventional shared- or distributed-memory multi-processors containing multi-core CPUs, together with GPU devices. In contrast, in the traditional "homogeneous computing" all computational devices have the same nature and similar processing features.