# Performance Assessment of Amorphous HfO<sub>2</sub>-Based RRAM Devices for Neuromorphic Applications

O. G. Ossorio, 1,\*,z

G. Vinuesa, 1,\*

H. García, 1 B. Sahelices, 1 S. Dueñas, 1 B. Castán, 1 E. Pérez, 1 M. K. Mahadevaiah, 2 and Ch. Wenger 2,3 B.

The use of thin layers of amorphous hafnium oxide has been shown to be suitable for the manufacture of Resistive Random-Access memories (RRAM). These memories are of great interest because of their simple structure and non-volatile character. They are particularly appealing as they are good candidates for substituting flash memories. In this work, the performance of the MIM structure that takes part of a 4 kbit memory array based on 1-transistor-1-resistance (1T1R) cells was studied in terms of control of intermediate states and cycle durability. DC and small signal experiments were carried out in order to fully characterize the devices, which presented excellent multilevel capabilities and resistive-switching behavior.

© 2021 The Electrochemical Society ("ECS"). Published on behalf of ECS by IOP Publishing Limited. [DOI: 10.1149/2162-8777/ac175c]

Manuscript submitted April 21, 2021; revised manuscript received July 21, 2021. Published August 5, 2021.

The current trend of non-volatile memories covers a variety of technologies: Ferroelectric RAMs (FRAMs), which include a ferroelectric layer as a dielectric; Magnetoresistive RAMs (MRAMs), based on the magnetization of a ferromagnetic structure; Phasechange RAMs (PRAMs), which depend on crystallization and amorphization processes of a chalcogenide material; Resistive RAMs (RRAMs), which involve electro- and termochemical effects in the resistance change of a metal/oxide/metal system, and some others. 1-6 Focusing on RRAMs, their excellent characteristics (shortoperating time, good scalability, good retention, small-operating voltage, multiplicity of intermediate states) make them very relevant in the quest for a consolidated candidate which could suppose a relevant change in the current state-of-the-art. 7-9 The fundamentals of resistive switching (the mechanism on which RRAMs are based on) involve the growth of a conductive filament inside the dielectric film as a result of applying a potential difference between top and bottom electrodes. <sup>10,11</sup> One of the biggest obstacles in the fabrication of RRAMs is related to finding an appropriate combination of materials for the dielectric layer, and thus the materials research has continously progressed. 12 When the filament completely joins both electrodes, the resistance of the RRAM is low, and, thus, this situation is called LRS (low resistance state). When the polarity of the voltage applied is reversed, a rupture on the filament occurs, the resistance is high and this is called HRS (high resistance state). The transitions to reach the mentioned states are called set and reset, respectively. 13 The MIM devices that were tested in this work had an insulator film of HfO2, which has been extensively studied in the literature and is very appreciated for its usage in resistive memories. 14,15 Interestingly, RRAMs also serve as synaptic elements for neuromorphic networks, attending to the multiple intermediate states which they can reach. 16 Resistive RAMs can even be suitable for both memory and neuromorphic applications, as shown in Ref. 17, 18. There are precedent publications which studied these structures. <sup>19,20</sup> Nevertheless, we provide a complete characterization study of individual devices which were built following the same industrial process.

## Experimental

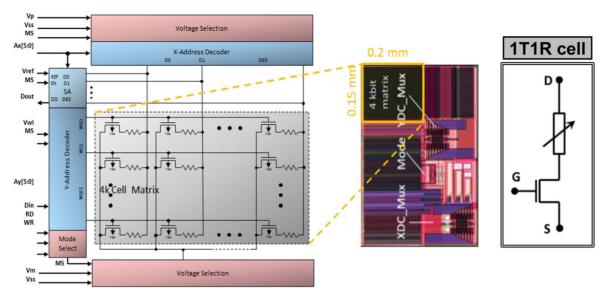

In this work, we evaluated the performance of individual MIM structures which constitute the unit element of a 4 kbit memory array based on 1T1R (1-transistor-1-resistor) cells, as displayed in Fig. 1. The process node to fabricate the devices in the array was

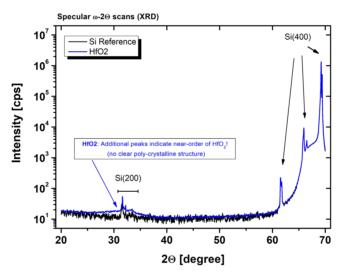

250 nm. In each cell of the memory, an NMOS transistor in series with the MIM resistor was placed so as to be able to select a specific cell and to limit the current that flows through the memory element, preventing an eventual hard breakdown. 19 The MIM stacks presented a TiN/a-HfO<sub>2</sub>/Ti/TiN structure, with the Ti layer below the top electrode. The hafnia layer is amorphous and has a thickness of 8 nm. On the other hand, each TiN electrode features 150 nm thickness and the Ti interface layer spanned 7 nm. In Fig. 2 there are included the XRD results that confirm the amorphous state in HfO2. Moreover, the TEM cross-sectional images that confirm the layer thickness information and also the amorphous state of the HfO<sub>2</sub> film were previously published and can be seen at Ref. 21 and Ref. 19 Each device occupies an area of  $75 \times 75 \mu \text{m}^2$ . The dielectric was deposited by Atomic Layer Deposition (ALD), while the metal films were deposited by magnetron sputtering. The electrical characteristics were acquired by using a Keithley SCS-4200A and comprised DC and small-signal experiments. The latter were run by applying an AC voltage of 30 mV superimposed to the DC signal, with a fixed frequency of 100 kHz. The bias voltage was supplied to the top electrode, while the bottom electrode was grounded.

## **Results and Discussion**

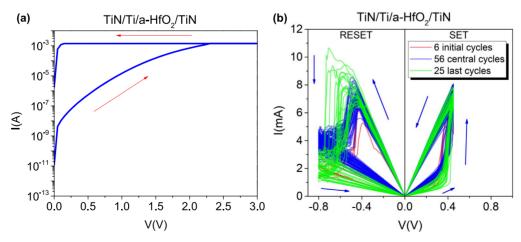

An exhaustive electrical characterization was performed on a moderately large set of devices, including current-voltage, small-signal cycles, memory maps and endurance tests. The forming process is shown in Fig. 3a: the current progressively increases until it reaches a current limit set to 1.4 mA. At that moment, a conductive filament is formed. It was necessary to restrict the maximum current because otherwise the devices break down irreversibly. Figure 3b depicts 87 I-V cycles which show 3 different stages during the series. During the first 6 cycles the behavior was quite erratic, probably as a result of the initial instability of the conductive filament. The next 56 cycles were much more repetitive, although it can be seen a progressive displacement of current values. The experiment finished with 25 cycles which presented symptoms of stress, given that the transitions were very abrupt and the HRS/LRS levels fluctuated excessively.

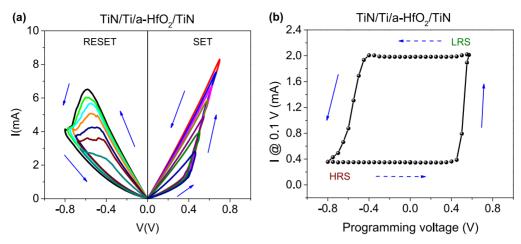

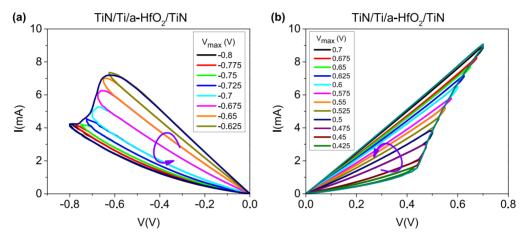

Continuing with I-V characteristics, in Fig. 4a a group of nested cycles is represented. They were obtained by applying voltage sweeps where each one completed a set/reset transition. The state transitions were performed alternately, while the voltage levels increased after each cycle. These cycles prove the excellent properties of the devices, in particular the easy control of the intermediate states. The I-V memory map presented in Fig. 4b shows that the set transition is more abrupt than the reset one. This

<sup>&</sup>lt;sup>1</sup>Department of Electronics, University of Valladolid, Valladolid 47011, Spain

<sup>&</sup>lt;sup>2</sup>IHP-Leibniz-Institut für Innovative Mikroelektronik, Frankfurt (Oder) 15236, Germany

<sup>&</sup>lt;sup>3</sup>BTU Cottbus-Senftenberg, Cottbus 03046, Germany

<sup>\*</sup>Electrochemical Society Student Member.

<sup>&</sup>lt;sup>z</sup>E-mail: ogonoss@ribera.tel.uva.es

Figure 1. Schematic representation of the 4 kbit array composed by 1T1R cells.

Figure 2. XRD results that confirm the amorphous state of HfO<sub>2</sub>.

Figure 3. Electroforming process (a). 87 I-V cycles with 3 different switching stages (b). The current (I) is in absolute values.

could be explained by the fact that the rupture of the filament occurs gradually, whilst the formation is abrupt. The procedure to measure I-V memory maps in RRAMs consists of applying a sequence

of programming voltage pulses, while alternating a read pulse at a fixed voltage (here it is 0.1 V) between programming pulses.<sup>23</sup> Afterwards, each point in the graph is understood as the current read at 0.1 V vs

Figure 4. Nested cycles (a), where the voltage level increased for each set/reset cycle. The current (I) is in absolute values. I-V memory map (b).

Figure 5. Accumulative I-V cycles. Erasing cycles (a). The current (I) is in absolute values. Writing cycles (b).

the previously applied programming voltage. Memory maps are the RRAM equivalent to ferromagnetic hysteresis cycles, where every state depends on the history of precedent states.

To demonstrate the analogical control of the conductance of RRAMs, we performed some writing/erasing tests. These tests were designed to be either accumulative or incremental. In the former, the first step is to apply the opposite transition from that of the experiment, to assure a start from a full initial state. After that, the corresponding write/erase cycles are run while their effects are accumulated. They are synonymous with set/reset cycles with voltage limits. On the contrary, the incremental cycles add a change to the opposite transition after each cycle, which implies that every write/erase begins at the same level. An example of accumulative I-V cycles is depicted in Fig. 5. It is important to remark that an enveloping cycle was added to demonstrate that a full cycle fits perfectly to the progressive transitions. These tests did not have any current limitation.

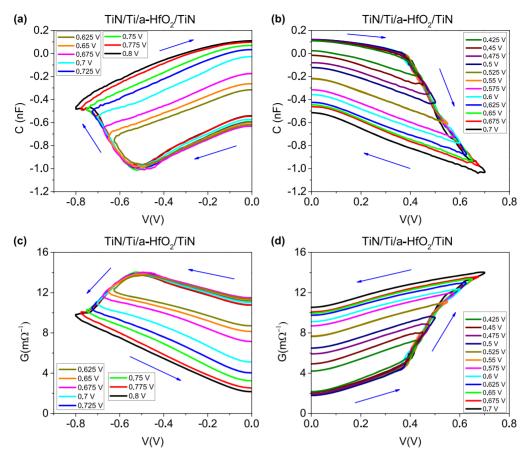

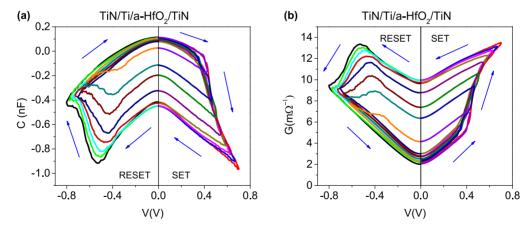

As it was proved before,<sup>24</sup> the study in terms of AC parameters, i.e., the admittance behavior of RRAM, provides relevant information about resistive switching phenomena. To do that, a small signal of 30 mV and 100 kHz was overlapped to the DC. For the sake of exemplification, we include some C-V and G-V incremental writing/erasing cycles in Fig. 6. It is remarkable the ease of control of a potential myriad of levels ranging between HRS and LRS. These characteristics strongly enable the already met objective of building neuromorphic systems with these devices.<sup>19</sup> Another interesting

characteristic of these devices is the considerably narrow voltage range, not even reaching 1 V in either polarity. Thus, the reduced power consumption is another significant, crucial and desired advantage in this case.

Following the same method as in Fig. 4a, there are illustrated some nested cycles in Fig. 7. The reason for the negative capacitance values was proposed in the literature by relating the properties of the conductive filaments with a theoretical model which states that a device in that situation acts as a capacitance in parallel with a resistance in series with an inductance.<sup>24,25</sup>

In addition to our small-signal study, in a publication in collaboration with Milo et al., <sup>19</sup> AC pulsed experiments were carried out over devices with the same stack structure as in this work.

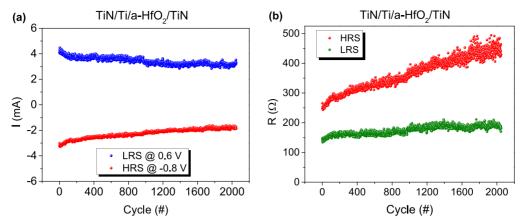

Furthermore, the endurance of the devices was evaluated by applying voltage pulses in order to modify alternately the state to HRS and LRS during 2048 cycles. The results of an endurance experiment are shown in Fig. 8a, where the set and reset pulses feature an amplitude of  $0.6\,\mathrm{V}$  and  $-0.8\,\mathrm{V}$ , respectively. Besides, in Fig. 8b the plotted resistance values exhibited an enlarging HRS vs. LRS ratio as the resistance in HRS was increasing along the iterations.

For the sake of comparison, Table I provides the HfO<sub>2</sub> RRAM main parameters in this work and other reported ones. Although the operating voltages in individual cells are lower than in 1T1R scheme, it must be taken into account the bigger complexity of an array structure. Also, the current did not need to be limited when

Figure 6. Incremental C-V and G-V cycles. C-V erasing (a). C-V writing (b). G-V erasing (c). G-V writing (d).

Figure 7. C-V nested cycles (a). G-V nested cycles (b).

working with individual RRAMs, but this is compulsory for controlling a network of several hundreds of memories at the same time.

Finally, with the aim of apporting more characterization results, we refer to the work from Zahari et al. <sup>29</sup> in which there were developed retention tests over 1T1R cells with the same structure as it is described in our study.

#### Conclusions

An extensive performance study in TiN/a-HfO<sub>2</sub>/Ti/TiN devices was carried out. The dielectric composition resulted in a great yield of the resistive memories, which present a wide functional window

of approximately an order of magnitude between high and low resistance states when measuring the current values at 0.1 V. Both DC and small-signal experiments showed the ease of control of the multilevel states, thus empowering its suitability for neuromorphic circuits. Additionally, the good endurance results and low power consumption of the samples may indicate a large cycle durability with good behavior, where the resistance window augmented stepwisely across the experiment. These results reinforce the prospects of these thoroughly designed devices. With respect to the comparison with other authors' results, it can be stated that the 1T1R structure is an excellent choice for integrating RRAMs into memory arrays, assuring a good control of the state changes and an improved yield.

| Ref. Study | Composition TE/<br>Dielectric/BE                                            | Dielectric<br>Thickness | Structure       | Control Mechanism          | Ratio<br>LRS/HRS | Forming Voltage                                 | SET/RESET<br>Voltages |

|------------|-----------------------------------------------------------------------------|-------------------------|-----------------|----------------------------|------------------|-------------------------------------------------|-----------------------|

| This work  | TiN/HfO <sub>2</sub> /Ti/TiN                                                | 8 nm                    | Individual cell | Voltage (no current limit) | ~2               | ~2.5 V                                          | 0.7 V/-0.8 V          |

| 26         | TiN/Ti/HfO <sub>2</sub> /W                                                  | 10 nm                   | Individual cell | Voltage (no current limit) | ~15              | ∼5 V                                            | 0.6 V/-0.8 V          |

| 19         | TiN/HfO <sub>2</sub> /Ti/TiN                                                | 8 nm                    | 1T1R            | Limited by transistor      | $\sim 10$        | [2 V, 5 V] Maximum yield @ 5 V                  | 1.2 V/1.8 V           |

| 27         | Ti/HfO <sub>2</sub> /TiN                                                    | 10 nm                   | 1T1R            | Limited by transistor      | $\sim 20$        | Measurements @ 380 K ~1.9 V @ pulse             | 1.0 V/1.2 V           |

|            |                                                                             |                         |                 |                            |                  | width = 1 s $\sim$ 2.2 V @ pulse width = 0.01 s |                       |

|            |                                                                             |                         |                 |                            |                  | $\sim$ 2.6 V @ pulse width = 100 $\mu$ s        |                       |

| 28         | TiN/TaO <sub>3</sub> /HfO <sub>2</sub> /Al <sub>2</sub> O <sub>3</sub> /TiN | 8 nm                    | 1T1R            | Limited by transistor      | $\sim 30$        | ~2.25 V @ 473 K (200 °C)                        | 1.68 V/2.14 V         |

Figure 8. Current variation along an endurance test (a). Resistance variation in the endurance test (b).

#### Acknowledgments

This work was funded by the Spanish Ministry of Science, Innovation and Universities grant TEC2017-84321-C4-2-R, with support of Feder funds, and the Deutsche Forschungsgemeinschaft (German Research Foundation) with Project-ID 434 434 223-SFB1461 and by the Federal Ministry of Education and Research of Germany under grant number 16ES1002.

#### **ORCID**

- O. G. Ossorio https://orcid.org/0000-0003-3457-2317

- G. Vinuesa https://orcid.org/0000-0003-0389-3409

- H. García https://orcid.org/0000-0003-1329-8806

- B. Sahelices https://orcid.org/0000-0002-3380-3403

- S. Dueñas https://orcid.org/0000-0002-2328-1752

- H. Castán https://orcid.org/0000-0002-3874-721X

- E. Pérez https://orcid.org/0000-0001-7545-9420

- M. K. Mahadevaiah https://orcid.org/0000-0002-6534-9954

- Ch. Wenger https://orcid.org/0000-0003-3698-2635

### References

- 1. C. Muller, "FRAM Ferroelectric Memories: Basic Operations, Limitations, Innovations and Applications." Ferroelectric Dielectrics Integrated on Silicon. ed. E. Defaÿ (John Wiley & Sons, Hoboken, NJ, USA) 379 (2013).

- 2. S. Bandiera and B. Dieny, "Magnetic Random Access Memories." Nanomagnetism: Applications and Perspectives, ed. C. Fermon and M. Van de Voorde (Wiley-VCH Verlag GmbH & Co. KGaA, Weinheim, Germany) 55 (2017).

- 3. M. Wuttig and N. Yamada, Nat. Mater., 6, 824 (2007).

- 4. R. Waser and M. Aono, Nat. Mater., 6, 833 (2007).

- 5. L. Wang, C. Yang, and J. Wen, *Electron. Mater. Lett.*, 11, 505 (2015).

- X. Dong, C. Xu, N. Jouppi, and Y. Xie, "NVSim: A Circuit-Level Performance, Energy, and Area Model for Emerging Non-volatile Memory." Emerging Memory Technologies, ed. Y. Xie (Springer, New York, NY, USA) 15 (2014).

- 7. S. Munjal and N. Khare, J. Phys. D. Appl. Phys., 52, 433002 (2019).

- 8. H. Jeong and L. Shi, J. Phys. D. Appl. Phys, 52, 023003 (2019).

- T. Shi, R. Wang, Z. Wu, Y. Sun, J. An, and Q. Liu, Small Struct., 2, 2000109 (2021).

- A. C. Jasmin, "Filamentary model in resistive switching materials." AIP Conference Proceedings, 1901, 060004 (2017).

- 11. F. Zahoor, T. A. Zulkifli, and F. Khanday, Nanoscale Res. Lett., 15, 90 (2020).

- V. Gupta, S. Kapur, S. Saurabh, and A. Grover, IETE Tech. Rev., 37, 377 (2020).

- 13. R. Waser, R. Dittmann, C. Staikov, and K. Szot, Adv. Mater., 21, 2632 (2009).

- 14. V. Gritsenko, T. Perevalov, and D. Islamov, Phys. Rep, 613, 1 (2016).

- 15. T. Perevalov, V. Aliev, V. Gritsenko, A. Saraev, and V. Kaichev, Microelectron. Eng., 109, 21 (2013).

- 16. J. Zhu, T. Zhang, Y. Yang, and R. Huang, *Appl. Phys. Rev.*, **7**, 011312 (2020).

- 17. A. C. Khot, T. D. Dongale, J. H. Park, A. V. Kesavan, and T. G. Kim, ACS Appl. Mater. Interfaces, 13, 5216 (2021).

- 18. T. D. Dongale, A. C. Khot, A. V. Takaloo, and T. G. Kim, NPG Asia Mater, 13, 16 (2021)

- V. Milo, C. Zambelli, P. Olivo, E. Pérez, M. K. Mahadevaiah, O. G. Ossorio, Ch. Wenger, and D. Ielmini, APL Mater, 7, 081120 (2019).

- 20. E. Pérez, O. G. Ossorio, S. Dueñas, H. Castán, H. García, and Ch. Wenger, Electronics, 9, 864 (2020).

- R. Romero-Zaliz, E. Pérez, F. Jiménez-Molinos, Ch. Wenger, and J. B. Roldán, Electronics, 10, 346 (2021).

- 22. M. J. Wang, F. Zeng, S. Gao, C. Song, and F. Pan, J. Alloys Compd., 667, 219 (2016).

- S. Dueñas, H. Castán, K. Kukli, M. Mikkor, and K. Kalam, ECS Trans, 85, 201 (2018).

- 24. H. Castán, S. Dueñas, H. García, O. G. Ossorio, L. A. Domínguez, E. Miranda, M. B. González, and F. Campabadal, J. Appl. Phys., 124, 152101 (2018).

- T. Wakrim, C. Vallée, P. Gonon, C. Mannequin, and A. Sylvestre, Appl. Phys. Lett., 108. 053502 (2016).

- 26. Ó. G. Ossorio, S. Poblador, G. Vinuesa, S. Dueñas, H. Castán, M. Maestro-Izquierdo, M. G. Bargalló, and F. Campabadal, "Single and complex devices on three topological configurations of HfO2 based RRAM." 2020 IEEE Latin America Electron Devices Conference (LAEDC), 1 (2020).

- Y.-T. Su, H.-W. Liu, P.-H. Chen, T.-C. Chang, T.-M. Tsai, T.-J. Chu, C.-H. Pan, C.-H. Wu, C.-C. Yang, M.-C. Wang, S. Zhang, H. Wang, and S. M. Sze, IEEE Journal of the Electron Devices Society, 6, 341 (2018).

- X. Huang, H. Wu, B. Gao, D. C. Sekar, L. Dai, M. Kellam, G. Bronner, N. Deng, and H. Qian, Nanotechnology, 27, 395201 (2016).

- 29. F. Zahari, E. Pérez, M. K. Mahadevaiah, H. Kohlstedt, Ch. Wenger, and M. Ziegler, Sci. Rep., 10, 14450 (2020).