**Budapest University of Technology and Economics** Faculty of Electrical Engineering and Informatics Department of Electron Devices

# MSc THESIS MSc degree in Electric Engineering

Jesús Antonio Méndez Puertas

BUDAPEST, 2015

MSC THESIS TASK DESCRIPTION

Mendez Puertas Jesus Antonio candidate for MSc degree in Electrical Engineering

#### **Preliminary investigations on Thermal Electric Devices**

Until now, the continuous development of electronics has been characterized by Moore's law. The scale down resulted in the nanosized CMOS integrated circuits, pushing the "red brick wall" towards the lower dimensions.

Although the current CMOS integrated circuit development is driven by a lot of innovations, there are still some limits determined by unavoidable physical effects such as tunneling of charge carriers through thin insulating regions and statistical irregularities in the number of dopant atoms.

There are many new ideas for building atomic or molecular scale devices for the information technology. However, there is still a gap between the up-to-date "top-down" CMOS technology and the "bottom-up" devices, i.e. molecular electronics, nanotubes, single electron transistors. The new thermal-electric device (phonsistor) and the CMOS compatible thermal-electric logic circuit (TELC) may help to fill this gap. The device is based on the semiconductor-metal transition (SMT) effect shown by certain materials. This effect allows an electric resistance change in three-four orders of magnitude induced by thermal or electrical excitation.

#### Tasks of the student:

- Present a comprehensive review on thermal electric devices and circuits

- Study and analyze some experimental thermal electric devices (VO<sub>2</sub>) structures

- Evaluate results, give suggestions for extension of investigation.

Supervisor at the department: External supervisor: Dr. Mizsei, János, professor

Budapest, 7 March 2014

Dr. András Poppe associate professor head of department

Budapest University of Technology and Economics Faculty of Electrical Engineering and Informatics Department of Electron Devices

Magyar tudósok körútja 2. Building Q. section B. 3rd floor Budapest, H–1117, Hungary, Tel: +36 1 4632702 E-mail: adm@eetbmehu

**Budapest University of Technology and Economics** Faculty of Electrical Engineering and Informatics Department of Electron Devices

Jesús Antonio Méndez Puertas

# PRELIMINARY INVESTIGATIONS ON THERMAL ELECTRONIC DEVICES

supervisor Dr. Mizsei János

BUDAPEST, 2015

### Contents

| Summary                                                          | 6  |

|------------------------------------------------------------------|----|

| Resumen                                                          | 7  |

| 1 Introduction                                                   | 8  |

| 2 Basic devices for managing heat conduction                     |    |

| 2.1 Introduction                                                 | 10 |

| 2.2 Thermal diode                                                | 10 |

| 2.2.1 Three segment thermal diode 2002                           | 11 |

| 2.2.2 Two segment thermal diode 2004                             | 11 |

| 2.3 Negative differential thermal resistance: Thermal transistor | 14 |

| 2.4 Thermal logic gates                                          | 15 |

| 2.5 Thermal memories                                             | 16 |

| 3 MIT (Metal insulator transitions)                              |    |

| 3.1 Mott transition                                              |    |

| 3.2 MIT in VO <sub>2</sub>                                       | 19 |

| 4 VO <sub>2</sub> based switches                                 | 22 |

| 4.1 Deposition techniques of VO <sub>2</sub>                     | 22 |

| 4.1.1 Chemical Vapor Deposition (CVD)                            | 22 |

| 4.1.2 Sol-Gel method                                             | 23 |

| 4.1.3 Sputtering                                                 | 24 |

| 4.1.4 Pulsed Laser Deposition (PLD)                              | 25 |

| 4.2 Thermally driven VO <sub>2</sub> switch                      |    |

| 4.3 Electrically driven VO <sub>2</sub> switch                   |    |

| 5 Thermal electronic logic circuit TELC                          |    |

| 6 VO <sub>2</sub> Laboratory Measurements                        |    |

| 6.1 SMT resistance                                               |    |

| 6.2 NOR thermal gate experiment                                  | 43 |

| 7 Conclusion                                                     | 56 |

| 8 References                                                     | 57 |

# STUDENT DECLARATION

I, Jesús Antonio Méndez Puertas, the undersigned, hereby declare that the present MSc thesis work has been prepared by myself and without any unauthorized help or assistance. Only the specified sources (references, tools, etc.) were used. All parts taken from other sources word by word, or after rephrasing but with identical meaning, were unambiguously identified with explicit reference to the sources utilized.

I authorize the Faculty of Electrical Engineering and Informatics of the Budapest University of Technology and Economics to publish the principal data of the thesis work (author's name, title, abstracts in English and in a second language, year of preparation, supervisor's name, etc.) in a searchable, public, electronic and online database and to publish the full text of the thesis work on the internal network of the university (this may include access by authenticated outside users). I declare that the submitted hardcopy of the thesis work and its electronic version are identical.

Full text of thesis works classified upon the decision of the Dean will be published after a period of three years.

Budapest, 23 June 2015

Jesús Antonio Méndez Puertas

# Summary

A study of the possibilities and developments of the electronic thermal devices is presented. Mainly, it is focused on the review of the principles and previous investigations on the thermal integrated switches based on the novel vanadium dioxide material, that presents a semiconductor to metal state phase transition around 68°C.

In order to prove the viability of the thermal integrated logic circuits, basically consisting on thermal logic gates made of phonsistors, it has been experimentally tested, using a heating plate and a source meter, a single SMT (Semiconductor to Metal Transition) switch and a thermal logic gate structure, based on a platinum contacts geometry deposited on a VO<sub>2</sub> thin film over a silicon substrate.

The experiments revealed the correct operation of the  $VO_2$  switch, proving the previous studied theories, as the resistance change and the reason that produce the transition activation. Also, the NOR logic function was proved on the thermal logic structure, using current driven inputs and a pull-up resistor in the output. The results acquired present the possibility of creating thermal logic gates and electronic circuits based on the phonsistor scheme. Further investigations building nanoscale structures, which would improve the performance, could be done to test the minimum switching times and the power consumption that would have the thermal logic technology.

**Keywords**: thermal logic circuits, vanadium dioxide (VO<sub>2</sub>) switches, thermal logic gates, VO<sub>2</sub> thin films, phononic computing

## Resumen

Se muestra un estudio acerca de las posibilidades de desarrollo de los dispositivos electrónicos térmicos. Principalmente, centrado en los principios y las investigaciones previamente realizadas en los conmutadores integrados térmicos, basados en el novedoso material Dióxido de Vanadio, que presenta una transición de fase del estado de semiconducción al metálico en torno a los 68°C.

Para probar la posibilidad de realizar los circuitos integrados lógicos térmicos, consistentes principalmente en puertas lógicas hechas con "phonsistors", ha sido probado experimentalmente un conmutador SMT (Transición de Metal a Semiconductor) y una estructura de puerta lógica térmica, basada en una estructura de contactos de platino depositada en una capa fina de VO<sub>2</sub> sobre un sustrato de silicio.

Los experimentos realizados, mostraron la correcta operación del conmutador VO<sub>2</sub>, probando las teorías presentadas con anterioridad, como el cambio de la resistencia y las causas que provocan la activación. Además, la función de la puerta lógica NOR es probada en una estructura de lógica térmica, usando entradas activadas por corriente y una salida con una resistencia de pull-up. Los resultados obtenidos presentan la posibilidad de crear puertas lógicas térmicas y circuitos basados en el esquema de los "phonsistors". Posteriores investigaciones para construir estructuras a tamaño nano, que podrían mejorar las prestaciones del sistema, podrían ser llevadas a cabo para probar los tiempos mínimos de switch de las puertas y el consumo de potencia que tendría la tecnología de lógica térmica.

Palabras clave: Circuitos Lógicos Térmicos, Conmutadores de Dióxido de Vanadio (VO<sub>2</sub>), Puertas Lógicas Térmicas, VO<sub>2</sub> Thin Films, Computación de Phonones

# **1** Introduction

Although the CMOS technology is the most extended nowadays on the integrated electronic circuits, some new technologies are been investigated to fight the impossibilities in the size reduction and improving aspects as the operation frequency and the power consumption of the CMOS technology.

The thermal logic circuits could solve the developing problems of the CMOS technology, which is built mainly out of phonsistor devices based on the SMT materials, such as the vanadium dioxide. The vanadium dioxide presents a resistance change of several orders of magnitude at a temperature of approximately 67°C. Some new technologies are carbon nanotubes, molecular electronics and nanowire FET.

The purpose of this thesis is to present the principles and previous investigations on the thermal circuits, and to show afterwards the experimental tests on a  $VO_2$  thin film with platinum contacts structure, trying to prove the possibility of building thermal logic integrated circuits based on the phonsistor device.

Firstly, it is discussed the previous investigations on phononic computing, introducing the necessary building blocks to achieve it, which are the thermal diodes or thermal rectifiers, the thermal transistors (based on the Negative Thermal Differential Resistance (NDTR)), the thermal gates and finally the thermal memories.

Secondly, it is showed the Mott transition principles and the characteristics of the MIT/SMT transition in the Vanadium dioxide (VO<sub>2</sub>), which is basically a Mott transition. The third chapter deals with the design of the VO<sub>2</sub> based switches, starting with the possible deposition techniques for creating the VO<sub>2</sub> thin films and the metallic contacts, and ends presenting some previous investigations of several thermally, electrical and optical driven VO<sub>2</sub> switches. Also, the two main theories of the switching mechanism that induces the MIT in the electrical switching (the Joule heating and field effects), are reviewed.

Finally, it is examined the thermal logic circuit (TELC) proposal, in which the thermal gates and thermal switch tested are founded. The measurements made on a

VO<sub>2</sub> thin film with platinum contacts and the results achieved are exposed in the last chapter.

# 2 Basic devices for managing heat conduction

#### 2.1 Introduction

In the last decade there has been some investigations in the field of the thermal conduction, trying to demonstrate the possibility of building thermal logic gates and devices, which are able to control the heat flow, as their electronic counterparts [4]. The reason why electronic devices have been early developed it is because is much harder to control de flow of heat than the flow of electrons, since phonons (the carriers of heat) are not defined particles but bundles of energy unaffected by electromagnetic fields without mass or charge [5].

Some thermal rectifiers have been proposed and built, by using the property of temperature-dependent power spectra in nonlinear lattices [4], as well as molecular thermal devices that pump heat from a cold to a hot tank.

Moreover, researches based on the new phenomenon of negative differential thermal resistance, have recently built and create models for thermal diodes, thermal transistors, thermal logic gates and thermal and thermal memories, which are the basic components of functional thermal devices [4]. These components add a new physical dimension to information processing in addition to electronics and photonics, eliminating the long regarded view as useless of the heat in electronic circuits [5].

These introduced elements and concepts will be explained in detail below, starting from the thermal diode and finishing with the thermal memories.

#### 2.2 Thermal diode

A primary building block for phononics is a device that rectifies the heat flow, i.e., a thermal rectifier or diode [5]. This device conducts heat in only one direction. The directional thermal effect was firstly observed by the physicist Chauncey Starr in a copper-cuprous-oxide interface. The device models at that time had not any rigorous theoretical foundation such as nonlinear dynamics or computing simulate process [5].

#### 2.2.1 Three segment thermal diode 2002

In 2002 a more serious model for a thermal diode based on resonance was proposed by Terraneo, Peyrard and Casati, based on the possibility to control the energy transport inside a non-linear material one dimensional chain, with a resonant frequency that depends strongly on temperature, connecting two nearly linear segments (thermostats) at different temperatures, which resonant frequencies hardly varies with temperature [1][5].

In the research was observed that the heat flux increased by raising the temperatures of the thermostats and keeping constant the temperature difference, or acting on the properties of the chain. Consequently it allows the system to behave as a common conductor down to an almost perfect insulator [1].

The principle of the thermal rectifier was that when the resonant frequencies or phonon bands of the three regions matched, the heat flux was possible.

When the power spectrum in one part of the device matches that in the neighbouring part, it is found that heat energy is exchanged efficiently. In the absence of such overlapping of the spectral properties, the flux of energy becomes strongly weakened [6].

#### 2.2.2 Two segment thermal diode 2004

Then Casati and other Scientifics in 2004, proposed a model for a thermal diode, which was demonstrated via computer simulation. The system was formed by two segments of nonlinear lattices connected by a harmonic spring with constant strength  $k_{int}$  [2]. Each segment is composed of a chain of particles, joined each other by linear springs [6], this segments are described by Hamiltonian of the Frenckel-Kontorova (FK) model which is supposed to have heat conduction [2].

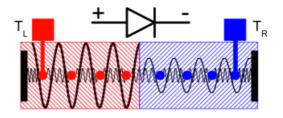

Figure 2.1: Scheme of the thermal diode [6]

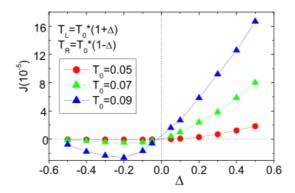

After the numerical simulations, fixing the parameters to simplify, using Langevin heat baths, and integrating the differential equations of motion by using the 5th-order Runge-Kutta algorithm [2]; it was shown that the local heat flux varies with the temperature gradient  $\Delta$  (T<sub>L</sub> – T<sub>D</sub>) and the temperature T<sub>o</sub>, this is depicted in Figure 2.2.

Figure 2.2: Heat current J vs. △, for different values of T0 [2]

As it is shown in the plot, when  $\Delta > 0$  the heat current increases proportionally with  $\Delta$ , while in the case of  $\Delta < 0$  the heat currents is approximately zero. Thus, when  $T_L > T_R$  (heat flow J<sub>+</sub>), the thermal diode conducts properly, and in the case of  $T_R > T_L$ (heat flow J<sub>-</sub>), the heat flux is very poor, so it exists a rectification in the conduction between both heat current directions,  $|J_{+}/J_{-}| > 0$ .

For setting up the rectifier efficiency of the diode it must be observed some parameters, such as the temperature  $T_o$ , the interface elastic constant  $k_{int}$  and the effect of the lattice parameter  $\lambda$ , which refers to the strength of the on site potential.

$K_{int}$  controls the heat flux and consequently the rectifier efficiency  $|J_+/J_-|$ , in the simulations it was proved the variation of the rectification from 2 with  $k_{int}=0.5$  up to 100 for  $k_{int}=0.01$ . Varying  $\lambda$  also was clearly shown that in a wide range of parameters the model had a quite good rectifying efficiency of almost 100 [2].

To understand the rectifying mechanism of this model, it must be taking in account the phonon spectra of the left and right interface particles at the different temperatures, in which the thermal diode works. On one hand, at low temperatures the particles are confined in the valley of the on-site potential which produces a weigh power spectrum in the high frequencies and on the other hand when the temperature becomes higher the particles acquired enough kinetic energies for the thermal activation across the barriers [2], what means a movement of the power spectrum to lower frequencies.

The frequency range of the power spectrum of both segments controls the heat flux, since the more power spectrum overlapping, the more heat conduction. To get the desired strong thermal rectification, the strength of the on site potential in the two sides is set at different levels, more specifically the barrier height of the on-site potential for the right segment is chosen small [6], so it allows the particles to move almost freely, both in the low and in the high temperature regimes, which produces that the spectrum of the right side will be in lower frequencies as we can observe in Figure 2.3.

Figure 2.3: Spectra of the two particles at the interface for different temperatures [2]

A few years after the theoretical models of the thermal rectifiers presented above, some experimentally thermal rectifiers have been built, for example a nanoscale solid-state thermal rectifier has been demonstrated experimentally by asymmetrically deposited carbon and boron nitride nanotubes, the responsible of the rectification phenomenon is thought to be the solitons [7].

# 2.3 Negative differential thermal resistance: Thermal transistor

Once some models of thermal diodes has been presented as well as some experimental thermal rectifiers. The next aim to raise the thermal logic circuits is to create a thermal logic transistor, which controls heat current, analogous to the fieldeffect transistor that controls the flow of electric charge.

The thermal transistor is able to control the heat flux from the hot segment (source) to the cold one (drain), applying a control temperature to a point in the middle (gate). As well as the field-effect transistor the thermal transistor also must have a current gain; it means that changes in the heat current through the gate produces a larger increase in the heat flux from the drain to source.

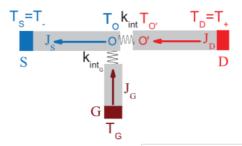

In 2006 Li, Wang and Casati proposed a model for a thermal transistor consisting of three segments drain (D), source (S) and gate (G), following the notation in a MOSFET. Each segment is a FK lattice, as in the 2004 model of thermal diode. Segment D is connected with S via a spring with  $k_{int}$  constant and G is joined via another spring to a particle O in the middle of D and S [3], as it is shown in Figure 2.4.

Figure 2.4: Scheme of thermal transistor [3]

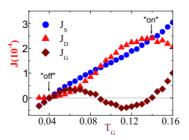

They made several numeric simulations using the Hamiltonian model for the segments, supposing that the lattices were coupled at their first particles, using Langevin heat baths and connecting  $T_+=0.2$ °C and  $T_-=0.03$ °C [3]. These simulations revealed that the thermal transistor model can act as a thermal switch, with heat flux ratio between off and on mode of 100, as well as a thermal current amplifier, just adjusting the parameters values, in this case the only difference in the parameters for both function was the spring constant  $K_{intG}$ .

Figure 2.5: Heat flux vs. control temperature T<sub>G</sub>, k<sub>intG</sub> =1 [3]

There are three working points for  $T_G=0.04$ , 0.09 and 0.14, where  $J_D=J_S$ , these points corresponds to the off state (stable), semi-on state (unstable) and on state (stable).

The transistor function is based on the Negative differential thermal resistance (NDTR) that occurs at the interface between O and O'. When the  $T_G$  increases ( $T_o$  is close to  $T_G$ ), it reduces the temperature difference  $T_D - T_O$ , which we could expect to produce a decreasing in  $J_D$ , however, as observed in Figure 2.5, it is seen that the current flux  $J_D$  increases with  $T_G$ . This fact is due to the FK lattice non linearity in segment D. It is expected that NDTR effect can experimentally be found in nanoscale materials such as nanotubes, nanowires, etc [6].

#### 2.4 Thermal logic gates

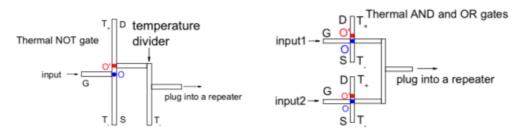

Thermal logic gates based on thermal transistors are possible due to the NDTR effect, when heat flow  $J_D$  increases due to an increase in  $T_{G}$ , it produces an increase in the temperature difference  $T_D - T_O$ , and consequently  $T_{O'}$  decreases. Thus,  $T_{O'}$  changes in the opposite way of  $T_{G}$ .

First of all, as in electronic logic, two standard values are used for representing high and low level, which are  $T_{off}$  (0.03°C) and  $T_{on}$  (0.16°C) [4]. The basic element for achieving the thermal logic is the signal repeater, which is a two terminal device that standardize the output to  $T_{off}/T_{on}$  depending if the input is below or above a threshold temperature  $T_c$  (semi-on state), respectively. The principle is that when  $T_G$  changes slightly it produces a higher change in  $T_O$ , which makes  $T_O$  be closer to the stable temperatures. This repeater is build by connecting several thermal transistors in series, using the input G and the output O. The characteristic of the device is close to an ideal repeater. The next basic element used in this thermal logic proposal is the temperature divider, which behaviour is similar to a voltage divider; the output temperature is an adjustable fraction of the input temperature.

The thermal NOT gate is made of a thermal transistor, using the input G and as output O' [4], since as it was explained before, an increasing in  $T_G$  generates a reduction in the value of  $T_{O'}$ , and vice versa, which means a negative response. The output O' is always higher than  $T_{on}$ , therefore with the divider, the temperature is made lower or higher than  $T_c$  and then it is connected to a thermal repeater to normalize the output value to  $T_{off}/T_{on}$ .

Finally the thermal AND/ OR gate can be realized connecting the output O of two thermal transistors, via two thermal dividers to a single thermal repeater [4], as depicted in Figure 2.6. In both gates when the two inputs are  $T_{off}/T_{on}$  the output is  $T_{off}/T_{on}$ , to made the output  $T_{on}$  or  $T_{off}$  when the inputs are different it is just necessary to adjust the rate of the temperature divider.

Figure 2.6: Scheme of Thermal NOT/AND and OR gates [4]

#### 2.5 Thermal memories

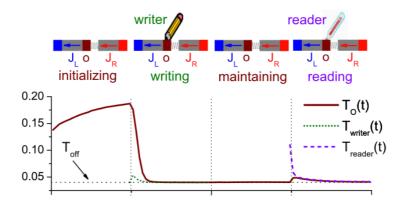

Thermal memories are the last elements necessary for achieving the phononic computing, this device is supposed to storage the information encoded in temperature states.

In [8] it is proposed a model of thermal memory based on the thermal transistor, showed in the chapter 2.3. The node S and D of the thermal transistor model are fixed to a constant temperature  $T_D>T_S$ , and the parameters adjusted. After these, it appears three working points for  $T_G$ , which are  $T_{off}$ ,  $T_{on}$  (stable) and  $T_{semi-on}$  (unstable), where  $J_G=0$ , perfectly balancing  $J_D$  and  $J_S$ . These three working states keep constant even if the heat bath in G is removed, it means that the last temperature

coupled to G is saved, which is the required function of the thermal memory. Moreover, if small fluctuations of the working points temperature appear, the system goes back himself to the stable working points, so the thermal memory system can remain the working temperature unchanged for a long time, in spite of some perturbations that could be applied [6].

A scheme of the thermal memory working process is depicted in Figure 2.7, where the Boolean temperatures available to write are  $T_{off}$  and  $T_{on}$ . In the writing cycle the temperature is coupled to G/O point, after, the writer is removed and the temperature memorized is maintained until a new writing process. For the reading cycle, the reader, i.e. a small thermometer, is connected to the point G/O, in this process, the temperature  $T_O$  is self-recovered [8], as it was already mentioned, keeping the temperature invariable.

Figure 2.7: Thermal memory writing/reading process for an 'off' state [8]

# **3 MIT (Metal insulator transitions)**

#### 3.1 Mott transition

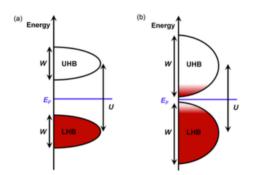

Generally, materials can be differenced either to be an insulator or metal, depending on the position of the Fermi level in the band structure. This model is not sufficient in some cases, since it neglects the Coulomb interaction between electrons (electron correlation).

In materials, which should be a metal, with half filled conduction band, when the electrons hop from a site to a new one, which is already occupied by an electron, they can experience Coulomb repulsion from the electron sited in the new place. If the Coulomb repulsion energy (U) is larger than the electrons kinetic energy, it could drive to bound the electrons to their original site instead of being freely moving for conduction. This effect can be explained as a split of the single half-filled band into a full lower band (lower Hubbard band, LHB) and an empty higher band (upper Hubbard band, UHB) [13], with a band gap equal to the energy U, turning the material into an insulator.

Due to the screening, if the total electron density is increased the Coulomb repulsion will be lowered, and in a critical value the split bands could be merged leading to an insulator to metal transition. The Coulomb repulsion is relative to the band bandwidth (W), as we can observe in Figure 3.1. In transition metal oxides, with bandwidth of 1-2 eV and Coulomb energy 1-10 eV, the band gap is significant, however for conventional semiconductors Si and Ge, the bandwidth is usually 10-20 eV [13], so the Coulomb repulsion can be neglected.

Mott transitions can be induced by tuning the relation between the Coulomb energy and the bandwidth, for example applying stress to the material, or via changing the carrier density, in the last case for the transition to occur, it is needed to satisfy the equation  $n_c^{1/3} a_H \sim 0.25$  [13].

Figure 3.1: Split of the band due to Coulomb repulsion [13]

## 3.2 MIT in VO<sub>2</sub>

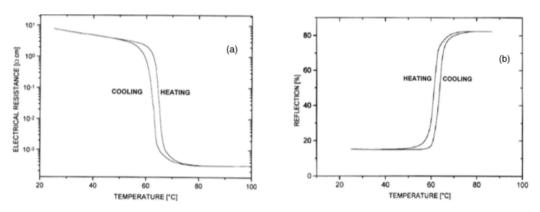

Vanadium dioxide is an intensively studied material, which undergoes a reversible metal to insulator phase transition, which occurs at a temperature near 68°C. The transition produces several changes, which are a lattice structural transition from monoclinic to tetragonal, changes in the electronic properties, since the electrical resistivity increases by 3 to 5 orders of magnitude, and variations in the optical properties, such as the optical reflectivity, at almost all wavelengths [14][10]. Doping the VO2 films and varying the film size, the transition temperature and the switching characteristics can be altered [15].

Although the transition is reversible, it exists a remarkable hysteresis, with widths that varies from approximately 1°C in bulk crystals to 10-15°C in thin films [15], and can be even larger in VO<sub>2</sub> nanoparticles. In Figure 3.2, it can be observed the hysteresis phenomenon in the graphics of the electrical resistance and optical reflection, measured for thin films of VO<sub>2</sub> with 100 nm thickness.

Figure 3.2: Measured hysteresis curves during the MIT of a thin VO2 film for (a) electrical resistance and (b) optical reflectivity at a wavelength of 2.0 µm [15]

The physical mechanism behind the MIT is mostly a Mott transition. However, some authors believe that MIT in VO<sub>2</sub> is not a purely electronic Mott-Hubbard transition, but a transition with two stages. The first step is an electronic Mott transition, that occurs when  $T=T_t \sim 68^{\circ}$ C, and then, this transition immediately initiates a structural change, which remembers to a Peierls phase transition [11]. Nevertheless, in some situations the structural change may not take place.

The MIT transition is triggered when a certain electron density is raised, and no matters if the value of necessary carriers is aimed by heating up the VO<sub>2</sub> to  $T=T_t$ , photo-generation, injection of carriers, or high field generation at switching. Consequently VO<sub>2</sub> thin films can be activated by thermal, electrical (charge injection or Joule heating), photon excitation or external pressure [9].

Some experiments injecting carriers into the VO<sub>2</sub> in a Si-SiO<sub>2</sub>-VO<sub>2</sub> structure, through the Si substrate, have proved that this process can initiate the switching when the electron density in VO<sub>2</sub> exceeds a certain n<sub>c</sub>. The value of n<sub>c</sub> estimated from the experiments was about n<sub>inj</sub>=4.3 x 10<sup>18</sup> cm<sup>-3</sup>, this value for the transition condition, can also be found from the Mott criterion:  $(n_c)^{1/3} \alpha_H \approx 0.25$ , which once operated for the values of the VO<sub>2</sub> gives: n<sub>c</sub> =  $(0.25/\alpha_H)^3 \approx 3 \times 10^{18}$  cm<sup>-3</sup> [10], that is similar to the experimental results.

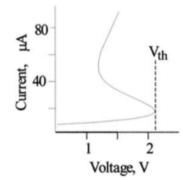

Other important effect in  $VO_2$  is based on MOM films, when a voltage is applied to the film, the channel is heated up to the temperature of transition by the current circulating, which produces a change from the high resistivity to the low resistivity state, resulting in a S-shape voltage-current characteristic, as we can see in Figure 3.3.

Under non equilibrium conditions, with high electric fields approximately above  $10^5$  V/cm [14], the switching effect is proved not to be only a simple electro thermal procedure, but also a electron correlation effect [10][11], since the switching times experimented, around nanosecond scale, are considerable less that which should be if the process would be only by joule heating. Based on this, fast switching and the possibility to control the resistance state of VO2 electrically can be the principle for the utilization of VO2 in high speed electronics.

Figure 3.3: Voltage-current characteristics [10].

# 4 VO<sub>2</sub> based switches

In the last few years several switches based in the Vanadium dioxide, have been proposed. Vanadium dioxide ultrafast switching devices, where the MIT is induced by applying an electric field, could be one of the main applications, since the speed of such a switch is expected to exceed the speed of conventional field-effect transistors [18].

Also, prototypes of high speed and high density non-volatile memory structures, that use  $VO_2$  as a switching element in the memory cell, are being explored [18].

Other transition-metal-oxide systems that have a phase transition could be used as well for novel solid state devices. Some of the materials are high-temperature superconductors, such as Y-Ba-Cu-O system, colossal magnetoresistance in manganites, such as La-Ca-Mn-O family, and also the recent observation of a highmobility electron gas at the interfaces between LaAlO<sub>3</sub> and SrTiO<sub>3</sub> [23]. Switches based in NbO<sub>2</sub>, which shows a thermally triggered MIT at around 1080 K, present switching times below nanoseconds [21].

It can be summarize, that the main benefits of these switches are the highspeed transitions, in the order of nanoseconds, and the size, that can be reduced up to the submicron scale.

Firstly, in this section there will be presented the most common  $VO_2$  thin film growth techniques, and then, some theoretical and experimental electrical, optical and thermal switches, based on these  $VO_2$  films.

#### 4.1 Deposition techniques of VO<sub>2</sub>

#### 4.1.1 Chemical Vapor Deposition (CVD)

This process for depositing high quality and high performance thin films, consist on exposing a substrate to one or more volatile precursors, creating a reaction and/or decomposition on the substrate surface, that leads to the desired deposition. In

the reaction, undesirable secondary products produced are removed by a gas flow through the chamber.

CVD was the first deposition technique used for VO<sub>2</sub> thin films, and it is still extensively used. The process for VO<sub>2</sub> deposition, it is normally based on organometallic chemical vapor deposition or metal organic chemical vapor deposition. The main precursor formulations for growing VO<sub>2</sub> are: vanadium oxychloride (VOCl<sub>3</sub>), which can be carried by N<sub>2</sub> or CO<sub>2</sub> gas into the growth chamber, pyrolysis of vanadium acetylacetonate (C<sub>5</sub>H<sub>7</sub>O<sub>2</sub>)<sub>4</sub>V with mixtures of nitrogen and oxygen, and Vanadyl tri-isopropoxide (VO(OC<sub>3</sub>H<sub>7</sub>)<sub>3</sub>) [15].

Some recent investigations, have demonstrated the deposition of  $VO_2$  on glass via aerosol-assisted CVD, using as precursor (Vanadium (III) acetylacetonate and vanadyl (IV) acetylacetonate), dispersed in a solvent and converted in an aerosol ultrasonically [15]. In this case the precursor does not need to be volatile as in the previous cases.

#### 4.1.2 Sol-Gel method

The Sol-Gel process is a wet-chemical technique for creating materials from a chemical solution, which contains colloidal precursors (sol). Once the sol is evolved to the formation of an inorganic network with a liquid phase (gel), is then deposited on a substrate. After, a drying process is applied to remove the liquid phase, usually alcohols, from the gel, thus forming a porous material that is finally moved to a thermal annealing step in order to favour the crystallization and enhance mechanical properties. This method allows metal doping by introducing the dopants into the sol. VO<sub>2</sub> is sometimes doped with tungsten or niobium to change the transition temperature [15].

In the case of VO<sub>2</sub> formation, generally a solution of vanadium isopropoxide  $VO(OC_3H_7)_3$  diluted in an alcohol is deposited in a substrate via spin coating, and then followed by an annealing in a reducing atmosphere. Also, other vanadium oxide gels used, can be got via the acidification of aqueous solutions of NaVO<sub>3</sub>, via hydrolysis of VO(OR)<sub>3</sub> or using V<sub>2</sub>O<sub>5</sub> [15].

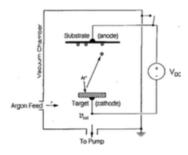

#### 4.1.3 Sputtering

Sputtering is one of the most common physical vapor deposition processes for growing  $VO_2$  thin films, mainly because of its film uniformity, scalability to larger substrates and the efficiency of deposition that can be reach. In this process, there are three different types of energy source that can be used for introducing the required electrons, which are: DC, RF and magnetron sputtering [15].

This method consists on a diode geometry in which the negative charged cathode, is the precursor material, generally a v-metal target ( $V_2O_3$ ,  $V_2O_5$ ), and the anode is the substrate [15]. A gas, normally oxygen/hydrogen mixed with argon is introduced into a pre-pumped vacuum chamber, the free electrons, provided by the energy source, are accelerated away from the cathode and when they approach the outer electrons of the neutral gas atoms, it drives the electrons off, and creates gas ions. The gas ions are fast-tracked into the cathode, striking the target and eroding the precursor material (target) via energy transfer, the neutral particles ejected, travel in a straight line until they get in contact with the substrate, creating a coating with the precursor material particles [16]. Finally, when the free electrons, produced in the eroding of the target, find the gas ions, it changes them back into neutral gas atoms, liberating photons. The formation of new neutral gas atoms, allows the starting of the process again and the eroding of more target particles.

Figure 4.1: DC sputtering mechanism [15].

On one hand, the RF sputtering operates at lower voltage and lower gas pressures, producing higher deposition rates than the DC, and moreover, the RF allows the sputtering of an electrically insulated target [15]. On the other hand, the magnetron sputtering provides the highest deposition-rates sources since the magnetic field, created around the cathode, trap the free electrons close to it, increasing the rate

of gas ions created. Consequently, the quantity target material eroded and deposited on the substrate [16].

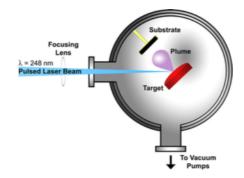

#### **4.1.4 Pulsed Laser Deposition (PLD)**

Pulsed laser deposition is a deposition technique, recently, became the most popular in the field of thin film depositions, mainly for oxide growth (VO<sub>2</sub>). The scheme, as it is showed in Figure 4.2, consists on a laser emitter focused on the target, which is the material that will be deposited, and a substrate, which is facing the target. The target and the substrate are placed inside a vacuum chamber. The chamber can be in an ultra high vacuum or in the presence of a gas, such as oxygen.

The laser emits a high power pulsed laser beam, when the laser pulse strikes in the target, a energy conversion from electronic excitation to mechanical energy is produced, creating a group of ejected energetic species including atoms, molecules, electrons, ions and particulates, with the form of a plume. Then the mixture is deposited on the substrate, which is usually raised to a high temperature. Sometimes after the particles are deposited a process of annealed is used.

Figure 4.2: A typical experimental arrangement for PLD [15].

In the formation of VO<sub>2</sub>, the target is usually metallic vanadium, placed into an ultrahigh vacuum chamber filled with a low pressure Ar and O<sub>2</sub> mixture. The substrates used are mainly silicon, glass, sapphire and quartz, which are heated up to approximately  $500^{\circ}$ C [15].

#### 4.2 Thermally driven VO<sub>2</sub> switch

The Vanadium dioxide experiments a resistance transition at a temperature of approximately 68°C, as it was explained before. Therefore, it could be built a switch, activated by some heater, i.e. a resistance, thermally coupled to a VO<sub>2</sub> film.

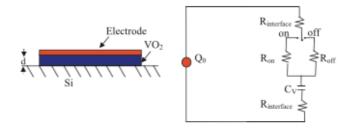

A resistance-capacitance thermal circuit model has been proposed in ref. [12] to determine the switching time of a thermally driven MIT VO<sub>2</sub> nanoscale switch, using some experimental values of the thermal conductivity in the film, and the interfacial thermal resistances. The switch is a metal/VO<sub>2</sub>/substrate structure, modelled, as showed in Figure 4.3. The thickness of the VO<sub>2</sub> film varies from 20 to 100 nm in the simulations.

Figure 4.3: Sandwich structure of VO<sub>2</sub> thermal switch and the RTC circuit model [12]

In the nanoscale, the contact resistances ( $R_{interface}$ ) at the electrode/VO<sub>2</sub> and VO<sub>2</sub>/substrate interfaces are the main point in the heat conduction. The thermal capacitance of VO<sub>2</sub> can be defined by  $C_V = \rho C\Omega$ , where  $\rho = 4340 \text{ kg/m}^3$  is the mass density, C = 690 J/K kg is the thermal capacity and  $\Omega = d \times A$  is the volume of VO<sub>2</sub> [12]. The thermal conductivity ( $\kappa$ ) of VO<sub>2</sub> is dependent of the temperature, in the model, it is simplified by two values, one for T<T<sub>c</sub>,  $\kappa(T)=3.5$ , and another for T>T<sub>c</sub>,  $\kappa(T)=6$ , where T<sub>c</sub>=335K is the critical temperature that separates the "on" and "off" state. From the thermal conductivity, the thermal resistance can be found from the equation:  $R_v(T)=\frac{d}{A \times \kappa(T)}$ . Summarizing, the circuit can be simplified by a total thermal resistance  $R_{total}=2R_{interface}+R_v$ , and the thermal capacitance of VO<sub>2</sub> ( $C_v$ ).

After some operations, an equation for the minimum switching time for the heating process, is presented in Equation (1), assuming the initial temperature  $T_0=298$ K, and the temperature inside the VO<sub>2</sub> higher than the critical temperature (T<sub>c</sub>).

$T_{\infty}$  is the steady state temperature, which depends of the input thermal energy Q<sub>o</sub>, via the equivalence  $Q_o = d \times \kappa \times (T_{\infty} - T_o)$ .

$$T(t) \ge T_c \rightarrow t_{msw} = R_{total} C_v ln \left( \frac{T_o - T_\infty}{T_c - T_\infty} \right) (1) [12]$$

This previous equation is similar for both, cooling and heating process, the differences are the initial temperature, the steady-state temperature and the different thermal conductivity, which results in a different minimum switching time.

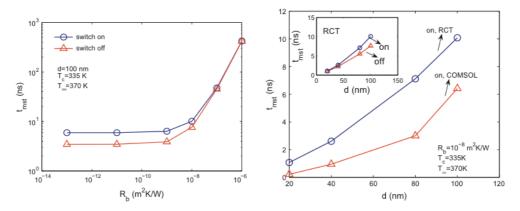

As we can deduce from Equation (1), the switching time depends mainly on the interfacial thermal resistance, VO<sub>2</sub> thickness (d), the critical temperature ( $T_c$ ) and the external thermal source ( $Q_o$ ). The figures presented below show the switching time dependence with these factors. It is observe that the thinner the VO<sub>2</sub> layer, the faster the switch. When the thermal energy ( $Q_o$ ) applied is increased, the switching time decreases. Moreover, it is observed that reducing the  $T_c$ , the switching on time decreases, but it takes more time to switch off. Finally, it is also found, that when  $R_b$  is smaller than  $10^{-9}$  m<sup>2</sup> K/W, the minimum switching time is similar for both process; although slightly smaller for the switch off process. For higher interfacial thermal resistance ( $R_b$ ) values, the minimum switching on time of both processes increases exponentially.

Summarizing, the estimated minimum switching time from the model is of the order of ~1ns [12], which is approximated to the experimentally observed switching times, this switching time can be adjusted with the parameters presented above and generally the switching off process is faster.

Figure 4.4: Effect of the interfacial thermal resistance (Rb) and the thickness (d) on the switching time [12].

#### 4.3 Electrically driven VO<sub>2</sub> switch

In this chapter, there will be discussed the electrically activation reason of the MIT in  $VO_2$  films, and the results acquired in refs. [17][18][19], which present different electrically triggered switches structures.

The electrically triggered phase transition (E-MIT) in VO<sub>2</sub> devices is been investigating nowadays for novel devices for information storage, memory resistances and neural circuits [21].

When an electrical field is applied to a  $VO_2$  switch, there are two main possibilities that can explain the MIT, the Joule heating, due to the current that flows through the channel between the metallic contacts, and the electronic correlation effects, produced by the electronic field applied.

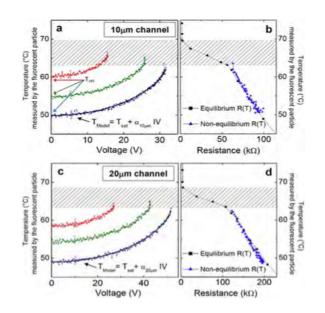

On one hand, the ref. [19] shows, that the Joule heating is the main reason of the dc voltage or dc current induced MIT in VO<sub>2</sub>. For the experiments, they used a Vanadium dioxide 130 nm thick film, deposited by magnetron sputtering on a r-cut sapphire substrate, with gold electrodes over the film, creating channels of 10 and 20  $\mu$ m. They measured the temperature increase in the VO<sub>2</sub>, placing a fluorescent particle of ~1 $\mu$ m inside the channel, and applying a dc voltage through a resistance in series with the contacts, at different initial temperatures T<sub>set</sub>.

The experimental measurements of the channel temperature, incrementing the voltage, fixed the results of the model, assuming an ohmic Joule heating. The results are depicted in Figure 4.5(a,c). Moreover, the resistance measured in the channel, while heating the VO<sub>2</sub> film with a Peltier heater and while increasing the dc voltage, were superposed, and both curves were very close, they are labeled as Equilibrium R(T) and Non-equilibrium R(T) respectively, in Figure 4.5(b,d). From these results, it is proved that the Joule heating plays a key role in the dc voltage or dc current induced MIT in micro sized VO<sub>2</sub> channels.

Figure 4.5: Temperature of flourescent particle vs dc voltage [a,c] and local temperature vs resistance.

On the other hand, the references [17][18] discussed that the electric field is the main reason in the MIT in ultrafast VO<sub>2</sub> switches, since the Joule heating would lead longer switching times.

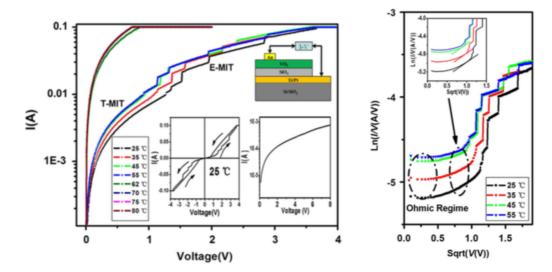

Firstly, in the ref. [17], it is presented a MOIM (Metal oxide insulator metal) structure, where the oxide is the VO<sub>2</sub> film and the insulator is a thin SiO<sub>2</sub> layer. This structure is believe to be a very desirable option in ultrafast electronic devices, since the insulator layer reduce significantly the current between the two metal layers, in the metallic and insulator state of VO<sub>2</sub>, reducing the Joule heating effect and consequently the "on" to "off" switching time.

The perpendicular structure was prepared by depositing firstly a 200 nm Pt layer onto Si/SiO<sub>2</sub>. Secondly, the SiO<sub>2</sub> buffer (180 nm) was grown in the Si/Pt substrate with a chemical vapor deposition, and after, it was created, using RF magnetron sputtering, the VO<sub>2</sub> thin film with 200nm thickness. Finally, an Au patch of 100  $\mu$ m x 100  $\mu$ m was placed over the VO<sub>2</sub>, the structure is shown in the inset of Figure 4.6. The temperature-resistance curve was measured, and it showed an abrupt changed around Tc=66°C with a resistance increment of approximately 2 x 10<sup>2</sup> and a hysteresis window of AT  $\approx$  10°C, which confirms a clear MIT in the structure.

For investigating the E-MIT of  $VO_2$  structure, it was measured the I-V characteristics, measuring the current and incrementing the applied source voltage, between the metallic electrodes, under different temperatures. The results are shown in Figure 4.6. The maximum current of the power source was limited to 100mA to protect the switch when the metallic state is reached.

Figure 4.6: (a) (I-V) curves measured for different initial temperatures (T<sub>0</sub>); inset: schematic of the MOIM structure, hysteresis at T<sub>0</sub>=25°C and leakage current in the SiO<sub>2</sub> buffer. (b) Poole-Frenkel analysis.[17]

When the threshold voltage  $V_T \approx 1.6V$  is overwhelmed, which is equivalent to an electric field of ~4.2x10<sup>6</sup>V/m, it is observed a notable series of jumps in the current, produced by the decreasing of the resistance, which is the MIT. The MIT is even more clear, with the Poole-Frenkel analysis, showed the right graphic of Figure 4.6, where the difference between the ohmic and metallic region are easily notice. These subsequent small MIT steps are may due to the sequential switching of different VO<sub>2</sub> grains, or local domains [17], which are induced by the ionization impact.

The voltage applied to the electrodes produce a carrier injection via the Pt layer into the  $SiO_2$  insulator, and the carriers are kept. The accumulated carriers generate a large charge, that creates an electric field, and acts in the electron subsystem of VO<sub>2</sub>, producing the phase transition [17]. However, a leakage current exists through the  $SiO_2$  layer, so Joule heating causing by defective oxide, probably also contributes to the VO2 film for MIT.

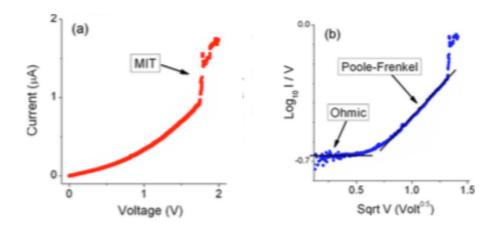

Secondly, in the ref. [18] it is reported the results of the experiments made in a nanoscale VO<sub>2</sub> device. The switch consists on a VO<sub>2</sub> ~100nm thickness film, deposited by dc sputtering over a n-Si substrate, and several Au nanodots of 200nm diameter, deposited on the top of the VO<sub>2</sub> film by electro beam lithography. The structure shows a MIT near 73°C, with a resistance increment of approximately three orders of magnitude.

The electrical measurements were done using a tip AFM between the Au contacts, which are the top contact, and the Si substrate as the bottom contact. The results were done at room temperature. It can be noticed from the results, showed in Figure 4.7, that an abrupt jump in the current and an increment in the conductance are produced when the critical voltage (~1.8V) is reached, clearly showing the phase transition in the VO<sub>2</sub> film. The electrical field at the MIT is approximately  $E_c=1.8V/d=18\times10^6V/m$ , which is a value close to the example presented above.

Figure 4.7: Electron transport measurements in nanoscale VO2 at room temperature using conducting tip AFM. I-V curve from a dot (left), and Poole Frenkel analysis (right). [18]

Finally, it could be considered, that Joule heating due to the current through the junction between the electrodes, could be the possible mechanism of the MIT in the nanoscale devices presented; however, it is only proved in microsize devices with dc current/voltage triggering. The Joule heating power, at the onset of the MIT in the nanojunctions, is comparable to the Joule power of the microdevices used in ref. [20]. It can be deduced from the electrothermal simulations, presented in reference [20], for different microsize switches, that the Joule heating produced by the power required to induce the MIT is insufficient to heat the VO<sub>2</sub> film up to the critical temperature

(68°C), meaning that the transition is a field effect. Also, it was found a weak reduction in the temperature rise at the transition point for narrower channels, produced by a decrease in the channel current, which is proportional to a channel width. A similar decrease is observed in the reduction of the channel length, since the applied power necessary to raise the critical field is reduced. Moreover, since the heat dissipation speed is higher in smaller structures, the heating in the nanojunction should be lower [20].

For measurements done with a voltage source, the temperature rise in the channel just beyond the transition is notably larger than in the semiconductor state, leading to a rapidly thermal phase transition after the field-induced transition. Then, the electronic phase transition precedes the structural phase transition. In most of the simulations, the Joule heating appears insufficient to induce the MIT, however, in the metallic state the heating is enough to maintain the metallic state even if the voltage applied is reduced significantly. It is observed in the large hysteresis between the power required to switch "on" and "off" the VO<sub>2</sub> channel, depicted in the I-V characteristics [20].

The origin of the electric field assisted MIT is an area of ongoing research. It has been argued that the electric field in VO2 causes the doping of the valence band with holes to a critical hole density, thus triggering the hole-driven MIT. The fact that the injection of hole carriers into the material can trigger the MIT, was also established from the optical pump-probe experiments where the carriers were excited by laser pulses [18].

# **5** Thermal electronic logic circuit TELC

Since some decades ago, in the electronics and information technology field, the silicon technology has been the huge dominant. However, nowadays some other technologies are being investigated to developed nanoscale devices with a simpler scheme, and to face the impossibility of the silicon technology for scaling down more due to the tunnel effect.

The new thermal electronic logic (TELC) has been proposed in reference [22], which is based on the  $VO_2$  switches, instead of the current CMOS technology. The technology consists in mixing heating resistors with single SMT-material bulks. The heating resistors are used to set the temperature of the bulks, inducing on it a change from the insulating "off" to metallic "on" state.

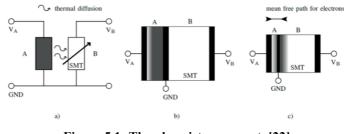

Figure 5.1: The phonsistor concept. [22]

The Figure 5.1 shows the simplest phonsistor device, which consists on a heating resistor (A) and a SMT resistor (B) thermally coupled. In b) it can be observed a phonsistor formed by a resistor between the two electrodes on the left, which is heated by the Joule-effect, and consequently heats the MIT material between the middle and right electrodes, which can switch on the material. Finally, in c) it is pointed the effect of scaling down the phonsistor, where the heating resistor thickness is lower than the mean free path for electrons, and it leads the hot electrons to be injected by ballistic transport directly into the SMT material, and then, they thermalize there.

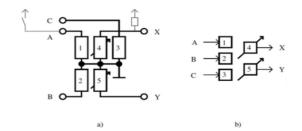

The thermal electronic gates are formed of one or more input, which are normally heating resistors voltage/current driven (or SMT resistors), thermally coupled to one or more SMT resistors, which are the outputs, as it is observed in Figure 5.2. The combination of the heating resistors and SMT resistors can produce different type of gates. If the thermal coupling is strong it could be possible to switch on the SMT resistor of the output, only with one input activated, otherwise if the coupling is weak, it may be necessary to active more than one input to switch the output, forming OR and AND gates respectively. Therefore, adjusting the thermal coupling between the inputs and the outputs, via geometrical distance and/or using different isolating materials between them, it could be easily created OR/AND logic gates and combinations of them.

Figure 5.2: Conventional a) and simplified b) scheme of a general thermal-electronic logic gate.

[22]

The TELC consists on many phonsistors, which can be thermally coupled to each other or connected through metallic wires to longer distances via electric signals, if the output SMT resistor of the phonsistor is connected to a pull up resistor.

The TELC is supposed to be compatible with silicon integrated circuits. The TELC can be created by lateral arrangement or vertical arrangement, which seems more promising, since it could be compatible with standard silicon CMOS VLSI circuits and it could be more dense. The thermal time constants in this nanoscale integration can be comparable to the electric constants, approximately 10<sup>-10</sup> seconds.

Since the TELC scheme is simpler than the conventional VLSI circuit, it contains less interfaces, and allows an easier and more effective scaling down, limiting the linear size due to the tunnel effect to 10nm in phonsistor devices, instead of 50nm, as in complex logic gates (CMOS).

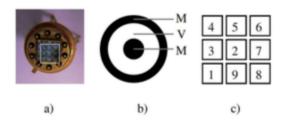

This technology has been proved on a complex gate, realized on a  $VO_2$  thin layer deposited onto an isolator substrate, with metallic contacts forming rings, Figure 2.1 b). The outer rings are connected together forming the ground, and the electrical controller of each gate is insulated. The internal contacts are the input and outputs, and all the gates are thermally coupled.

Figure 5.3: a) Photograph of the experimental thermal-electronic integrated circuit. b) Structure of a single device. c) Numbering of the coupled devices [22]

For the test, the gates were connected to current limited power supplies, through pull up resistors. It was tested the NOR operation and the AND operation, with the gate No. 3 as output and gates No. 5 and 7 as input. In the NOR operation any of the input gates could switch on itself and the output. However, with lower supply voltages in the inputs or shorter time scale, it was needed unless two inputs to generate enough Joule heat to switch on the output gate, thus, simulating a NAND gate. The phonsistor is switched off only by decreasing the supply voltage of the output. The device switching time can be estimated about 10 ms for this relative large size TELC device.

# 6 VO<sub>2</sub> Laboratory Measurements

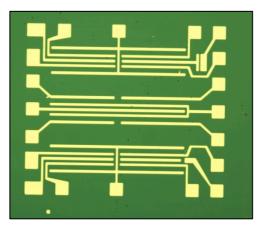

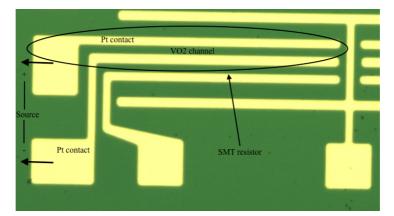

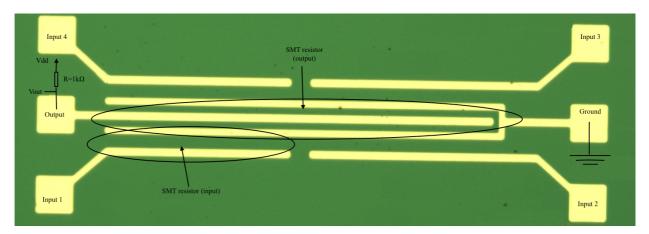

For the experiments of the Thermal Logic Circuit, it has been used a layer with an  $VO_2$  thin-film of 100nm thickness and Platinum contacts of approximately 50nm width.

The VO<sub>2</sub> layer was developed using the Pulsed Laser Deposition technique, where exactly 20000 laser pulses were stroke in a vanadium target during a period of 33 minutes. The target and the substrate were placed into a vacuum chamber, filled with  $O_2$  gas at  $2x10^{-3}$  mbar. The substrate used was SiO<sub>2</sub>-Si and was kept at 600°C during the process. This VO<sub>2</sub> layer was fabricated in Finland.

The desired geometries of the Pt contacts, which are shown in Figure 6.1, were made with a lift-off technology. For the deposition of the platinum in the wafer, it was used RF reactive cathode sputtering, the sputtering power used was 100W with a voltage of approximately 1kV and the current through the magnet was 5A. Firstly the chamber was pre-vacuumed up to  $\sim 2 \times 10$ -4 Torr and then, Argon was introduced into the chamber until a pressure of  $10 \times 10$ -4 Torr was reached. The plate was covered with a 5 min pre-sputtering, and then 5 min of sputtering. The vacuum pressure of the chamber at the end of the process was  $\sim 1 \times 10$ -4 Torr. The deposition process of the platinum contacts has been made at the BME University.

Figure 6.1: The three different geometries of the platinum contacts over the VO<sub>2</sub> film.

## 6.1 SMT resistance

Firstly, it has been measured the characteristics of the SMT resistance formed between two upper platinum contacts on the left, in the below geometry of Figure 6.1, the scheme is represented in the Figure 6.2.

Figure 6.2: Scheme of the SMT resistor based on VO<sub>2</sub> channel.

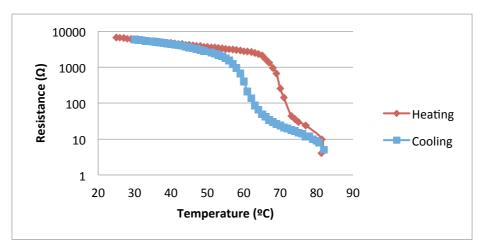

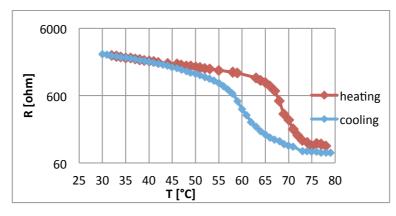

The graphic of the temperature-resistance, showed in Figure 6.3, has been achieved varying the temperature of a hot plate situated below the VO<sub>2</sub> layer and with a thermal coupling paste between them, to facilitate the heating. The temperature of the hot plate is controlled by heating and cooling the water that flows inside the plate. The resistance was measured by placing two probes over the contacts. The probes were connected to a Kethley 2450 source meter and it was applied 10  $\mu$ A to the contacts for measuring the resistance.

Figure 6.3: Resistance – temperature graphic between the two platinum contacts.

The phase transition was produced at approximately 70°C, and the resistance changed from  $6,5k\Omega$  at the room temperature to  $5\Omega$  in the metallic state, it means a change of 3 orders of magnitude, as it could be predicted from the references presented in the previous chapters. Also, there is a hysteresis of ~10°C, which is the usual for thin films. In the metallic state, the colour of the VO<sub>2</sub> layer changes from green to dark purple.

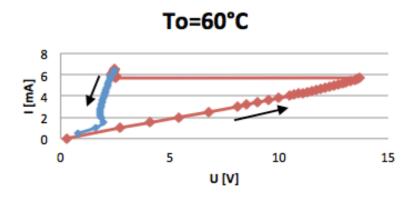

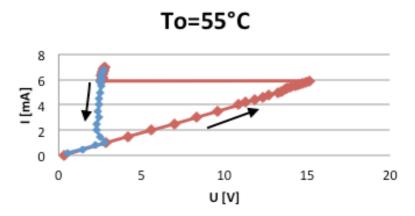

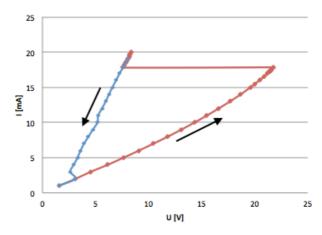

Then, the voltage-current characteristic has been measured in the same contacts, the source meter was connected to the contacts, and it was varied the current while the voltage was monitored. The tests were done for different temperatures of the hot plate; these plots are shown in Figure 6.4, 6.4 and 6.5.

In a first approximation, it can be explained the phase switch between the platinum contacts, as a Joule-heating effect, produced by the current through the  $VO_2$  channel, since as it can be deduced from Chapter 4.3, the electric field effects appeared for nanoscale ultra-fast switches, but for micro size channels voltage/current driven as ref. [19] expounds, the Joule heating is the reason of the switch.

It can be observed in the figures below, that the  $VO_2$  resistor has a tyristor like characteristic. When the current increases, the voltage increase as well with the ratio of the resistance existing between the contacts. Once the critical power is reached, which produces the enough Joule heat to achieve the transition temperature (68°C), the  $VO_2$  channel switches to the metallic state. When the metallic state is raised the resistance drops, and consequently the voltage decreases. The "on" state is kept until the current decrease so much, that the metallic state cannot be maintained and the channel recovers the semiconductor state. The resistance during the "off" state decreases slightly with the current increment, due to the temperature increment produced by the Joule heating.

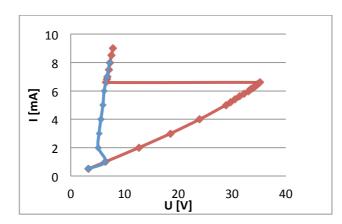

Figure 6.4: Current - voltage graphic of the SMT resistor at 60°C

At the 60°C temperature measurement, the resistance varies from 2800  $\Omega$ , with 10µA, in the off state, up to 380  $\Omega$  in the metallic state at 6,5mA. The transition was produced at 5,7 mA, the voltage dropped from 13,7V to 2,5V, this means that the Joule heat power required was 78mW.

The experiments with the layer at 55°C, showed, that for the phase transition it was required approximately 6mA, which produced a 91mW Joule heat power. The resistance changed from 2870 $\Omega$ , with 10 $\mu$ A, to ~400  $\Omega$  in the metallic state.

Figure 6.5: Current - voltage graphic of the SMT resistor at 55°C

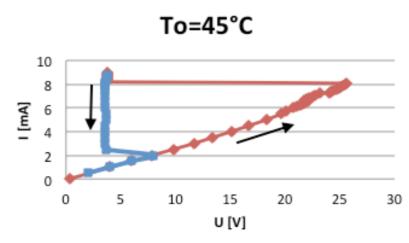

Then at the temperature of 45°C it was measured the I-V characteristic, at the first measurement, which is showed in Figure 6.6, the phase transition was produced at 8,1 mA and 25,5V, which means a power of 207,4 mW, but on the posterior measurements the transition was achieved at around 7mA (160 mW). The resistance varies from 3980 $\Omega$ , at 10µA, to 425 $\Omega$  at 9mA, which corresponds to semiconductor and metallic state, respectively.

Figure 6.6: Current - voltage graphic of the SMT resistor at 45°C

It can be summarize from the figures above, that while the temperature of the layer decrease, the power required to switch the resistor increase, which is due to the bigger temperature increment needed to raise the transition temperature. From the Joule heating equation  $\Delta T = P \times R_{th}$ , it can be established an average thermal resistance for the VO<sub>2</sub> resistor, establishing the transition temperature at 70°C, as observed in Figure 6.3, and the power required to achieve the transition as P=V x I, where V and I is the voltage and current in the moment of the transition, observed in the characteristics on Figure 6.4, 6.4 and 6.5. In the Table 1, it is presented the experimental thermal resistance for each temperature.

The average thermal resistance is 140 K/W, which is a first approximation to find the Joule heat power needed to switch on the channel for each working temperature, however this is not a exact approximation due to the leakage current flow variations, since the current path is not completely defined.

The resistance change between the on and off state is less than one order of magnitude, which is quite lower than the measured at the resistance temperature graphic, which was 3 orders. These increment on the on state resistance is produced because only a narrow metallic state channel is formed in the  $VO_2$  film between the contacts, instead of switching on the whole  $VO_2$  film channel, as it was produced when the whole layer was heated. The reason for this narrow channel is that the current is not equally distributed through the whole metallic pad due to the current leakage. Therefore, it produces that the current which flows in the proximity of the pad connexion to the needles, is higher than in the further parts, leading to heat more

the closest portions of the  $VO_2$  film than the others, and consequently the phase transition is done only in the zone where the critical temperature is reached first.

| To                               | $\Delta T$ | I <sub>th</sub> (transition current) | P <sub>th</sub> (transition power) | R <sub>th</sub> (thermal resistance) |

|----------------------------------|------------|--------------------------------------|------------------------------------|--------------------------------------|

| 60°C                             | 10°C       | 5,7 mA                               | 78,1 mW                            | 130 K/W                              |

| 55°C                             | 15°C       | 6 mA                                 | 91,2 mW                            | 160 K/W                              |

| 45°C (first measurement)         | 25°C       | 8,1 mA                               | 207,4 mW                           | 120 K/W                              |

| 45°C (posterior<br>measurements) | 25°C       | 7 mA                                 | 164 mW                             | 150 K/W                              |

Table 1: Thermal resistance experimentally found from Joule equation

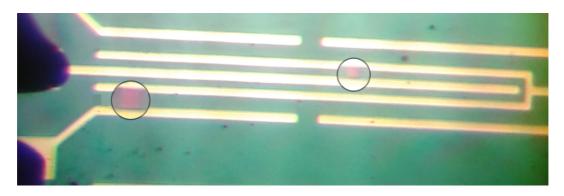

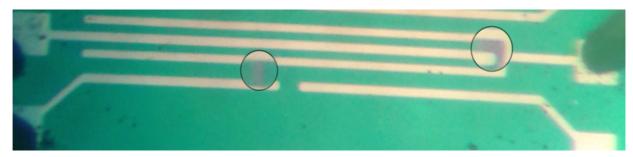

It was reported some problems when it was tried to switch on at 35°C. For switching on the SMT resistor the current was increased by 1mA steps, but at 5mA (165mW) it appeared a big increased in the voltage, since the electrical resistance started to increase, it changed from 4,9 k $\Omega$  to 6,6 k $\Omega$ . A crack in the VO<sub>2</sub> channel and the platinum contact was observed with the microscope, the image of the break is showed in Figure 6.7.

Figure 6.7: Crack in the VO<sub>2</sub> channel and Pt contact at 35°C measurements.

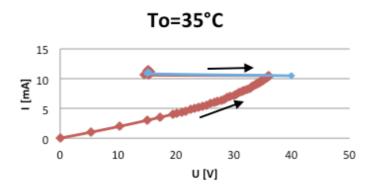

After the crack, the measuring probes were changed to another part of the layer over the same geometry, to try again to switch on the channel at 35°C. This second time, the current was increased slowly, with 0,1 mA steps. The current-voltage characteristic found is shown in Figure 6.8.

At 10,5mA and 36,1 V, which produced 379 mW, the resistance changed from  $3438\Omega$  to  $1367\Omega$  which could be associated to the SMT transition, although the change is not large. After increasing current, the metallic state continued, but when the current decreased to 10,5 mA again, the resistance increased to 3809  $\Omega$ , since the channel switched off. The thermal resistance observed from this measurement is approximately 100 K/W, which is not too far from the one found at the other tests.

It can be noticed, that in the last experiment at  $35^{\circ}$ C the channel switched off at the same current of the switch on, which is very fast compared with the measurements done at the other temperatures, where the hysteresis between the current needed for change from the semiconductor to metallic state and viceversa, was quite large. The high temperature increment needed to heat for switching on the channel cannot be maintained when the current starts to decrease. The reason may be, that the temperature difference between the whole plate and the channel is large, leading to a high heat flow, which produces a faster cooling of the VO<sub>2</sub> channel.

Figure 6.8: Current - voltage graphic of the SMT resistor at 35°C

Finally, on the figure below it is displayed the black stain produced in the channel after switching on and off the resistor several times, in the 45°C experiment.

Figure 6.9: Crack in the VO<sub>2</sub> channel at 45°C measurements.

## 6.2 NOR thermal gate experiment

Based on the theory of the TELC (thermal logic circuits) presented in chapter 5, it is known that several SMT resistances thermally coupled can realize the function of different gates. In the layer reviewed for the study, the platinum contacts over the  $VO_2$  layer forming different geometries, showed in Figure 6.1, can function as the thermal gates.

It has been studied the logic function and properties of the scheme showed in Figure 6.10, which consists on four SMT resistors, which are thermally coupled to other SMT resistor in the middle, following the scheme of the phonsistors depicted in Figure 5.1.

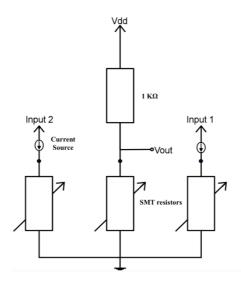

The NOR gate function is tested, using four input SMT resistors current driven, which are formed between the platinum contacts, named as Input 1, 2, 3 and 4, a platinum contact in the middle labelled as Ground, and an output SMT resistance between output and ground contacts. The input resistors activate the output SMT resistor by Joule heating. The output contact of the output resistance, is connected to a voltage source through a  $1k\Omega$  resistance, limiting the current through the SMT resistance, and creating the NOR function, since when an input turns on it leads the output resistance to switch to the metallic state, consequently Vout is connected via the small resistance value, at the metallic state, to the ground. The  $1k\Omega$  pull-up resistance absorbs the most of the Vdd voltage drop.

Figure 6.10: Modified image, obtained from the microscope, of the NOR thermal gate structure

Figure 6.11: Electrical scheme of the thermal NOR gate

Firstly, it has been measured the resistance-temperature characteristic of the SMT output resistance, which is showed in Figure 6.12, following the method described in section 6.1 used to obtain the Figure 6.3. As it was expected, at a temperature of approximately 70°C the VO<sub>2</sub> channel switched from the semiconductor to metallic state, the resistance decrease from 2,3k $\Omega$  at 30°C to 85 $\Omega$  at 80°C. At the cooling process as noted before, the switch from metallic to semiconductor state is not produced at the same temperature, this hysteresis is observed to be more or less 7 °C.

In this scheme it is noticed that the resistance between the platinum contacts at the semiconductor state is lower than the resistance at the SMT resistance studied in section 6.1. The reason must be the better geometry, which reduces the quantity of current leaking through other parts of the  $VO_2$  film, instead of following the path between the high potential and the ground. Since the current path is better defined, the resistance is less.

Figure 6.12: Resistance-Temperature graphic of the SMT resistor between the Output and Ground

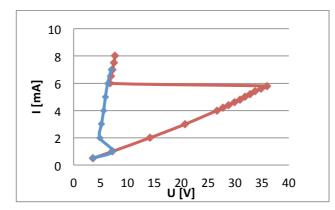

Then, the hot plate placed below the  $VO_2$  was heated up to 50°C, after, increasing the current applied and monitoring the voltage, it has been found the current-voltage characteristic of the SMT output resistor, and it is depicted in Figure 6.13. This test was done before connecting the output to the supply voltage "Vdd".

When the power applied to the output resistance reached 387,5 mW the channel switched from the semiconductor to metallic state, it is noticed a drop on the resistance from 1,5 k $\Omega$  to 420  $\Omega$  at the semiconductor and metallic state respectively. The resistance at the metallic state is higher than the observed in Figure 6.12, since the metallic state is just produce in a narrow channel at the VO<sub>2</sub>. This affirmation is derived from the resistance equation:  $R = \rho \times \frac{L}{s}$ , where S is the section/area, L the length and  $\rho$  the resistivity constant of the conductor. Therefore, the higher the material surface the less the resistance.

The metallic state is conserved until the power supplied descends below approx. 8 mW, where the resistance jumps from  $800\Omega$  to  $1550\Omega$ . While the power supplied is decreasing, the electrical resistance rises slightly due to the temperature reduce, (as observed in the resistance-temperature graphic), until the critical temperature is reached and it switches to the semiconductor state. This is clearly seen in the graphic below, where at 3mA and 2,7V, the slope of the descending line (resistance), turns back to the previous slope at the semiconductor state, when the current was increasing. Despite the low power applied, the metallic state is maintained until quite below the power value needed to switch on the channel. The reason is that once the metallic channel is created in the VO<sub>2</sub> film, all the current flows through this narrow channel, increasing the collisions between the electrons and consequently producing a higher amount of heat, which turns into a higher thermal resistance in the metallic phase, (as it will be see in Table 2,3). Then the temperature at this channel is maintained over the switch "off" critical temperature, approximately 63°C, with a low Joule heat power.

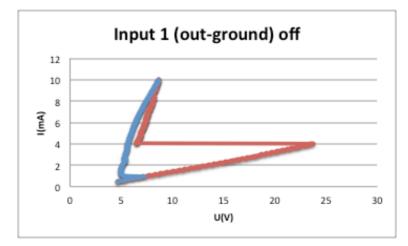

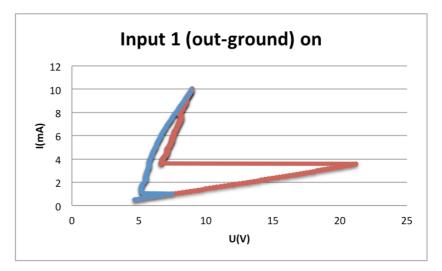

Figure 6.13: Current - voltage graphic of the SMT resistor between the Output and Ground contacts at 50°C

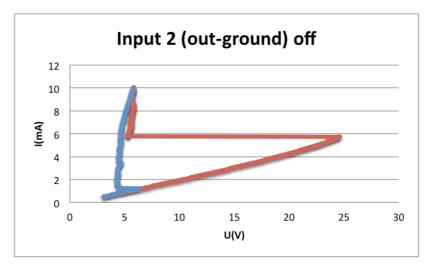

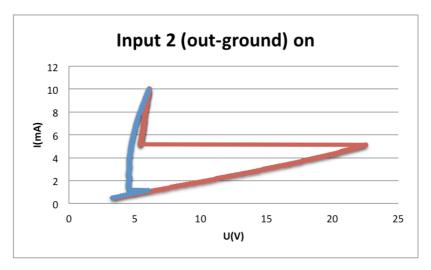

Then, it has been measured the current voltage characteristics of the SMT resistances created between the Input 1, 2 and the ground, at 50°C, before connecting Vdd. The plots are showed in Figure 6.14, 6.14. The average power measured, required to switch on the resistances after several test, was 210mW and 230mW for the Input 1 and 2 resistances, correspondingly. Otherwise, the power measured in the transition from metallic to semiconductor state was approximately 10mW for both cases.

Figure 6.14: I-V characteristic of SMT resistance between Input 1 and ground contacts.

Figure 6.15: I-V characteristic of SMT resistance between Input 2 and ground contacts.

The thermal resistance can be found experimentally using the Joule heating relation:  $\Delta T = P x R_{th}$ , as it was done in the previous section, or through the equation of the thermal resistance in an specific material, this has two variations depending if the surface crossed by the current (heat source), is big or small compared to the heat sink, in this case the silicon substrate. In the second case it has to take in account the spreading resistance approximation. The equations of the thermal resistance are the Thermal resistance in a specific material (2) and the Spreading thermal resistance (3).

$$R_{\rm th} = \rho_{\rm th} \times \frac{\iota}{A} \quad (2)$$

$$R_{\rm th} = \rho_{\rm th} \times \int \frac{dr}{2\pi r^2} = \frac{\rho_{\rm th}}{2\pi} \times \left[ \left( -\frac{1}{r_{\rm in}} \right) - \left( -\frac{1}{r_{\rm fin}} \right) \right] (3)$$

Where  $\rho_{\text{th}}$  is the resistivity of the material, "t" thickness, "A" area/surface and  $r_{\text{in}}$ ,  $r_{\text{fin}}$  are the radio of the narrow metallic channel created on the VO<sub>2</sub> over the silicon surface, and the radio at the end of the silicon, which can be approximated to  $\infty$ , respectively.

From the previous equations, it is calculated the values of the experimental and theoretical thermal resistance of the output SMT resistance, and the input resistances, this values are presented in Table 2 and 3.

|                                                | $\Delta T$ | Current | Power   | R <sub>th</sub> |

|------------------------------------------------|------------|---------|---------|-----------------|

| Output resistance<br>"Semiconductor<br>state"  | 20 °C      | 18 mA   | 387 mW  | 52 K/W          |

| Output resistance<br>"Metallic state"          | 13 °C      | 3 mA    | 8 mW    | 1625 K/W        |

| Input 1 resistance<br>"Semiconductor<br>state" | 20 °C      | 5,7 mA  | 210 mW  | 95 K/W          |

| Input 1 resistance<br>"Metallic state"         | 13 °C      | 2 mA    | 9,8 mW  | 1325 K/W        |

| Input 2 resistance<br>"Semiconductor<br>state" | 20 °C      | 6,5 mA  | 230 mW  | 87 K/W          |

| Input 2 resistance<br>"Metallic state"         | 13 °C      | 2 mA    | 10,2 mW | 1275 K/W        |

Table 2: Thermal resistance estimated from experimental values

For the theoretical equations, it can be supposed that all the heat is produced in the silicon substrate layer, which thickness is  $300\mu m$ , since the thickness of the VO<sub>2</sub> film and the platinum contacts is of the order of nm, than, the value of the thermal resistance of this films is negligible compared to the thermal resistance of the silicon substrate. The value of the thermal resistance used for the silicon layer is 0,77 cm°C/W, extracted from Ioffe Institute web page.

Table 3: Thermal resistance estimated from Eq. (2) and Eq. (3)

|                                               | Width | Length | Area /Radius           | R <sub>th</sub> (thermal resistance) |

|-----------------------------------------------|-------|--------|------------------------|--------------------------------------|

| Output resistance<br>"Semiconductor<br>state" | 60 µm | 800 µm | 0,0464 mm <sup>2</sup> | 50 K/W                               |

| Output resistance<br>/Input 1,2<br>"Metallic state" | 10 μm (metallic<br>channel width at<br>the beginning) |        | $5 \ \mu m$ (radius of circle equivalent to rectangular channel) | 245 K/W |

|-----------------------------------------------------|-------------------------------------------------------|--------|------------------------------------------------------------------|---------|

| Input 1 resistance<br>"Semiconductor<br>state"      | 45 μm                                                 | 380 µm | 0,017 mm <sup>2</sup>                                            | 135 K/W |

| Input 2 resistance<br>"Semiconductor<br>state"      | 45 μm                                                 | 400 µm | 0,018 mm <sup>2</sup>                                            | 128 K/W |

The values of the thermal resistance experimentally and theoretically, showed in the tables above, are in concordance, proving that the Joule heating effect, which occurs in the device is the reason for phase transition from metallic to semiconductor and from semiconductor to metallic state. The Joule heating increases the temperature in the VO<sub>2</sub> film and then produce the phase transition. The small differences produced in the thermal resistance in the semiconductor state are may be due to the current leakages, since not the totally of the current flows to the surface between the input and the ground surface, it is been supposed at the theoretical results.

Nevertheless, it is observed a big difference at the thermal resistance values at the metallic state, which can be explained with the following remarks.

A decreasing in the current is tested to produce a slight increasing in the electrical resistance, due to the cooling of the channel and the decrease of the channel thickness. It has been observed, that the higher the power the larger the width of the channel, and viceversa. This channel width decrease could be the reason for explaining the large thermal resistance observed experimentally in the switch from metallic to semiconductor state, and consequently the high hysteresis between the power necessary to switch on and off.