## Universidad de Valladolid

Escuela Técnica Superior de Ingeniería Informática

Departamento de Informática

## Tesis Doctoral:

# Design and evaluation of a Thread-Level Speculation runtime library

Presentada por **D. Álvaro Estébanez López** para optar al grado de doctor por la Universidad de Valladolid

Dirigida por:

Dr. Diego R. Llanos Ferraris

Valladolid, Octubre 2015

#### Resumen

En los próximos años es más que probable que máquinas con cientos o, incluso, miles de procesadores sean algo habitual. Para aprovechar estas máquinas, y debido a la dificultad de programar de forma paralela, sería deseable disponer de sistemas de compilación o ejecución que extraigan todo el paralelismo posible de las aplicaciones existentes. Para ello, durante los últimos tiempos, se han propuesto multitud de técnicas paralelas. Sin embargo, la mayoría de ellas se centran en códigos simples, es decir, sin dependencias entre sus instrucciones. La paralelización especulativa surge como una solución para estos códigos complejos, posibilitando la ejecución de cualquier tipo de códigos, con o sin dependencias. Esta técnica asume de forma optimista que la ejecución paralela de cualquier tipo de código no de lugar a errores y, por lo tanto, necesitan de un mecanismo que detecte cualquier tipo de colisión. Para ello, constan de un monitor responsable que comprueba constantemente que la ejecución no sea errónea, asegurando que los resultados obtenidos de forma paralela sean similares a los de cualquier ejecución secuencial. En caso de que la ejecución fuese errónea los *threads* se detendrían y reiniciarían su ejecución para asegurar que la ejecución sigue la semántica secuencial.

Nuestra contribución en este campo incluye (1) una librería de ejecución especulativa nueva y fácil de utilizar; (2) nuevas propuestas que permiten reducir de forma significativa el número de accesos requeridos en las operaciones especulativas, así como consejos para reducir la memoria a utilizar; (3) propuestas para mejorar los métodos de *scheduling* centradas en la gestión dinámica de los bloques de iteraciones utilizados en las ejecuciones especulativas; (4) una solución híbrida que utiliza memoria transaccional para implementar las secciones críticas de una librería de paralelización especulativa; y (5) un análisis de las técnicas especulativas en uno de los dispositivos más vanguardistass del momento, los coprocesadores Intel Xeon Phi.

Como hemos podido comprobar, la paralelización especulativa es un campo de investigación activo. Nuestros resultados demuestran que esta técnica permite obtener mejoras de rendimiento en un gran número de aplicaciones. Así, esperamos que este trabajo contribuya al acercamineto del uso de soluciones especulativas a los compiladores comerciales y/o los modelos de programación paralela de memoria compartida.

#### Palabras clave

Paralelización especulativa, Especulación a nivel de Thread, Paralelización optimista, Scheduling, Rendimiento, Evaluación.

#### **Abstract**

It is very likely that, in the next years, shared-memory systems with hundreds or even thousands of computational units will become commonplace. Since parallel programming is conceptually difficult, and to take advantage of these platforms, it is desirable to have compiling and/or runtime systems that automatically extract all the available parallelism of a sequential application. Although many parallel processing approaches have been developed in the last decades, most automatic parallelization proposals are focused on codes with no hurdles. Speculative parallelization (SP) techniques arise as a more general solution, allowing the parallel execution of any code, even in the presence of dependence violations. To ensure that, SP approaches rely on a runtime monitor responsible for ensuring that the results of the parallel execution match the expected output of the original, sequential code. This technique, based on the optimistic assumption that no dependences will arise when executing the code in parallel, launches threads that execute different fragments of the sequential code at the same time. If a dependence violation is detected, the offending threads are stopped and restarted with the correct values, thus ensuring that the execution follows sequential semantics.

Our contribution in this field includes (1) a new, easy-to-use speculative runtime library; (2) new proposals which allow to decrease the number of memory accesses involved in speculative operations, as well as some advice to decrement the memory footprint; (3) research on new scheduling methods focused on the dynamic management of chunks of iterations in speculative executions; (4) an hybrid approach which implements speculative parallelism using transactional memory to handle its critical sections; and (5) an analysis of the speculative techniques in one of the most state-of-the-art devices as are Intel Xeon Phi coprocessors.

Speculative parallelization is a lively research field. Our results show that these techniques have the potential of leading to considerable improvements in the performance of many applications. We expect that this work, among others, will foster the use of SP-based solutions in commercial compilers and shared-memory parallel programming models.

### **Keywords**

Speculative parallelization, Thread-Level Speculation, Optimistic parallelism, Scheduling, Performance, Evaluation.

## Agradecimientos

Para llevar a cabo una tesis doctoral, hace falta mucho más que matricularse. Durante su desarrollo hay muchos momentos buenos, pero también hay otros en que se hace muy duro seguir adelante. Con estas líneas quiero agradecer a todos los que celebraron conmigo los buenos ratos, pero sobretodo a los que me ayudaron a levantarme en cada caída y me animaron cuando más lo necesitaba.

Primero, quiero acordarme de mis compañeros de fatigas, Yuri, Sergio, Javier, Héctor y Ana, por esas charlas sobre nuestro futuro, por el apoyo, las risas y sobretodo el buen ambiente creado en el grupo. También mencionar a Arturo que ha sido un excelente tutor y una gran persona.

También quiero agradecer a mi familia y amigos por estar ahí, especialmente a mi hermano Juan Cruz, y mi amigo Pablo con los que he compartido tantos, y tan buenos momentos. También quiero destacar a mis abuelos, cuya pérdida ha sido el momento más agrio de mi vida. Sólo puedo agradecerles el haber estado conmigo siempre, ayudando a mi madre en todo lo posible. Sin ellos no se si hubiera llegado hasta aquí, y desde luego les recordaré siempre.

Pero para ser justos hay tres personas que merecen unos agradecimientos mucho más concretos.

Diego R. Llanos Ferraris, quiero agradecerle que haya confiado en mí desde el principio. Ese principio que data de Febrero de 2011 cuando llamé a la puerta de su despacho para empezar un proyecto de fin de carrera que me permitió obtener la Ingeniería Técnica. Cuando después, apostó por mí de nuevo al asignarme un trabajo de fin de grado con un tema tan importante para él, y que fue el germen de esta tesis doctoral, el desarrollo de la librería especulativa. También por darme todo su apoyo durante el siempre complicado máster. Con respecto al final del camino, esta tesis, decir que ha sido un placer y un orgullo trabajar bajo su tutela, siendo comprensivo, exigente, y enseñadome perfectamente cómo ser un buen investigador. Si me permites, te animo a que sigas investigando y formando doctores puesto que la ciencia y la Universidad de Valladolid lo agradecerán. Además sería injusto no recordar todo el esfuerzo económico que ha hecho por mí. Y es que, junto con Arturo, han intentado que realice la tesis con todos sus medios, me habéis apoyado cuando me quedaba a las puertas de una beca, e incluso cuando me equivocaba cumplimentando los papeles. Deciros que siempre he intentado reconocer vuestros esfuerzos, que me han motivado, y me han llevado a finalizar esta tesis doctoral, nunca lo olvidaré. Gracias a Diego me voy de la Universidad

con una tesis doctoral, unas cuantas publicaciones, y lo más importante un amigo para toda la vida.

Pilar López Alonso, a ella le quiero dar la gracias por todo lo que ha hecho por mí. Y es que aparte de darme la vida, me ha enseñado todos los valores importantes de la misma. A través de esfuerzo y constancia ha conseguido sacar a sus hijos adelante, unos hijos que le debemos todo lo que somos. Quiero darle las gracias por todo su apoyo incondicional en los buenos y malos momentos. El mundo sería perfecto si lo formase más gente como tú, espero que algún día pueda merecerme que alguien esté tan orgulloso de mí, como lo estoy yo de tí.

Tania Alonso Sambade, porque ha sido mucho más que una novia para mí. Desde que comencé mi andadura por la universidad, ella ha sido mi novia, mi mejor amiga y se podría decir que mi psicóloga. Me has apoyado, escuchado, aconsejado en los momentos difíciles, y celebrado conmigo las buenas noticias. Gracias por ser como eres y estar conmigo siempre, esta tesis no hubiera sido posible si tú no hubieras estado a mi lado. Las cosas pueden cambiar, pero tu y yo seguimos siempre juntos.

Álvaro Estébanez López

## Contents

| Re | esume | n de la | tesis                                                                 | 1  |

|----|-------|---------|-----------------------------------------------------------------------|----|

|    | R.1   | Motiva  | ación                                                                 | 2  |

|    |       | R.1.1   | Sistemas multiprocesador                                              | 2  |

|    |       | R.1.2   | Violaciones de dependencia                                            | 3  |

|    |       | R.1.3   | Paralelización de códigos con dependencias                            | 4  |

|    |       | R.1.4   | Paralelización especulativa                                           | 4  |

|    | R.2   | Objeti  | vos de esta tesis                                                     | 6  |

|    |       | R.2.1   | Pregunta de investigación                                             | 7  |

|    | R.3   | Metod   | lología de investigación                                              | 8  |

|    | R.4   | Resum   | nen de contribuciones                                                 | 9  |

|    |       | R.4.1   | Desarrollar un estudio en profundidad del estado del arte en paralel- |    |

|    |       |         | ización especulativa                                                  | 10 |

|    |       | R.4.2   | Combinar un librería especulativa con un compilador                   | 10 |

|    |       | R.4.3   | Mejorar el rendimiento de las operaciones involucradas en una         |    |

|    |       |         | librería especulativa                                                 | 11 |

|    |       | R.4.4   | Combinar nuestro sistema especulativo con otras técnicas paralelas    | 11 |

|    | R.5   | Respu   | esta a la pregunta de investigación y conclusiones                    | 12 |

|    | R.6   | Agrado  | ecimientos                                                            | 13 |

| 1  | Intr  | oductio | o <b>n</b>                                                            | 15 |

|    | 1.1   | Motiva  | ation                                                                 | 16 |

|    |       | 1.1.1   | Multiprocessor computers                                              | 16 |

|    |       | 1.1.2   | Dependence violations                                                 | 18 |

|    |       | 1.1.3   | Parallelization of codes with dependences                             | 20 |

|    |       | 1.1.4   | Speculative Parallelization                                           | 21 |

|    | 1.2   | Object  | tives of this dissertation                                            | 24 |

|    |       | 1.2.1   | Research question                                                     | 24 |

|    |       | 1.2.2   | Milestones                                                            | 24 |

|    | 1.3   | Resear  | ch methodology                                                        | 26 |

|    | 1 /   | Dogun   | nant atmicture                                                        | 27 |

## X | CONTENTS

| 2 | State | e of the | art                                                   | 29 |

|---|-------|----------|-------------------------------------------------------|----|

|   | 2.1   | Introd   | luction                                               | 30 |

|   | 2.2   | Source   | es of TLS and design choices                          | 30 |

|   |       | 2.2.1    |                                                       | 31 |

|   |       | 2.2.2    | Drawbacks of TLS                                      | 33 |

|   |       | 2.2.3    |                                                       | 33 |

|   |       | 2.2.4    | <del>_</del>                                          | 34 |

|   | 2.3   | Precui   | =                                                     | 37 |

|   | 2.4   | Hardw    | vare-based approaches                                 | 38 |

|   | 2.5   | Softwa   | are-based approaches                                  | 38 |

|   |       | 2.5.1    | Solutions relying on compile-time and runtime support | 39 |

|   |       | 2.5.2    | Solutions relying on programming abstractions         | 42 |

|   |       | 2.5.3    | Other proposals                                       | 46 |

|   |       | 2.5.4    |                                                       | 47 |

|   |       | 2.5.5    | STLS on distributed-memory systems                    | 49 |

|   |       | 2.5.6    | STLS using GPUs                                       | 49 |

|   | 2.6   | Other    | studies related to TLS                                | 49 |

|   |       | 2.6.1    |                                                       | 49 |

|   |       | 2.6.2    |                                                       | 50 |

|   |       | 2.6.3    |                                                       | 51 |

|   |       | 2.6.4    |                                                       | 51 |

|   | 2.7   | Limits   | s to TLS                                              | 51 |

|   | 2.8   | Concl    | usions                                                | 52 |

| 3 | The   | ATLaS    | runtime system                                        | 53 |

|   | 3.1   | Proble   | em description                                        | 54 |

|   | 3.2   |          |                                                       | 55 |

|   |       | 3.2.1    |                                                       | 56 |

|   |       | 3.2.2    |                                                       | 57 |

|   |       | 3.2.3    |                                                       | 57 |

|   |       | 3.2.4    |                                                       | 57 |

|   | 3.3   | Main l   |                                                       | 58 |

|   | 3.4   | Our no   | ew TLS library                                        | 59 |

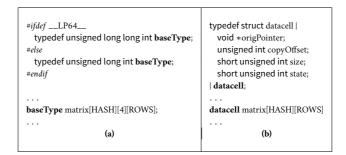

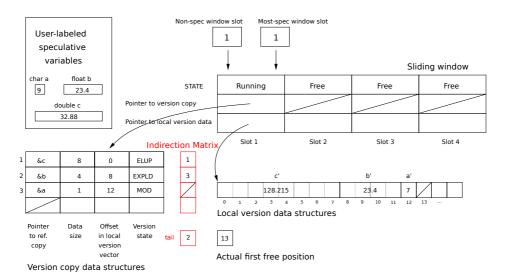

|   |       | 3.4.1    | Data structures                                       | 59 |

|   | 3.5   | New s    | peculative operations                                 | 60 |

|   |       | 3.5.1    | Speculative reads                                     | 60 |

|   |       | 3.5.2    |                                                       | 64 |

|   |       | 3.5.3    |                                                       | 69 |

|   |       | 3.5.4    | -                                                     | 70 |

|   | 3.6   | Perfor   |                                                       | 78 |

|   |       | 3.6.1    |                                                       | 78 |

|   |      | 3.6.2 Keeping version copies: A hash-based solution 82   |

|---|------|----------------------------------------------------------|

|   |      | 3.6.3 Additional improvements 84                         |

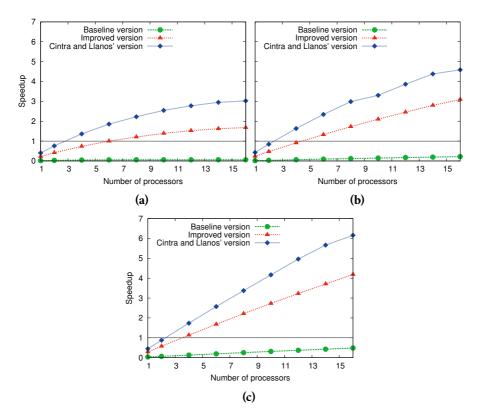

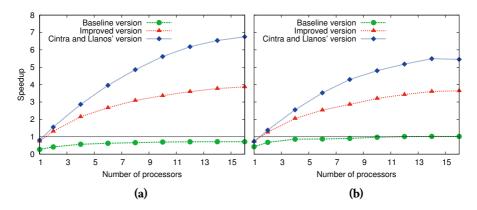

|   | 3.7  | Experimental evaluation                                  |

|   |      | 3.7.1 Experimental setup                                 |

|   |      | 3.7.2 Experimental results                               |

|   | 3.8  | Conclusions                                              |

| 4 | The  | ATLaS framework 95                                       |

|   | 4.1  | Problem description                                      |

|   | 4.2  | Compilation phase description                            |

|   |      | 4.2.1 Semantics of Aldea et al.'s speculative clause     |

|   |      | 4.2.2 Compiler support for the <i>speculative</i> clause |

|   | 4.3  | Experimental evaluation                                  |

|   |      | 4.3.1 Benchmark evaluation                               |

|   |      | 4.3.2 Effectiveness of the ATLaS runtime library 105     |

|   | 4.4  | Conclusions                                              |

| 5 | Sche | duling strategies for TLS 109                            |

| 3 | 5.1  | Problem description                                      |

|   | 5.2  | Classical scheduling alternatives                        |

|   | 3.2  | 5.2.1 Self scheduling                                    |

|   |      | 5.2.2 Dynamic scheduling                                 |

|   | 5.3  | Scheduling iterations under TLS                          |

|   | 5.4  | Moody Scheduling: Design guidelines                      |

|   | 5.5  | Moody Scheduling function definition                     |

|   | 5.6  | Dynamic and Adaptive Implementations                     |

|   | 5.7  | Experimental evaluation                                  |

|   | 3.7  | 5.7.1 Environment setup                                  |

|   |      | 5.7.2 Experimental results                               |

|   | 5.8  | Conclusions                                              |

|   | 3.0  | Conclusions                                              |

| 6 |      | and Transactional Memory 123                             |

|   | 6.1  | Problem description                                      |

|   | 6.2  | Background                                               |

|   |      | 6.2.1 Transactional Memory in a Nutshell                 |

|   |      | 6.2.2 Brief review of software TM libraries              |

|   |      | 6.2.3 Transactional Synchronization Extensions           |

|   |      | 6.2.4 TLS-TM hybrid approaches                           |

|   | 6.3  | Comparison of TM and TLS                                 |

|   | 6.4  | Critical sections in ATLaS                               |

|   |      | 6.4.1 Location                                           |

|   | 6.5  | Benchmarks used                                          |

|   | 6.6  | Protecting data accesses: OpenMP critical vs. TM                             | 33         |

|---|------|------------------------------------------------------------------------------|------------|

|   | 6.7  | Experimental results                                                         | 40         |

|   |      | 6.7.1 Experimental setup                                                     | 40         |

|   |      | 6.7.2 Results for OpenMP, STM and HTM                                        | 41         |

|   | 6.8  | Conclusions                                                                  | 41         |

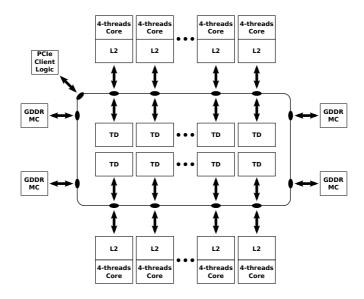

| 7 | TLS  | and Xeon Phi coprocessors                                                    | 45         |

|   | 7.1  | Problem description                                                          | 46         |

|   | 7.2  | Intel Xeon Phi in a nutshell                                                 | 46         |

|   |      | 7.2.1 Internal details                                                       | 47         |

|   |      | 7.2.2 Use of the Xeon Phi                                                    | 47         |

|   | 7.3  | Experimental evaluation                                                      | 48         |

|   |      | 7.3.1 Environmental setup                                                    | 49         |

|   | 7.4  | Experimental results                                                         | 49         |

|   |      | 7.4.1 Scalability                                                            | 49         |

|   |      | 7.4.2 Oversubscription                                                       | 49         |

|   |      | 7.4.3 Absolute performance                                                   | 51         |

|   | 7.5  | Related work: TLS and the Xeon Phi coprocessor                               | 52         |

|   |      | 7.5.1 Hardware improvements to benefit software TLS                          | 54         |

|   |      | 7.5.2 Studies related to the Xeon Phi coprocessor                            | 54         |

|   | 7.6  | Conclusions                                                                  | 55         |

| 8 | Con  | clusions 15                                                                  | <b>5</b> 7 |

|   | 8.1  | Summary of results and contributions                                         | 58         |

|   |      | 8.1.1 Goal 1: Deep study of the state-of-the-art in TLS                      | 58         |

|   |      | 8.1.2 Goal 2: Combine a TLS library with a compiler                          | 58         |

|   |      | 8.1.3 Goal 3: Improve operations involved in a TLS runtime library 15        | 59         |

|   |      | 8.1.4 Goal 4: Test a TLS runtime library with other parallel techniques . 16 | 50         |

|   | 8.2  | Answer to the research question                                              | 50         |

|   | 8.3  | Future work                                                                  | 51         |

| A | Bene | chmarks description 16                                                       | 53         |

|   | A.1  | Randomized incremental algorithms                                            | 54         |

|   |      | A.1.1 Minimum enclosing circle                                               | 55         |

|   |      | A.1.2 Convex hull                                                            | 55         |

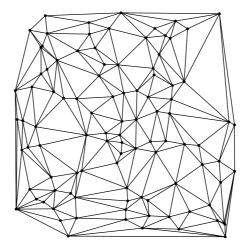

|   |      | A.1.3 Delaunay triangulation                                                 | 56         |

|   | A.2  | TREE benchmark                                                               | 58         |

|   | A.3  | Synthetic benchmarks                                                         | 59         |

|   |      | A.3.1 Complete                                                               |            |

|   |      | A.3.2 Tough                                                                  | 59         |

|   |      | A.3.3 Fast                                                                   | 59         |

| В   | Exar   | Example of use of the TLS library |                                                           |     |  |  |  |

|-----|--------|-----------------------------------|-----------------------------------------------------------|-----|--|--|--|

|     | B.1    | Initialia                         | zation of the engine                                      | 174 |  |  |  |

|     | B.2    | Use of                            | the engine and variable settings                          | 174 |  |  |  |

|     | B.3    | An exa                            | mple of use                                               | 175 |  |  |  |

|     |        | B.3.1                             | Sequential application                                    | 176 |  |  |  |

|     |        | B.3.2                             | Speculative Parallelization of the sequential application | 178 |  |  |  |

|     |        | B.3.3                             | Summary                                                   | 181 |  |  |  |

| Bil | bliogr | aphy                              |                                                           | 183 |  |  |  |

# List of Figures

| 1.1        | Loop without dependences between iterations                            | 17 |

|------------|------------------------------------------------------------------------|----|

| 1.2        | Loop with a dependence between two iterations                          | 17 |

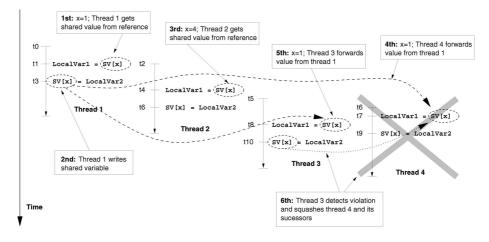

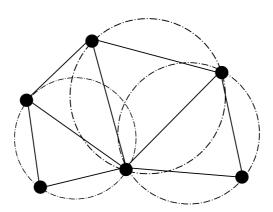

| 1.3        | Example of speculative parallelization                                 | 23 |

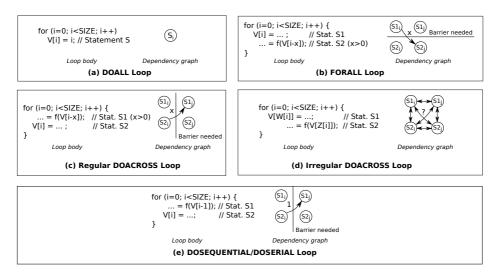

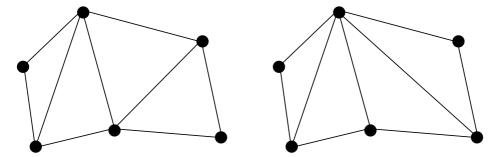

| 2.1        | Different types of loops according to the presence of data dependences | 31 |

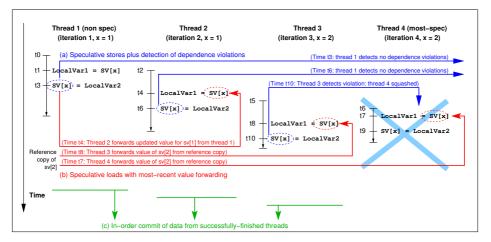

| 3.1        | Example of speculative load and store operations                       | 56 |

| 3.2        | Summary of operations carried out by a runtime TLS library             | 57 |

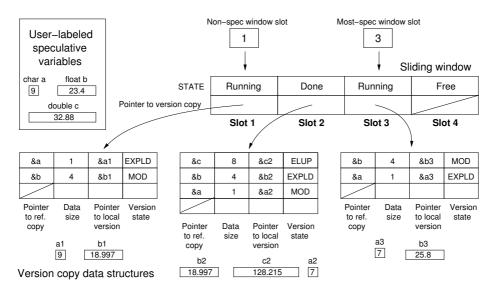

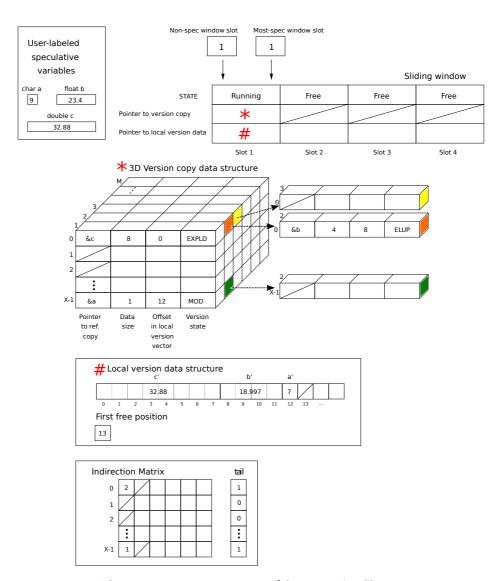

| 3.3        | Data structures of our new speculative library                         | 59 |

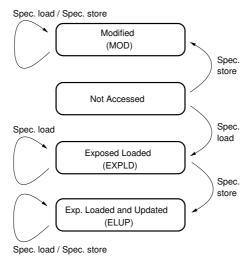

| 3.4        | State transition diagram for speculative data                          | 61 |

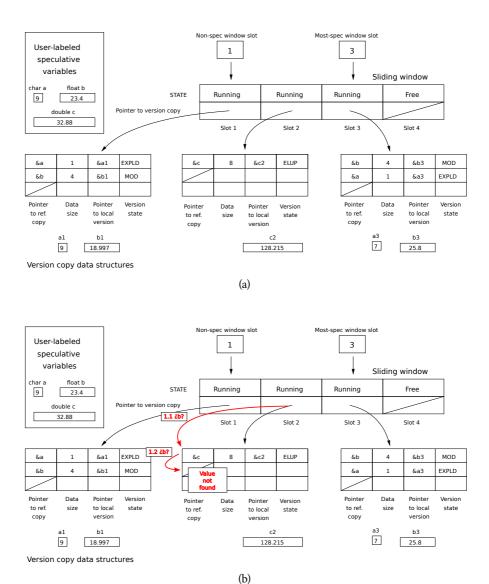

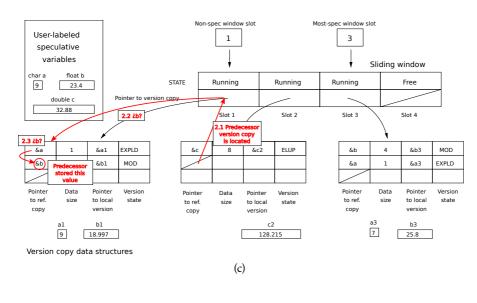

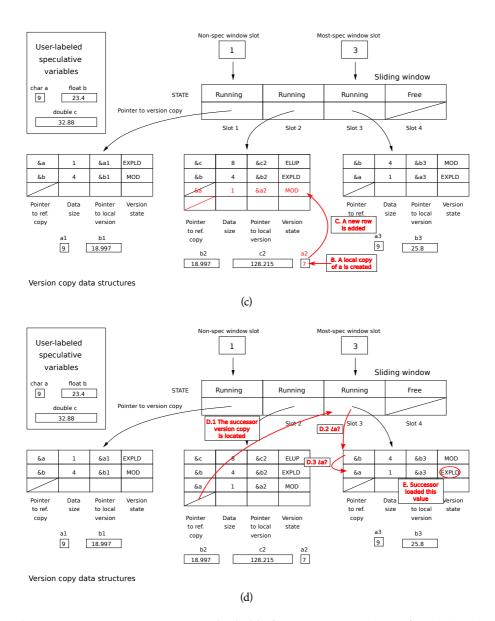

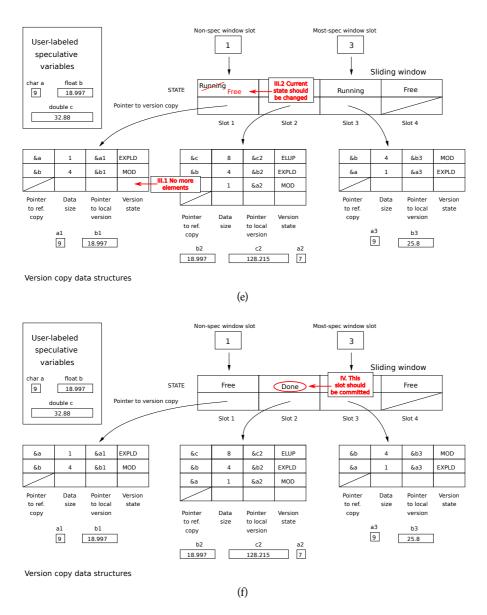

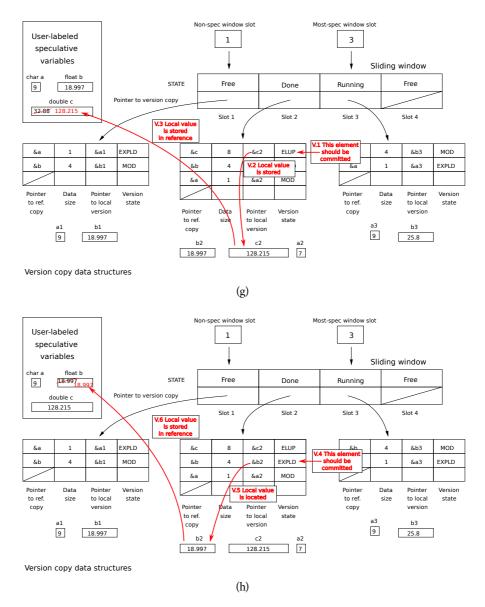

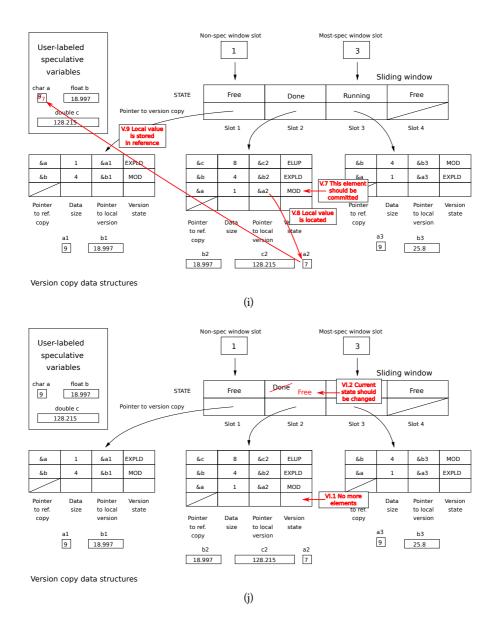

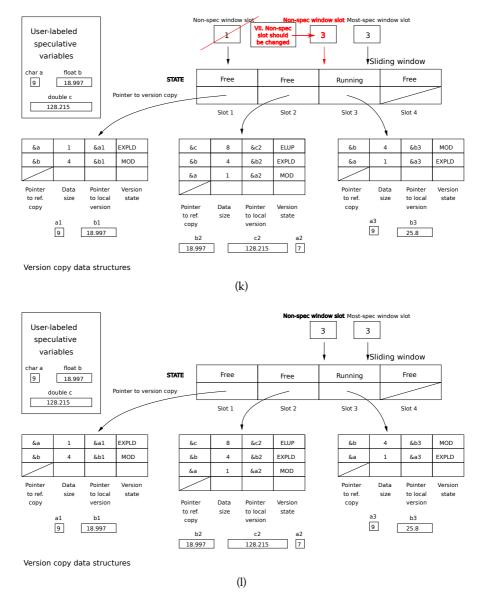

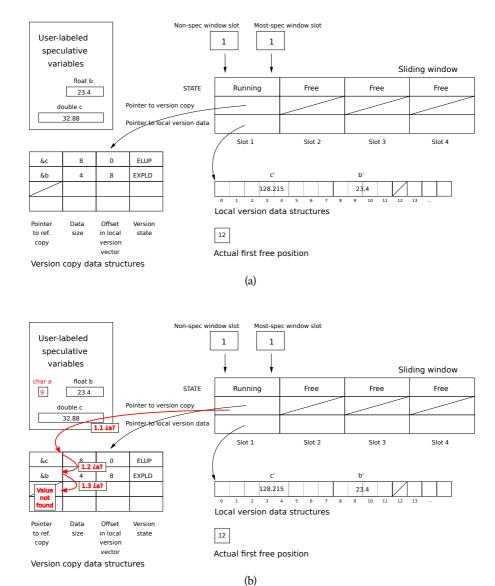

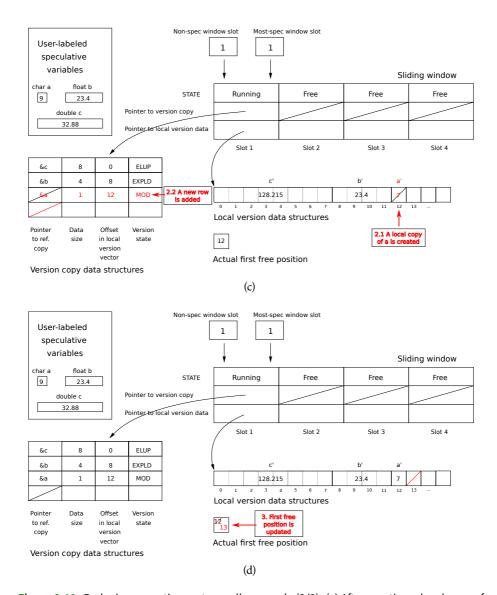

| 3.5        | Speculative load example $(1/2)$                                       | 62 |

| 3.6        | Speculative load example (2/2)                                         | 63 |

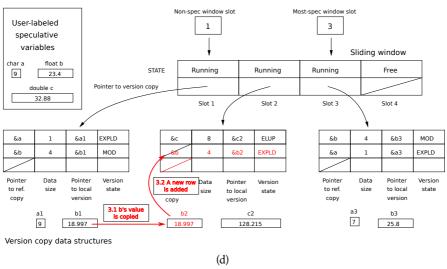

| 3.7        | Speculative store example $(1/3)$                                      | 66 |

| 3.8        | Speculative store example (2/3)                                        | 67 |

| 3.9        | Speculative store example $(3/3)$                                      | 68 |

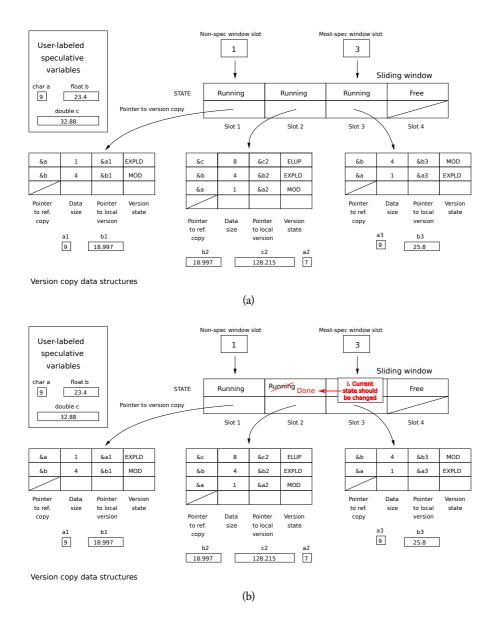

| 3.10       | Speculative commit example (1/6)                                       | 71 |

| 3.11       | Speculative commit example (2/6)                                       | 72 |

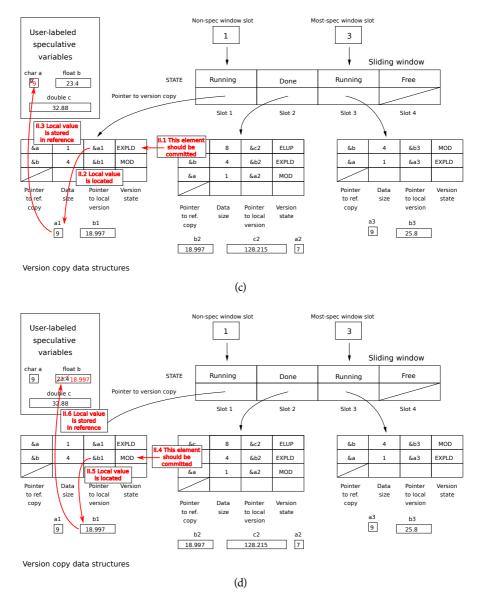

| 3.12       | Speculative commit example (3/6)                                       | 73 |

| 3.13       | Speculative commit example (4/6)                                       | 74 |

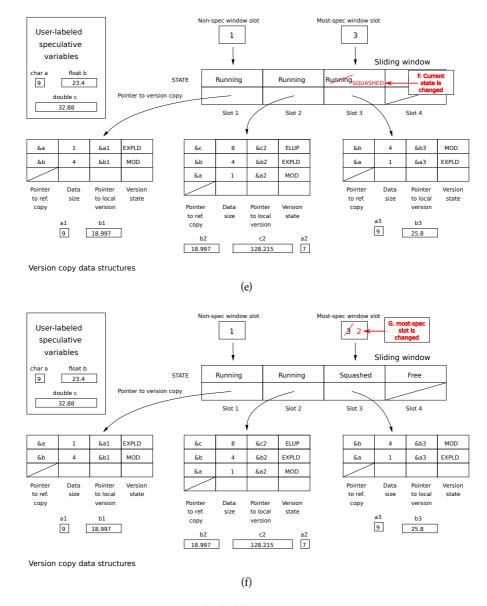

| 3.14       | Speculative commit example (5/6)                                       | 75 |

| 3.15       | Speculative commit example (6/6)                                       | 76 |

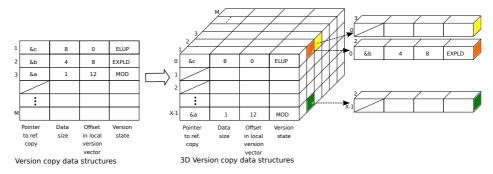

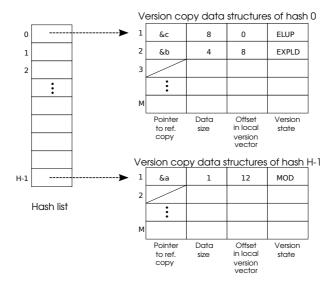

| 3.16       | Hash-based version copy data structures with three dimensions          | 82 |

| 3.17       | Hash-based version copy data structures                                | 83 |

| 3.18       | Reducing operating system calls example (1/2)                          | 86 |

| 3.19       | Reducing operating system calls example (2/2)                          | 87 |

| 3.20       | Implementation of a static example of the data structure               | 88 |

| 3.21       | Structures with the Indirection Matrix                                 | 89 |

| 3.22       | Performance comparison for 2D-Hull benchmark                           | 91 |

| 3.23       | Performance comparison for Delaunay benchmark                          | 92 |

|            | Current appearance of the TLS runtime library                          | 94 |

| <b>4</b> 1 | Example of loop parallelization with OpenMP                            | 96 |

## XVI | LIST OF FIGURES

| 4.2  | Parallelization of a loop that cannot be parallelized with OpenMP  | 97  |

|------|--------------------------------------------------------------------|-----|

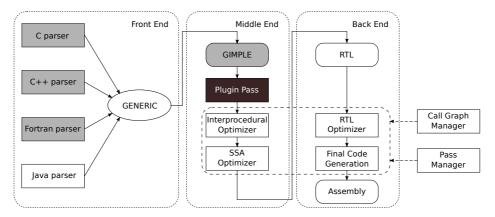

| 4.3  | GCC Compiler Architecture                                          | 100 |

| 4.4  | Loop transformation that allow its speculative execution           | 102 |

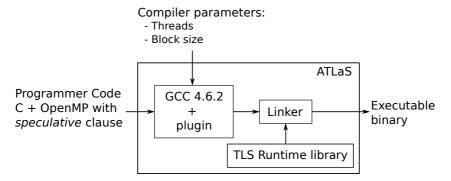

| 4.5  | Overview of the code generation process for the speculative clause | 103 |

| 4.6  | Performance achieved with the benchmarks considered                | 104 |

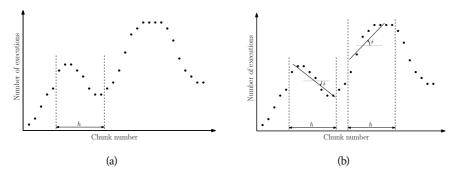

| 5.1  | Execution profile and example of the linear regression used        | 115 |

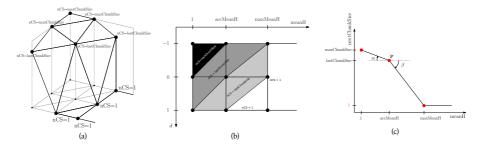

| 5.2  | Graphical representation of the Moody scheduling                   | 117 |

| 5.3  | Dynamic and Adaptive approaches of Moody Scheduling                | 118 |

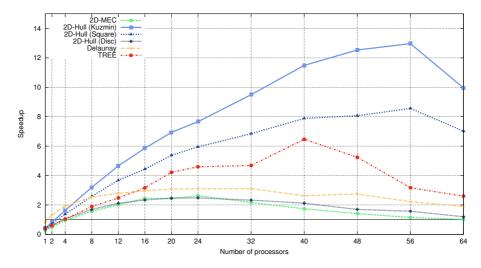

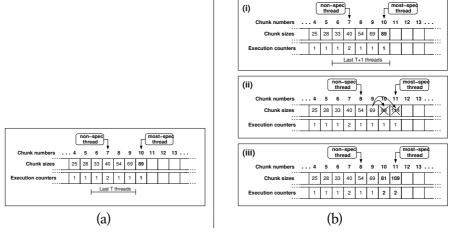

| 5.4  | Performance comparison for some benchmarks tested                  | 121 |

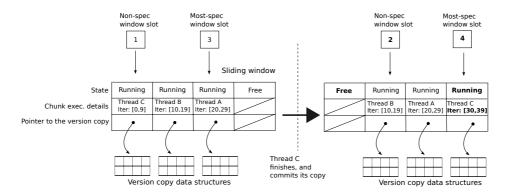

| 6.1  | Updating the sliding window that handles the speculative execution | 129 |

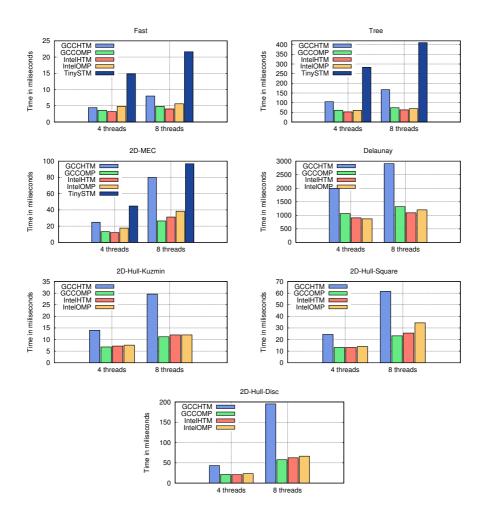

| 6.2  | Accumulated time in miliseconds required by critical sections      | 139 |

| 6.3  | Speedups by number of processors for each benchmark tested         | 142 |

| 7.1  | Overview of the microarchitecture of an Intel Xeon Phi coprocessor | 148 |

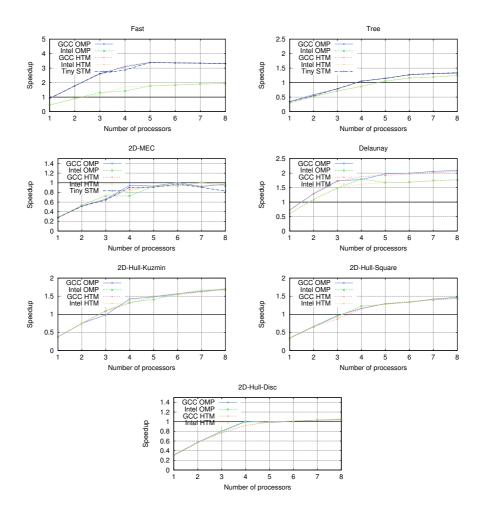

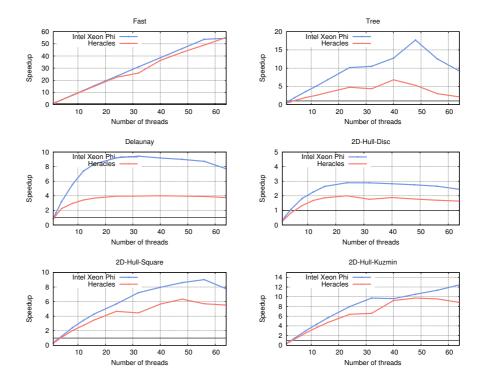

| 7.2  | Speedups by number of processors for each benchmark tested         | 150 |

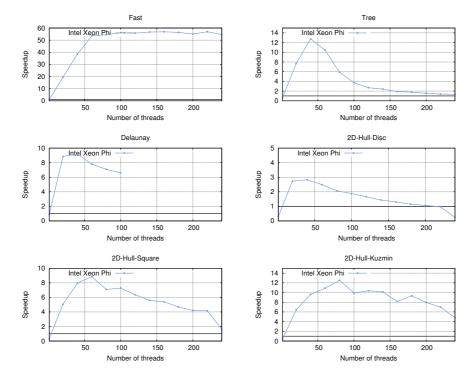

| 7.3  | Speedups on the Intel Xeon Phi coprocessor                         | 151 |

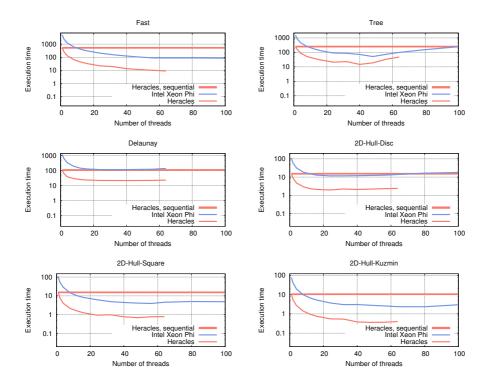

| 7.4  | Execution time with respect to the number of threads               | 153 |

| A.1  | Minimum enclosing circle defined by three points                   | 165 |

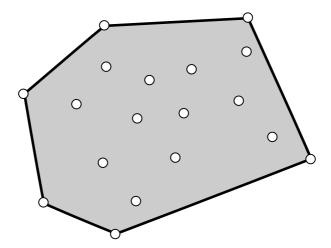

| A.2  | Convex hull of a set of points                                     | 166 |

| A.3  | Delaunay: Two different triangulations with the same set of points | 167 |

| A.4  | Delaunay triangulation of a set of 6 points                        | 167 |

| A.5  | Delaunay triangulation of a set of 100 points                      | 168 |

| 11.5 | Delauliay triangulation of a set of 100 points                     | 100 |

## List of Tables

| 1.1  | Timing of the loop with the values of each variable at any time              | 21  |

|------|------------------------------------------------------------------------------|-----|

| 3.1  | Profile of main functions with a single thread in the baseline TLS library . | 81  |

| 3.2  | Profile of main functions with eight threads in the baseline TLS library     | 81  |

| 3.3  | Profile of main functions with a single thread in the hash-based version     | 84  |

| 3.4  | Profile of main functions with eight threads in the hash-based version       | 84  |

| 4.1  | Percentages of parallelism effectively exploited by ATLaS                    | 106 |

| 5.1  | Changes on the following chunk sized according to $d$ and mean H $$          | 116 |

| 5.2  | Characteristics of the algorithms and input sizes used                       | 119 |

| 6.1  | Number of accesses to each protected zone                                    | 132 |

| 6.2  | Percentages of potentially parallelism for the benchmarks                    | 132 |

| 6.3  | Time in critical sections using GCC HTM and GCC omp critical                 | 135 |

| 6.4  | Time in critical sections using Intel HTM and ICC omp critical               | 135 |

| 6.5  | Time in critical sections using Intel HTM and Tiny STM                       | 136 |

| 6.6  | Time in critical sections using GCC HTM and Tiny STM                         | 136 |

| 6.7  | Time in critical sections using GCC OMP and Tiny STM                         | 137 |

| 6.8  | Time in critical sections using Intel OMP critical and Tiny STM              | 137 |

| 6.9  | Time in critical sections with an execution of four threads                  | 138 |

| 6.10 | Time in critical sections with an execution of eight threads                 | 138 |

| 7.1  | Shared memory system and Intel Xeon Phi execution times                      | 152 |

# List of Listings

| 1.1 | Example of a code with private and shared variables                     | 18  |

|-----|-------------------------------------------------------------------------|-----|

| 1.2 | Example of Write-after-write dependence violation                       | 19  |

| 1.3 | Example of Write-after-read dependence violation                        | 19  |

| 1.4 | Example of Read-after-write dependence violation                        | 20  |

| 3.1 | Loop with a RAW dependence                                              | 55  |

| 3.2 | Vectors to measure time spend by each function                          | 79  |

| 3.3 | Additional code to measure the time spent by each function              | 79  |

| 3.4 | Vectors to measure calls and accesses done by specload()                | 80  |

| 3.5 | Additional code to measure calls and accesses done by specload<br>()    | 81  |

| A.1 | Code of the 'Complete' synthetic benchmark                              | 170 |

| A.2 | Code of the 'Tough' synthetic benchmark                                 | 171 |

| A.3 | Code of the 'Fast' synthetic benchmark                                  | 172 |

| B.1 | Example of manually speculative parallelization: Sequential application | 177 |

## Resumen de la tesis

D ESDE la aparición de los circuitos integrados, el rendimiento de los ordenadores ha crecido exponencialmente. Sin embargo, esta progresión terminó por toparse con ciertos límites impuestos por leyes físicas, tales como la disipación de calor, que obligaron a repensar el modelo de avance. Así, en lugar de seguir aumentando la frecuencia de los procesadores cada vez más, se optó por utilizar varias unidades computacionales (actuando como una sola) en el mismo chip, comenzando la era de los sistemas multiprocesador de memoria compartida. Sin embargo, para sacar rendimiento de una misma aplicación, el código secuencial debe ser o bien rescrito como un conjunto de tareas paralelas, o transformado automáticamente en código paralelo.

En este capítulo resumiremos la motivación de esta tesis doctoral, la metodología seguida, y los principales objetivos conseguidos. Además se enumerarán las conclusiones obtenidas.

### R.1 Motivación

Desde la aparición del primer microchip en 1971, el 4004 de Intel, con unos 3200 procesadores y una frecuencia de 104KHz [16, 122], los ordenadores han experimentado una evolución constante y vertiginosa. Así, el número de transistores por dispositivo ha crecido exponencialmente, con el consiguiente aumento en el rendimiento de los mismos. Sin embargo, a comienzos del siglo XXI, esta tasa de mejora se vió afectada por límites físicos, tales como la imposibilidad de extraer todo el calor producido por un chip de unos cuantos milímetros con un consumo superior a 100W.

Por estos motivos, los ingenieros tuvieron que repensar el modelo de progreso, comenzando a integrar varios procesadores en el mismo dispositivo. Esta solución se beneficia del incremento de transistores que pueden empaquetarse juntos y de la distribución del calor en puntos diferentes del chip. Por otro lado, también se logró disminuir el pico de frecuencia utilizado, por lo que los dispositivos que requieren un menor consumo de energía (como los que utilizan baterías) pudieron beneficiarse de este nuevo enfoque.

Sin embargo, por primera vez en la historia, un cambio de arquitectura no produjo automáticamente un aumento en el rendimiento de las aplicaciones subyacentes. Para aprovechar estas nuevas mejoras, los sistemas de memoria compartida deben ejecutar varias aplicaciones al mismo tiempo o utilizar versiones paralelas de aplicaciones secuenciales. Esta tesis doctoral se centra en el segundo problema, estudiando cómo una sola tarea puede ser ejecutada en paralelo por diferentes procesadores.

## R.1.1 Sistemas multiprocesador

Como se ha expuesto, las máquinas multinúcleo son capaces de ejecutar tanto varios programas a la vez, como solamente uno dividido en tareas más pequeñas. Para alcanzar mejoras en la ejecución de un programa secuencial con un ordenador multinúcleo, es necesario que los programas se puedan dividir en tareas independientes. Si las tareas tienen dependencias entre ellas y se ejecutan en un orden incorrecto, es más que probable que la ejecución produzca resultados erróneos.

Localizar aquellas partes de un código que podrían ejecutarse de forma independiente es una tarea tediosa y propensa a provocar errores porque se deben tener en cuenta factores como la sincronización para evitar resultados indeseados. Actualmente existen lenguajes específicos, así como extensiones de los lenguajes secuenciales y librerías de funciones centradas en facilitar el proceso de paralelización. Sin embargo, para paralelizar un programa secuencial el programador debe (a) conocer las características del hardware inherente, (b) entender el problema resuelto en el código, y (c) conocer el modelo de programación a utilizar. Además, desarrollar software paralelo para un arquitectura específica provocaría que éste no fuese portable a otras máquinas. Estos hechos hacen de la paralelización automática una idea muy atractiva.

Actualmente, existen algunos compiladores capaces de paralelizar fragmentos de código (principalmente los bucles). Sin embargo, los compiladores paralelos rehusan paralelizar un bucle si tienen la más mínima sospecha de que haya una violación de dependencia entre las instrucciones del bucle. Determinar o predecir qué instrucciones dependen de otras es una tarea compleja debido a la explosión combinatoria que provoca la existencia de múltiples flujos de control. Además, los valores de ciertas variables pueden no ser conocidos en tiempo de compilación, previniendo la paralelización. Estos hechos son los que más limitan la paralización en tiempo de compilación.

Cabe mencionar que existen ciertas herramientas para controlar estas situaciones, como las barreras, pero su uso limita de forma significativa el rendimiento, llegando a provocar que el código paralelo resultante sea incluso más lento que el código secuencial original.

### R.1.2 Violaciones de dependencia

Para entender mejor en qué consisten las violaciones de dependencia, debemos mencionar que éstas se clasifican de acuerdo a su uso. Así los modelos de programación paralela compartida clasifican las variables como *compartidas* o *privadas*.

Las variables privadas son aquellas que son escritas siempre antes de ser leídas en una misma iteración. Como se puede deducir, el ámbito de este tipo de variables es una misma iteración, y no más allá de ella. Por otro lado, el ámbito de las variables compartidas se extiende a varias iteraciones, e incluso a todas. Por lo tanto, si un *thread* utiliza una variable compartida, y más tarde otro *thread* de una iteración *previa* escribe un valor nuevo en ella, se producirá una violación de dependencia.

Como puede deducirse, un bucle que sólo utiliza variables privadas y variables compartidas de sólo lectura es paralelizable. Por el contrario, aquellos bucles cuyas instrucciones realizan operaciones tanto de lectura, como de escritura sobre variables compartidas probablemente darán lugar a violaciones de dependencia en ejecuciones paralelas.

### Tipos de violaciones de dependencia

Hay tres tipos de dependencias de datos entre iteraciones:

- Escritura-tras-escritura: Este tipo de violaciones de dependencia se producen cuando una variable se escribe en dos iteraciones diferentes, sin lecturas entre las escrituras. Así, una ejecución desordenada de las iteraciones producirá una violación de dependencia, ya que el valor final de la variable podría no ser correcto.

- Escritura-tras-lectura: Este tipo de dependencia de datos aparecen cuando una variable local que ha sido leída previamente en una iteración previa se escribe en una iteración posterior. De nuevo, una ejecución paralela desordenada puede provocar una violación de dependencia.

Lectura-tras-escritura: Este tipo de dependencia (la más peligrosa de todas) se produce cuando una variable se escribe con un valor que va a ser leído más tarde en iteraciones sucesivas. Si ambas operaciones se llevan a cabo en un orden incorrecto, el valor leído puede ser incorrecto.

### R.1.3 Paralelización de códigos con dependencias

Aunque el problema de paralelizar bucles con dependencias puede ser algo arduo de resolver, existen algunas técnicas capaces de paralelizar tales códigos. Mientras las soluciones clásicas rechazan paralelizar cualquier código que pueda provocar violaciones de dependencia, otras propuestas como el *Inspector-Ejecutor* o la *Paralelización Especulativa* lidian con estas situaciones. Estas técnicas confían en que la ejecución seguirá un orden secuencial, detectando cualquier eventual violación de dependencia y llevando a cabo las operaciones requeridas para conseguir los resultados correctos. A continuación, describiremos ambas técnicas.

#### Inspector-Ejecutor

Esta técnica [165] trata de paralelizar bucles que no pueden ser paralelizados por un compilador. Su funcionamiento se basa en encontrar dependencias entre las iteraciones de un bucle mediante el uso de un bucle inspector extraído del bucle original. El bucle inspector trata de asignar todas las iteraciones dependientes entre sí al mismo procesador para que la ejecución preserve un orden correcto. Más tarde, un bucle ejecutor lanza las iteraciones en paralelo. Aunque esta técnica puede ser aplicada a cualquier tipo de bucle, su uso sólo se aconseja si el tiempo de procesamiento del bucle inspector es bastante menor que el tiempo de ejecución del bucle original. Desafortunadamente, ésta no suele ser la tónica general debido al coste de inspeccionar los bucles que utilizan aritmética de punteros, siguen flujos de control complejos, o dependen de datos de entrada.

## R.1.4 Paralelización especulativa

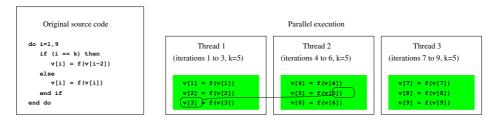

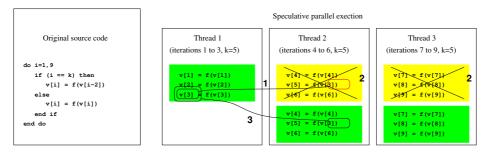

La paralelización especulativa [49, 73, 96, 144, 273] trata de extraer paralelismo de bucles que no pueden paralelizarse en tiempo de ejecución. En otras palabras, esta técnica trata de paralelizar códigos con dependencias. Ésta técnica asume de forma optimista que no se producirán violaciones de dependencia y ejecuta los bucles en paralelo. Mientras tanto, un monitor software o hardware se encarga de controlar que la ejecución sea correcta, realizando las correcciones oportunas de ser necesario.

Aunque los mecanismos basados en hardware no añaden ni cambios en el código, ni sobrecargas en la ejecución especulativa, requieren cambios en el procesador y/o los subsistemas caché. Por otro lado, los sistemas basados en software requieren cambios en el código original de los bucles, incluyendo la adición de algunas instrucciones que controlan la ejecución y vigilan la aparición de violaciones de dependencia. A pesar de la sobrecarga de rendimiento inherente a estas instrucciones, las soluciones basadas en software pueden

implementarse en los sistemas actuales de memoria compartida sin ningún cambio en el hardware subyacente. Esta tesis doctoral se centra en la rama software de este campo.

#### Modelo de ejecución

Recordemos que, en caso de detectarse una violación de dependencia, los resultados calculados hasta el momento por el *thread* que utilizó el valor incorrecto de la variable y sus sucesores ya no son válidos y deben descartarse, siendo estos *threads* re-ejecutados en orden. Tras resolver este problema la paralelización optimista puede continuar. Obviamente, se este proceso de parada y re-ejecución requiere una gran cantidad de tiempo adicional, por tanto, cuantas menos violaciones de dependencia se produzcan, mejores resultados obtendremos en términos de rendimiento.

La solución más recurrente utilizada por las soluciones software para evitar tantas violaciones de dependencia como sea posible se denomina *forwarding*. Si un *thread* tiene que leer un valor de una variable compartida, debe leer el valor más reciente almacenado en la misma, para lo cual copia el valor más reciente de los disponibles en los *threads* predecesores al *thread* consumidor. En caso de que se necesite escribir sobre una variable compartida, tras la escritura, el *thread* debe comprobar si un *thread* sucesor ha utilizado un valor desfasado, para detectar tan pronto como sea posible las violaciones de dependencia que puedan surgir.

Otra solución típica adoptada por las soluciones software es el uso de una versión propia de los datos compartidos por cada *thread* en ejecución. Así, los *threads* sólo modifican sus propias copias de las variables compartidas, en lugar de la versión global. Cuando un *thread* finaliza la ejecución de su bloque de iteraciones, si no se ha producido ninguna violación de dependencia, los resultados se guardan en la variable global compartida por todos los *threads* (esta operación se conoce como consolidación). Por otro lado, si se produjese una violación de dependencia, todas las versiones locales con valores erróneos deben ser descartadas (esta operación se denomina *squash*). Después tanto el *thread* en cuestión, como sus sucesores deben comenzar de nuevo la ejecución ya que podrían haber utilizado un valor contaminado del *thread* que sufrió una violación de dependencia. La ventaja de utilizar copias locales es que la operación más frecuente (lecturas sobre variables compartidas) puede llevarse a cabo bastante rápido, siempre que exista una copia local. Nos gustaría destacar que este proceso de parada y re-ejecución conlleva un tiempo, por tanto, cuantas más violaciones de dependencia aparezcan, peores resultados se obtendrán con esta técnica.

#### Operaciones principales de ejecuciones especulativas

Los sistemas software de paralelización especulativa necesitan modificar el código fuente original de la aplicación en tiempo de compilación para realizar las siguientes tareas:

Operaciones especulativas de lectura y escritura: Cada thread tiene su propia versión de las variables compartidas, por lo que todas las operaciones de lectura y escritura en variables compartidas deben sustituirse por una función que también comprueba que no aparezca ninguna violación de dependencia.

- Consolidación de resultados: Al final de la ejecución correcta de un bloque de iteraciones, se debe llamar a una función para consolidar los resultados producidos y solicitar un nuevo bloque de iteraciones consecutivas.

- Reparto de bloques de iteraciones consecutivas: Las iteraciones deben distribuirse a lo largo

de todos los threads disponibles que intervienen en la ejecución especulativa. Esta tarea

se puede realizar siguiendo diferentes estrategias: distribuyendo bloques de iteraciones

de tamaño constante; adaptando el tamaño de los bloques a las características de cada

aplicación; o decidir dinámicamente el tamaño del siguiente bloque de iteraciones.

## R.2 Objetivos de esta tesis

El diseño de un sistema de paralelización especulativa competitivo requiere abordar diferentes problemas. Como hemos mencionado anteriormente, las operaciones involucradas en la paralelización especulativa influyen directamente en el rendimiento de una solución especulativa. Por lo tanto, mejorar todo lo posible los mecanismos de acceso a las estructuras de datos de una biblioteca de paralelización especulativa, influirá directamente en su rendimiento. Así, parece más que interesante, dedicar esfuerzos a acelerar los accesos a la estructura de datos.

Asimismo, hay muchos códigos con violaciones de dependencias que presentan aritmética de punteros, imposibilitando la aplicación de las técnicas clásicas de paralelización especulativa. Por ello, sería útil mejorar una biblioteca de paralelización especulativa para que soporte códigos con este tipo de variables.

Por otro lado, distribuir correctamente las iteraciones entre los *threads* de una ejecución especulativa, influye de forma muy significativa. Por ello, sería aconsejable trabajar en el desarrollo de nuevas técnicas de reparto dinámico de iteraciones basadas en la historia reciente de violaciones de dependencia, esperando reducir los tiempos de ejecución.

Además, aunque utilizan diferentes enfoques para resolver distintos problemas, hay bastantes similitudes entre la memoria transaccional y la paralelización especulativa. Por tanto, sería de utilidad combinar las dos soluciones de forma que las secciones críticas utilizadas en la paralelización especulativa se beneficien de la memoria transaccional.

Finalmente, con la llegada de las máquinas 'many-core', han surgido nuevas posibilidades respecto a las técnicas de paralelización. Respecto al estado del arte en el campo de la paralelización especulativa, no se habían realizado estudios previos relativos a los coprocesadores Intel Xeon Phi. Por tanto, sería deseable evaluar el comportamiento de una librería especulativa en un coprocesador Intel Xeon Phi.

### R.2.1 Pregunta de investigación

De acuerdo con los problemas identificados, podemos proponer las siguientes preguntas de investigación a resolver en esta tesis doctoral:

¿Es posible desarrollar un sistema de paralelización especulativa en tiempo de ejecución capaz de utilizar eficientemente estructuras de datos complejas, utilizar aritmética de punteros y tener en cuenta la tendencia de violaciones de dependencia producida hasta ahora para estimar el mejor tamaño de bloque a repartir? ¿Podría implementarse, dando lugar a buenos resultados experimentales, utilizando memoria transaccional y en una arquitectura con un gran número de núcleos como los coprocesadores Intel Xeon Phi?

Para contestar estas preguntas de investigación, necesitamos llevar a cabo algunos objetivos intermedios, más específicos:

#### Desarrollar un estudio en profundidad del estado del arte en paralelización especulativa

Establecer una base sólida de los problemas resueltos, los desafíos existentes y proponer una clasificación de las soluciones existentes en el campo especulativo.

Dado que durante la última década se han realizado multitud de trabajos relacionados con la paralelización especulativa, consideramos que realizar un análisis tanto de las soluciones conocidas, como de las menos conocidas será un buen punto de partida. Además ya que no existe un artículo que sintetice todo este conocimiento, hemos desarrollado un compendio de paralelización especulativa como parte de nuestra investigación.

#### Combinar un librería especulativa con un compilador

Proponer e implementar una librería de paralelización especulativa que puede ser combinada fácilmente con un compilador para obtener una herramienta general de paralelización especulativa.

Hasta donde tenemos entendido, los compiladores actuales no soportan ejecución especulativas automáticamente, en otras palabras, no pueden transformar un bucle directamente para paralelizarlo especulativamente. Por lo tanto, una de los objetivos de esta tesis doctoral es alcanzar este objetivo. Cabe mencionar que este propósito ha sido llevado a cabo con la inestimable ayuda del Dr. Sergio Aldea. Mientras su trabajo se centraba en el desarrollo de la parte del compilador, el nuestro se ha focalizado en la implementación de la librería especulativa que se acopla con su parte.

#### Mejorar el rendimiento de las operaciones involucradas en una librería especulativa

Encontrar un manera de reducir el tiempo requerida por las operaciones más costosas relacionadas con la librería especulativa.

Aunque el desarrollo de una librería especulativa en sí misma ya es una tarea bastante compleja, si no se logra obtener resultados mejores que los secuenciales, los esfuerzos realizados serán inútiles. Por tanto, mejorar tanto como sea posible el rendimiento de nuestra solución es algo más que recomendable. Así hemos descubierto como recorrer eficientemente las estructuras de datos involucradas en las principales operaciones de la librería, logrando una mejora de los procedimientos más pesados en términos de rendimiento. Para ello, hemos desarrollado algunas estructuras de datos que reducen tanto el espacio, como el tiempo requeridos por las soluciones clásicas.

Por otro lado, no hemos encontrado demasiados artículos que estudien el reparto de iteraciones en contextos de paralelización especulativa. Consecuentemente, buscar una solución eficiente, así como desarrollarla nos permitirá probar si el rendimiento se ve influido por este aspecto.

#### Combinar nuestro sistema especulativo con otras técnicas paralelas

Sugerir, implementar y probar soluciones híbridas basadas en nuestra librería especulativa y otras herramientas actuales.

Las técnicas paralelas están en constante evolución, proponiendo nuevos métodos y/o tecnologías. Por tanto, esta tesis doctoral no estaría completa sin combinar una librería de paralelización especulativa con otras técnicas paralelas para probar si combinándolas, se obtendrían mejoras. Por ello hemos combinado algunas de las técnicas más conocidas de memoria transaccional, con nuestra librería especulativa. Además, hemos adaptado el código de nuestro sistema a la interfaz de los coprocesadores Intel Xeon Phi.

## R.3 Metodología de investigación

Para el desarrollo de esta tesis doctoral se ha utilizado la metodología de investigación definida por Adrion [1]. Este enfoque, denominado método de investigación para ingeniería del software, adapta las fases clásicas del método científico hipotético-deductivo a la Informática. Así consta de cuatro fases diferentes que pueden repetirse cíclicamente hasta la consecución de los objetivos.

1. Observar las soluciones existentes.

Una vez elegido el campo de investigación donde se va a trabajar, es requisito obligatorio conocer el estado del mismo. De otra forma, se podrían desarrollar soluciones existentes, o algo que carezca de utilidad. Por ello, estudiaremos el campo de la especulación en profundidad.

#### 2. Proponer soluciones mejores.

Tras analizar toda la información, probablemente se localice un nuevo enfoque que mejore los existentes. Así, hemos propuesto una librería de paralelización especulativa capaz de ejecutar códigos complejos, que puede combinarse fácilmente con un compilador para facilitar enormemente su uso. Además, hemos desarrollado una estructura de datos capaz de reducir los accesos requeridos por las operaciones especulativas más costosas. También hemos detectado que los métodos de reparto de iteraciones no han sido suficientemente investigados en el contexto de la paralelización especulativa. Por ello, hemos desarrollado un algoritmo capaz de adaptarse dinámicamente al número de violaciones de dependencia que aparecen para asignar de forma más optimista (o pesimista) las iteraciones. Por último, sería útil combinar dos técnicas de paralelización optimista.

#### 3. Construir o desarrollar la solución.

Durante esta etapa se deben implementar las soluciones propuestas en la etapa anterior. Por tanto, hemos desarrollado la librería especulativa, así como el nuevo método de reparto de iteraciones. Además hemos combinado nuestra solución con otra técnica de paralelización optimista como es la memoria transaccional.

#### 4. Medir y analizar la nueva solución.

Por último, todo prototipo debe probarse para medir si lo realizado es útil o no. En nuestro caso hemos comparado las versiones paralelas contra las secuenciales. Para ello hemos utilizado tanto aplicaciones sintéticas, como aplicaciones de reales. Cabe mencionar que hemos utilizado varios tipos de máquinas, con una gran diversidad de procesadores, desde sistemas con memoria compartida, sistemas con memoria transaccional, hasta coprocesadores Intel Xeon Phi.

#### R.4 Resumen de contribuciones

A continuación exponemos las contribuciones de esta tesis doctoral ordenadas por objetivos, así como las publicaciones obtenidas con las mismas.

## R.4.1 Desarrollar un estudio en profundidad del estado del arte en paralelización especulativa

Hemos revisado la mayoría de las soluciones existentes en el campo de paralelización especulativa. Así hemos propuesto una clasificación para enmarcar todas ellas. Creemos que éste es un trabajo que nadie había realizado previamente, y que puede servir tanto para investigadores nóveles en este campo, como para veteranos. El trabajo realizado ha sido aceptado para su publicación en la siguiente revista:

Alvaro Estebanez, Diego R. Llanos y Arturo Gonzalez-Escribano. 'A survey on Thread-Level Speculation Techniques'. En: ACM Computing Surveys (CSUR). Accepted for publication

### R.4.2 Combinar un librería especulativa con un compilador

Hasta la fecha, no había ninguna solución centrada en combinar la paralelización especulativa con un compilador, hasta que Aldea et *al.* propusieron la suya [7]. Para ello utilizaron una librería de paralelización especulativa capaz tanto de ejecutar aplicaciones con operaciones complejas, como de manejar aritmética de punteros. Por lo tanto hemos implementado una librería capaz de combinarse con un compilador de manera transparente y ejecutar todo tipo de aplicaciones. Esta contribución ha sido publicada en los siguientes artículos:

- Alvaro Estebanez, Diego R. Llanos y Arturo Gonzalez-Escribano. 'Desarrollo de un motor de paralelización especulativa con soporte para aritmética de punteros'. En: Proceedings of the XXIII Jornadas de Paralelismo. Elche, Alicante, Spain: Servicio de Publicaciones de la Universidad Miguel Hernández, sep. de 2012. ISBN: 978-84-695-4471-6

- Sergio Aldea, Alvaro Estebanez, Diego R. Llanos y Arturo Gonzalez-Escribano. 'A New GCC Plugin-Based Compiler Pass to Add Support for Thread-Level Speculation into OpenMP'. English. En: Euro-Par 2014 Parallel Processing. Ed. por Fernando Silva, Inês Dutra y Vítor Santos Costa. Vol. 8632. Lecture Notes in Computer Science. Springer International Publishing, 2014, págs. 234-245. ISBN: 978-3-319-09872-2. DOI: 10.1007/978-3-319-09873-9\_20. URL: http://dx.doi.org/10.1007/978-3-319-09873-9\_20

- Sergio Aldea, Alvaro Estebanez, Diego R. Llanos y Arturo Gonzalez-Escribano. 'Una extensión para OpenMP que soporta paralelización especulativa'. En: Proceedings of the XXV Jornadas de Paralelismo. Valladolid, Spain, sep. de 2014. ISBN: 978-84-697-0329-3

- S. Aldea, A. Estebanez, D.R. Llanos y A. Gonzalez-Escribano. 'An OpenMP Extension that Supports Thread-Level Speculation'. En: *IEEE Transactions on Parallel and Distri*buted Systems, vol. PP, n.º 99, 2015, págs. 1-14. 2015. ISSN: 1045-9219. DOI: 10.1109/ TPDS.2015.2393870

Como resultado de nuestro objetivo anterior, y para incrementar el posible impacto de nuestra herramienta, hemos tratado de localizar y aliviar los principales cuellos de botella de la librería especulativa. Para ello, hemos propuesto una estructura de datos basada en un *hash* que permite decrementar el número de accesos involucrados en las operaciones especulativas. Esto que nos permitió mejorar considerablemente el rendimiento de nuestra librería.

Además, aunque el reparto de iteraciones es un campo ampliamente estudiado, los trabajos no se han centrado específicamente en la paralelización especulativa. Por tanto, tras revisar algunos de los algoritmos existentes, nos hemos dado cuenta de que no había soluciones focalizadas en obtener dinámicamente el mejor tamaño de bloque de iteraciones basándose en parámetros de ejecución. Así hemos desarrollado una técnica que utiliza las violaciones de dependencia acontecidas como factor determinante en la asignación del siguiente bloque de iteraciones. Estos logros han producido las siguientes publicaciones:

- Alvaro Estebanez, Diego R. Llanos y Arturo Gonzalez-Escribano. 'Improving the Perfomance of a Pointer-Based, Speculative Parallelization Scheme'. En: Proceedings of the 1st First Congress on Multicore and GPU Programming. PPGM'14. Granada, Spain, feb. de 2014. Also published in Annals of Multicore and GPU Programming, vol. 1, no. 1, 2014. 2014. issn: 2341-3158.

- Alvaro Estebanez, Diego R. Llanos y Arturo Gonzalez-Escribano. 'New Data Structures to Handle Speculative Parallelization at Runtime'. En: Proceedings of the 7th International Symposium on High-level Parallel Programming and Applications. HLPP '14. Amsterdam, Netherlands: ACM, 2014, págs. 239-258. Also published in International Journal of Parallel Programming, 2015, pp. 1-20. Springer US, 2015. issn: 0885-7458. doi: 10.1007/s10766-014-0347-0. url: http://dx.doi.org/10.1007/s10766-014-0347-0.

- Alvaro Estebanez, Diego R. Llanos, David Orden y Belen Palop. 'Moody Scheduling for Speculative Parallelization'. English. En: Euro-Par 2015: Parallel Processing. Ed. por Jesper Larsson Träff, Sascha Hunold y Francesco Versaci. Vol. 9233. Lecture Notes in Computer Science. Springer Berlin Heidelberg, 2015, págs. 135-146. ISBN: 978-3-662-48095-3. DOI: 10.1007/978-3-662-48096-0\_11. URL: http://dx.doi.org/10.1007/978-3-662-48096-0\_11

## R.4.4 Combinar nuestro sistema especulativo con otras técnicas paralelas

Para completar nuestro trabajo, hemos probado nuestra librería especulativa en otros contextos distintos a las máquinas de memoria compartida convencionales. Así hemos combinado la memoria transaccional con nuestra librería especulativa para comparar como influye el

uso de secciones críticas de forma convencional, o el uso de las transacciones software o hardware. Además hemos examinado el comportamiento de nuestro software con uno de los dispositivos más vanguardistas, un coprocesador Intel Xeon Phi. Este trabajo nos ha permitido publicar los siguientes artículos:

- Sergio Aldea, Alvaro Estebanez, Diego R. Llanos y Arturo Gonzalez-Escribano. 'Study

and Evaluation of Transactional Memory approaches with a Software Thread-Level

Speculation Framework'. En: IEEE Transactions on Parallel and Distributed Systems. To

be submitted

- 10. Alvaro Estebanez, Diego R. Llanos y Arturo Gonzalez-Escribano. 'Evaluating the capabilities of the Xeon Phi platform in the context of software-only, thread-level speculation'. En: *Proceedings of the 8th International Symposium on High-level Parallel Programming and Applications*. HLPP '15. Pisa, Italy: ACM, 2015. To be also published in *International Journal of Parallel Programming*, Springer US.

## R.5 Respuesta a la pregunta de investigación y conclusiones

¿Es posible desarrollar un sistema de paralelización especulativa en tiempo de ejecución capaz de utilizar eficientemente estructuras de datos complejas, utilizar aritmética de punteros, y tener en cuenta la tendencia de violaciones de dependencia producida hasta ahora para estimar el mejor tamaño de bloque a repartir? ¿Podría implementarse, dando lugar a buenos resultados experimentales, utilizando memoria transaccional, y en una arquitectura con un gran número de núcleos como los coprocesadores Intel Xeon Phi?

Como resultado de nuestra investigación, podemos afirmar que la pregunta de investigación ha sido contestada claramente. Por un lado, hemos desarrollado un software de paralelización especulativa capaz de (a) controlar estructuras de datos complejas, y (b) utilizar aritmética de punteros. Además, hemos propuesto (c) una estrategia de reparto de iteraciones que tiene en cuenta no solo parámetros de tiempo de ejecución como las violaciones de dependencia, si no también el optimismo que el usuario quiera implementar en cuanto a la asignación de bloques de iteración más grandes o más pequeños.

También hemos verificado que (d) la paralelización especulativa y la memoria transaccional se pueden combinar con resultados similares a los de las técnicas clásicas, y (e) que la paralelización especulativa puede utilizarse en los coprocesadores Intel Xeon Phi.

## R.6 Agradecimientos

Esta Tesis está parcialmente financiado por el Ministerio de Industria (CENIT OCEAN-LIDER), Ministerio de Ciencia e Innovación y el Fondo Europeo de Desarrollo Regional (MOGECOPP project TIN2011-25639, CAPAP-H3 network TIN2010-12011-E, CAPAP-H4 network TIN2011-15734-E, CAPAP-H5 network TIN2014-53522-REDT).

#### **CHAPTER 1**

# Introduction

S ince the invention of integrated circuit, computer performance has been improving exponentially. However, this progression quickly reached different physical limits at the beginning of the 21st century, being power dissipation the most remarkable one. Instead of augmenting clock speed even more, computer architects decided to pack several computational units in the same chip, starting the era of the affordable, shared-memory multiprocessor. However, to take advantage of these architectures in the execution of a single application, sequential code should be either rewritten as a set of parallel tasks, or automatically transformed into parallel code. In this chapter we will explain why the latter is a non-trivial problem, how speculative parallelization techniques may help, and which are the goals of this Ph.D. Thesis.

#### 1.1 Motivation

Since the advent in 1971 of the first microchip, the Intel 4004, with about 2300 transistors and a frequency of 104 KHz [16, 122], computing machines suffered a dramatic evolution, with exponential increments on the number of transistors per surface unit and a corresponding increment in computational performance. This astounding improvement rate quickly reaches physical limits at the beginning of the 21st century, such as the difficulties associated to extract all the heat produced by a chip of just a few square millimeters that consumes more than 100W.

To keep growing the rate of performance, computer architects started to pack several, simpler computational units in the same chip. This solution took advantage of the increment in the number of transistors that can be packed together<sup>1</sup>, while distributing "hot spots" on different areas of the chip, thus simplifying cooling. This solution also allowed to decrease the peak frequency used, consequently making this solution affordable for its use on battery-powered systems.

Nonetheless, for the very first time in computing history, an architectural improvement does not automatically lead to better performance of sequential applications. To take advantage of these new capabilities, these shared-memory parallel systems should either be used to run several applications at once, or run a parallel version of a sequential application. This Ph.D. Thesis is focused on the last problem, studying how a single task can be automatically executed by different processors in parallel.

# 1.1.1 Multiprocessor computers

As stated before, multicore machines are capable of executing not only several programs simultaneously, but also the same program divided on smaller tasks. To achieve improvements in the execution of a sequential program with a multicore computer, it is necessary that programs can be decomposed on independent tasks. If tasks have *dependences* among them, and we execute them in the wrong order, the execution will likely lead to incorrect results.

To isolate the parts of a code that may be executed independently is a tedious, error prone task because factors such as synchronization have to be taken into account to avoid undesirable results. There already exist some specific languages, as well as extensions to sequential languages, and function libraries centered on ease users this parallelization process. However, in order to successfully parallelize a sequential program, the programmer should (a) know the characteristics of the underlying hardware, (b) understand the problem to be solved by the code, and (c) know the parallel programming model being used. In addition, parallel software that is tailored for a specific architecture may not be portable to other systems. These facts make automatic parallelization a very appealing idea.

<sup>&</sup>lt;sup>1</sup>This is another example of an improvement that might soon reach its own physical limit.

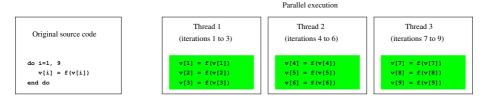

Figure 1.1: Loop without dependences between iterations.

Figure 1.2: Loop with a dependence between two iterations.

Nowadays, there are some compilers capable of parallelizing fragments of a code (mainly loops). However, parallelizing compilers conservatively refuses to parallelize a loop if there is the slightest possibility of a dependence violation among its iterations. Determining or predicting which instructions depend on others is a rather difficult task, because of the combinatorial explosion due to the existence of multiple control paths. Moreover, values of certain variables may not be known at compile time, thus preventing parallelization. We will further explore this point with an example.

Figure 1.1 shows a loop without dependence violations: All the instructions are independent, so the code may be safely parallelized at compile time. On the other hand, Figure 1.2 depicts a loop that may produce some dependence violations. Supposing that the value of k is unknown at compile time, and assuming that it will be k=5 at runtime, if the parallel execution of the loop executes iteration i (with i=5 in our example) before iteration i-2 (i-2=3 in our example), the value of v[i-2] (that is, v[3]) will return an outdated value, breaking sequential semantics. This issue, called *dependence violation*, appears when a given thread produces a datum that has already been consumed by one of its successors, with respect to the original, sequential order. So as to guarantee a right behavior, it is necessary to serialize the execution of iterations i-2 and i, a difficult task in the general case<sup>2</sup>. This one is the most severe limitation to compile-time parallelization techniques.

$<sup>^2</sup>$ Note that if the dependence did not cross thread boundaries (for example, with k=6), the compiler could have parallelized the loop safely.

```

for (i=0; i<100; i++)

{

localVar = sharedVarA+sharedVarB;

sharedVarA = i*localVar;

}</pre>

```

**Listing 1.1:** Example of a code with private and shared variables.

There exist some parallel constructs to handle these situations, such as barriers, but their use severely affects performance, sometimes making the resulting parallel code even slower than the original, sequential one.

### 1.1.2 Dependence violations

In order to understand when a dependence violation may take place, we will first show how variables can be classified according to their use. When using a shared-memory programming model, variables can be classified as either *shared* or *private*.

Informally speaking, private variables are those whose values are always written before being read at a given iteration. Their intended scope is the iteration, and not beyond it. On the other hand, shared variables contain values whose scope spans several iterations. Therefore, if a thread consumes a shared value, and later a thread running an *earlier* iteration writes a new value onto it, a dependence violation will take place.

An example of private and shared variables is shown at Listing 1.1. In this example, localVar is private since it is always written locally before being read in the context of each iteration. On the other hand, sharedVarA and sharedVarB are shared variables. In the case of sharedVarB, it is a read-only variable, so it will not trigger any dependence violation. Regarding shareVarA, it is read before being written, so reads and writes that do not follow sequential semantics are likely to trigger a dependence violation.

A loop that only uses private and read-only shared variables is parallelizable. On the contrary, loops that performs reads and writes on shared variables are expected to suffer dependence violations when executed in parallel.

#### Types of data dependences

There are three types of data dependences among iterations:

• Write-after-write (WAW): This kind of data dependence is produced when a variable is written in two different iterations, with no reads between the writes. An incorrect ordering in the execution of both iterations leads to a dependence violation.

```

for (i=0;i<4;i++)

{

if (i==1)

localVar = 4;

if (i==3)

localVar = 7;

}</pre>

```

Listing 1.2: Example of Write-after-write (WAW) dependence violation.

Listing 1.3: Example of Write-after-read (WAR) dependence violation.

Listing 1.2 shows an example. In this code, the localVar variable is written twice, first at iteration 2, and again at iteration 4. In a sequential code, the value obtained at the end of the loop in localVar would be 7. However, if we suppose a parallel execution with two processors, we cannot guarantee that iteration 2 is executed before iteration 4, and therefore, it cannot be ensured that the value of localVar at the end of the loop is 7 (the value might be erroneously 4).

• Write-after-read (WAR): This type of data dependence appears when a local variable that has been previously read in a previous iteration is written with a new value in a subsequent iteration. Again, an incorrect ordering of both iterations may trigger a dependence violation.

Listing 1.3 shows an example of this data dependence. Variable localVarA is read at iteration 2, and later written at iteration 4. In a sequential execution, the value of localVarA at the end of the loop would be 5, and the value of localVarB would be 3. Now suppose a parallel execution with two processors, where iterations 1 and 2 are assigned to the first one, and iterations 3 and 4 are assigned to the other processor. In this case, it cannot be ensured that iteration 2 is executed before iteration 4, so the value of localVarB at the end of the loop may not be 3.

**Listing 1.4:** Example of Read-after-write (RAW) dependence violation.

Read-after-write (RAW): This data dependence is the most difficult to track.

RAW dependence violations occur when a shared variable is written with a value that will be read by subsequent iterations. If both operations are carried out in the wrong order, the value read may be wrong.

Listing 1.4 shows an example. A sequential execution of that code will produce the values localVar = 10 and sv = 20. If we run this code in parallel using three processors, each one executing a single iteration, a parallel execution is likely to lead to wrong values. The exact values being produced depend on the particular ordering of the instructions being executed. For example, let us assume that at instant t1 the first instruction of threads 1 and 2 are executed, so localVar versions of both threads are 0. After that, at instant t2, the following instruction of thread 1 is executed, setting sv = 20. Once completed, at instant t3 the first instruction of thread 3 is executed, triggering a dependence violation, since localVar = 20 is consumed, instead of the value 10 that would follow sequential semantics. But problems do not stop here. If we suppose that at instant t4 the next instruction of thread 3 is executed, the value of sv will be 20. And consequently, if at instant t5 the last instruction of thread 2 is executed, sv will be 10. At the end of the execution, the values of variables would be either localVar = 20 or localVar = 0, and sv = 10, and the parallel executions would have failed. All those operations are summarized in the Table 1.1.

# 1.1.3 Parallelization of codes with dependences

Although the problem of parallelizing loops with dependences may seem hard to tackle, there are some techniques which allow the parallelization of such complex codes. Whereas classical solutions simply refuse to parallelize code whenever a single dependence might take

|         | Thread 1 |    | Thread 2 |    | Thread 3 |    |

|---------|----------|----|----------|----|----------|----|

| Instant | localVar | sv | localVar | sv | localVar | sv |

| t1      | 0        | 0  | 0        | 0  | 1        | 0  |

| t2      | 0        | 20 | 0        | 20 | 1        | 20 |

| t3      | 0        | 20 | 0        | 20 | 20       | 20 |

| t4      | 0        | 20 | 0        | 20 | 20       | 20 |

| t5      | 0        | 10 | 0        | 10 | 20       | 10 |

**Table 1.1:** Timing of the loop with the values of each variable at any time in the supposed execution.

place, other proposals, such as *Inspector-Executor* or *Thread-Level Speculation* handles these situations. These techniques optimistically suppose that the whole execution will follow sequential order. If any dependence violation occurs, they will detect this situation and perform the required operations so as to achieve a correct result. A brief description of both techniques follows.

#### **Inspector-Executor**

This technique [165] aims to parallelize loops that cannot be parallelized by a compiler. It is mainly based on finding data dependences among the iterations of a loop through the use of an inspector loop extracted from the original loop. The inspector loop tries to assign every single iteration that depends on previous ones to the same processor, so that the execution is ensured to be done in the correct order. A second, executor loop, carries out the execution of each chunk of iterations in parallel. Although this technique can be applied to any loop, its use is only advisable if the processing time of the inspector loop is quite lesser than the execution time of the original loop. Unfortunately, this does not happen in the general case, due to the cost of inspecting loops that use pointer arithmetic, complex control flows or depend on input data. This proposal was later enhanced with different improvements, that will be discussed on Section 2.3.

# 1.1.4 Speculative Parallelization

Thread-Level Speculation (TLS) [49, 215, 218, 241], also called Speculative Parallelization (SP)<sup>3</sup> [73, 96, 144, 273] or Optimistic Parallelism [157, 158, 159, 160, 161, 162] tries to extract parallelism of loops that cannot be ensured to be fully parallel at compile time. In other words, this technique aims to parallelize codes with dependences. TLS optimistically assumes that dependence violations will not occur, launching the parallel execution of the

<sup>&</sup>lt;sup>3</sup>From now on, TLS and SP concepts will be used throughout the text interchangeably.

loop. Meanwhile, a hardware or software monitor ensures the correctness of that assumption, taking corrective actions when needed.