## Journal Pre-proofs

Analysis of the performance of Nb<sub>2</sub>O<sub>5</sub>-doped SiO<sub>2</sub>-based MIM devices for memory and neural computation applications

Ó.G. Ossorio, G. Vinuesa, H. García, B. Sahelices, S. Dueñas, H. Castán, M. Ritala, M. Leskelä, M. Kemell, K. Kukli

PII: S0038-1101(21)00157-X

DOI: https://doi.org/10.1016/j.sse.2021.108114

Reference: SSE 108114

To appear in: Solid-State Electronics

Received Date: 15 April 2021 Accepted Date: 31 May 2021

Please cite this article as: Ossorio, Oacute.G., Vinuesa, G., García, H., Sahelices, B., Dueñas, S., Castán, H., Ritala, M., Leskelä, M., Kemell, M., Kukli, K., Analysis of the performance of Nb<sub>2</sub>O<sub>5</sub>-doped SiO<sub>2</sub>-based MIM devices for memory and neural computation applications, *Solid-State Electronics* (2021), doi: https://doi.org/10.1016/j.sse.2021.108114

This is a PDF file of an article that has undergone enhancements after acceptance, such as the addition of a cover page and metadata, and formatting for readability, but it is not yet the definitive version of record. This version will undergo additional copyediting, typesetting and review before it is published in its final form, but we are providing this version to give early visibility of the article. Please note that, during the production process, errors may be discovered which could affect the content, and all legal disclaimers that apply to the journal pertain.

© 2021 The Author(s). Published by Elsevier Ltd.

# Analysis of the performance of Nb<sub>2</sub>O<sub>5</sub>-doped SiO<sub>2</sub>-based MIM devices for memory and neural computation applications

Ó. G. Ossorio<sup>a</sup>, G. Vinuesa<sup>a</sup>, H. García<sup>a</sup>, B. Sahelices<sup>a</sup>, S. Dueñas<sup>a</sup>, H. Castán<sup>a,\*</sup>, M. Ritala<sup>b</sup>, M. Leskelä<sup>b</sup>, M. Kemell<sup>b</sup>, K. Kukli<sup>c</sup>

<sup>a</sup>Department of Electronics, University of Valladolid, Paseo de Belén 15, Valladolid, E-47011, Spain <sup>b</sup>Department of Chemistry, University of Helsinki, P.O.Box 55, Helsinki, FI-00014, Finland <sup>c</sup>Institute of Physics, University of Tartu, W. Ostwald 1, Tartu, 50411, Estonia

#### **Abstract**

Since two decades ago, research on resistive memories has continuously grown, gathering relevance through the variety of different technologies that fit into the non-volatile memories' area. In this study, we discuss the performance and electrical characteristics of RRAM cells constituted by MIM stacks with dielectric formed by  $Nb_2O_5$ -doped  $SiO_2$ . We report experimental results that show a clear improvement in the resistive behavior of the devices and an excellent analogical control of the intermediate levels between high-resistance and low-resistance states.

Keywords: RRAM, NVM, MIM stack, niobium oxide, silicon oxide

#### 1. Introduction

Resistive random access memories (RRAM) are of increasing interest, and they show fast write and erase operations, small cell size, good cyclic endurance and low working voltage. Due to the multi-valence nature of transition metals, their oxides work well as resistive switching layers, and are hence widely used in this application. SiO2 layers were used as resistive switching media in 3D crossbar arrays patterned on conductive wafers covered by chemically oxidized Si [1]. RRAM characteristics simulating synaptic behavior were also aimed and described in SiO2 media formed on thermally oxidized Si [2], or sputtered on platinum [3]. RRAM behavior has been analyzed also in another work on SiO2 films reactively sputtered on platinum [4]. Notably, SiO<sub>2</sub> contact barrier layers have been applied in sputtered stacks between Pt electrodes and nonstoichiometric Ta<sub>2</sub>O<sub>5-x</sub>/TaO<sub>2-x</sub> charge carrier source layers [5], where the SiO<sub>2</sub> layer assisted in confining the conduction channels and formation of filaments in the resistive switching regime.

While Ta<sub>2</sub>O<sub>5</sub> has quite widely been used as RRAM medium, Nb<sub>2</sub>O<sub>5</sub>, which is an oxide closely related to Ta<sub>2</sub>O<sub>5</sub> in terms of the chemical and physical properties, has been scarcely explored in the development of memristive devices. Nonetheless, Nb<sub>2</sub>O<sub>5</sub>/ NbO<sub>2</sub>-based thin stacked layers have earlier been engineered for 3D RRAM applications [6]. In another and more recent paper, chemical nature of NbO<sub>x</sub> films sputtered on Pt electrodes, affecting switching characteristics, was studied again [7]. Moreover, devices based on niobium oxides were proposed as prospective for neural computation, emulating the computational capability of a nerve system [8].

\*Corresponding author

Email address: helena@ele.uva.es (H. Castán)

Remarkably, Nb<sub>2</sub>O<sub>5</sub> films as resistive switching media have been grown by atomic layer deposition (ALD), as well, using either Nb(OCH<sub>2</sub>CH<sub>3</sub>)<sub>5</sub> and H<sub>2</sub>O [9] or C<sub>13</sub>H<sub>33</sub>N<sub>4</sub>Nb and O<sub>2</sub> plasma [10] processes on Pt electrode substrates. In the latter study, TiO<sub>2</sub> film was deposited between Nb<sub>2</sub>O<sub>5</sub> layers to assist in the creation of low-power forming-free RRAM device, indicating the adequation of multilayer structure.

In a previous study [11], Nb<sub>2</sub>O<sub>5</sub>-SiO<sub>2</sub> multilayers and mixed films were deposited on TiN electrode substrates by ALD using niobium pentaethoxide, hexakis(ethylamino)disilane, and ozone as precursors, and their ability to perform as resistive switching media in as-deposited state was examined. The conduction currents in single, non-mixed, SiO<sub>2</sub> and Nb<sub>2</sub>O<sub>5</sub> films tended to remain too high to enable reliable switching between high and low resistance states. In the Nb<sub>2</sub>O<sub>5</sub>-SiO<sub>2</sub> nanolaminates, however, after tuning the relative content of Nb in SiO<sub>2</sub> based films, better defined current-voltage switching loops could be recorded in the films deposited using Nb<sub>2</sub>O<sub>5</sub>:SiO<sub>2</sub> cycle ratio of 1:5, providing Nb:Si cation ratio of 0.13.

In the present study,  $Nb_2O_5$ -SiO<sub>2</sub> mixed films with Si content approximately tenfold higher than that of Nb were examined in conventional resistive switching and small-signal regimes, in order to map the conductivity and capacitance memory states against amplitudes of programming voltage. Incremental and accumulative measurements were performed in order to study the effects of intermediate charging between consecutive Set and Reset events, i.e., writing and erasing bits, respectively.

#### 2. Experimental details

The dielectric films composed of  $SiO_2$  and  $Nb_2O_5$  were grown by ALD from  $Si_2(NHEt)_6$ ,  $Nb(OC_2H_5)_5$ , and  $O_3$  at 300 °C in a flow-type hot-wall ALD reactor F120 (ASM Microchemistry, Ltd) to thicknesses around 20 nm. The cycle times

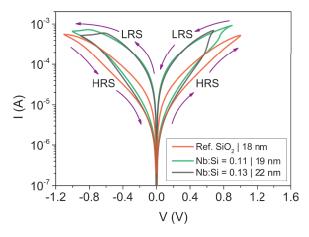

Fig. 1: Mean values of 20 current-voltage cycles for 3 dielectric films with different Nb:Si ratios and grown to the thicknesses indicated by labels.

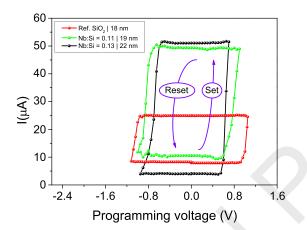

Fig. 2: Current-voltage memory maps for Nb<sub>2</sub>O<sub>5</sub>-SiO<sub>2</sub> films with different Nb:Si atomic ratios and grown to the thicknesses indicated by labels.

used for both SiO<sub>2</sub> and Nb<sub>2</sub>O<sub>5</sub> constituent layers were 0.5-0.5-2.0-0.5 s, denoting the sequence Si or Nb precursor pulse purge - O<sub>3</sub> pulse - purge. Electrically conducting substrates were composed of (100) oriented silicon with a resistivity of 0.014 -  $0.020~\Omega$  · cm, i.e. boron-doped Si to the concentrations ranging from  $5 \times 10^{18}$  to  $1 \times 10^{19}$  cm<sup>-3</sup>, coated with 10 nm thick crystalline titanium nitride layer. Energy dispersive x-ray spectrometry (EDX) was used for the measurements of the film thicknesses as well as relative niobium and silicon contents in the films by a Hitachi S-4800 scanning electron microscope equipped with an Oxford INCA 350 EDX spectrometer. The atomic ratios of niobium to silicon ranged from 0 to 0.13. The films were amorphous in the as-deposited state [11]. The structure of the stacks subjected to the measurements was Al/Ti/SiO<sub>2</sub>:Nb<sub>2</sub>O<sub>5</sub>/TiN/Si, where the top electrodes were made by electron beam evaporation through a shadow mask. The devices under test had three different areas: 0.204 mm<sup>2</sup>, 0.052 mm<sup>2</sup> and 0.002 mm<sup>2</sup>. Keithley 4200-SCS meter was used for the electrical characterization of the device stacks. Small signal measurements were carried out by applying a 30 mV signal at 100 kHz over the DC voltage.

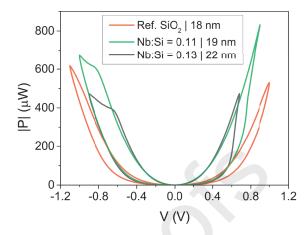

Fig. 3: Power consumed in the resistive switching media based on  $Nb_2O_5$ - $SiO_2$  films with different atomic ratios and grown to the thicknesses indicated by labels. The power was calculated based on the voltage applied and current recorded in Fig. 1

### 3. Results and discussion

The influence of adding Nb<sub>2</sub>O<sub>5</sub> to SiO<sub>2</sub> in terms of power consumption, width of the resistance window and precise control of the intermediate states was assessed. We performed a full comparison among three samples: the reference unmixed SiO<sub>2</sub> film (18 nm) and films with Nb:Si ratios of 0.11 (19 nm) and 0.13 (22 nm). In Fig. 1 current-voltage (I-V) cycles showing the switching between the high and low resistance states (HRS and LRS, respectively) are depicted. In these oxide films, the resistive switching behavior is due to the segregation of oxygen vacancies that may form a nano-filament which works as a conducting leakage path. As it is known, TiN is used as a standard electrode because it plays the role of oxygen ion reservoir, aiding the formation of oxygen vacancies which build the conductive filament in the insulator between both electrodes [12, 13]. It is shown that the narrowest functional window between the HRS and LRS was observed in the reference SiO2 device. At the same time, both Nb2O5-mixed devices behave quite similarly. Further, hysteretic memory maps depicted in Fig. 2 were obtained by using voltage pulses to program the device, where each programming pulse is followed by a read pulse at a fixed voltage [14]. The sequence and range of pulses completely cover the Set and Reset transitions. The read voltage was kept at 0.1 V, in order to not affect the resistive state. One can see in Fig. 2 that in both mixed films, similar characteristic values were achieved while the reference SiO2 differed from the mixtures by a narrower window between high and low resistance levels. It is important to remark that these memory maps were not calculated by taking the average of a group of cycles, but from individual measurements. For Ta<sub>2</sub>O<sub>5</sub>-based devices it has been reported that the activation energy for oxygen-ion migration is much lower in Ta-rich SiO<sub>2</sub>-hosted structures in comparison with non-mixed Ta<sub>2</sub>O<sub>5</sub> films [5]. As chemical and physical properties of Nb<sub>2</sub>O<sub>5</sub> are similar to Ta<sub>2</sub>O<sub>5</sub>, we can understand that the Set current increases with the Nb content. In addition, the useable programming voltage range is wider for SiO<sub>2</sub> than

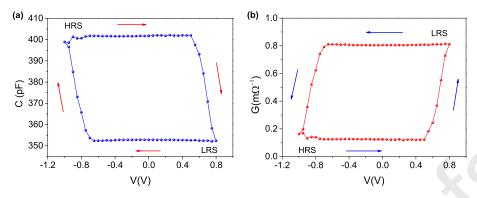

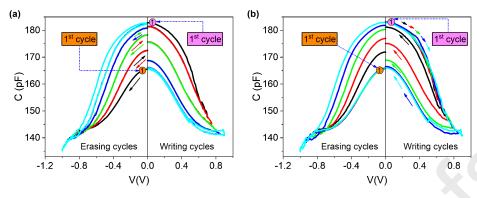

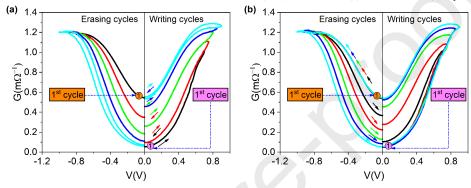

Fig. 4: Small signal memory maps corresponding to device with Nb:Si proportion of 0.13. C-V map (a). G-V map (b)

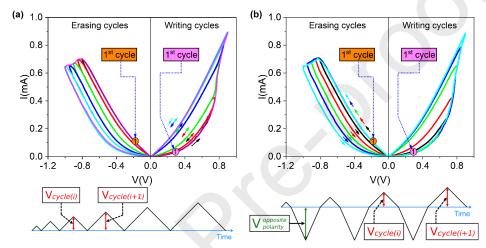

Fig. 5: Control of the intermediate states on device with Nb:Si = 0.11 (I-V). Accumulative (a) and Incremental (b) experiments

for the Nb<sub>2</sub>O<sub>5</sub>-SiO<sub>2</sub>. This is in a good agreement with previous studies [15, 16] where TiN and SiO<sub>2</sub> were employed as electrodes and resistive switching layers, and usually displayed high operating Set and Reset voltages, resulting in high power consumption in comparison, for example, with HfO<sub>x</sub>. In Fig. 3, one can read the power consumption for each device. The film with the Nb:Si ratio of 0.13 provided the lowest power consumption values. These results imply that the Nb:Si ratio of 0.13 in the dielectric is relatively well suited to its implementation in memory systems. Fig. 4 represents the small-signal memory maps of the mentioned sample (capacitance vs. voltage and conductance vs. voltage), which portray its excellent characteristics.

By revisiting Fig. 2, it can be seen that the Set transition is more gradual in the 19 nm thick sample (Nb:Si = 0.11) when compared with the other two. This detail may be useful for developing artificial synapses in neuromorphic circuits. We make this assumption even though these are large area structures. In order to adapt these structures to 1T-1R bipolar RRAM devices, the dimensions of the filamentary channels as well as the fractional conducting areas should be taken into account [17], because both are essential parameters for determining the current level for LRS and HRS and also when estimating the ultimate

packing density of the ReRAM device. As a procedure to justify the mentioned assumption, we performed some complementary measurements. The DC curves in Fig. 5 correspond to both writing and erasing cycles, which were measured in two distinct ways. Accumulative (Fig. 5a) current-voltage measurements were performed by applying the first and only cycle under the voltage polarity opposite to that in the following consecutive measurements (in order to assure that the device starts from a full HRS/LRS), continuing with voltage sweeps to maxima what were increased in each subsequent cycle. As a result, every cycle was started at the current (resistivity) level predetermined by the previous one. In Fig. 5b the incremental writing and erasing test measurement is depicted. In this case, voltage sweeps were applied to the opposite polarity after each cycle, which ensured that every cycle started at the same HRS/LRS level and reached its respective maximum current. It is important to note here the progressive Set and Reset phases in which it was not necessary to impose any current limitation (compliance). To complete the description of the measurements, Figs. 6 and 7 illustrate the small-signal writing and erasing tests, with capacitance vs. voltage curves in the former case, and conductance vs. voltage loops in the latter case. Similarly to the performance observed in the case of conventional I-V measurements,

Fig. 6: Control of the intermediate states on device with Nb:Si = 0.11 (C-V). Accumulative (a) and Incremental (b) experiments

Fig. 7: Control of the intermediate states on device with Nb:Si = 0.11 (G-V). Accumulative (a) and Incremental (b) experiments

the intermediate current (resistivity) states could become appreciably well controlled in the Nb<sub>2</sub>O<sub>5</sub>-SiO<sub>2</sub> film with the Nb:Si atomic ratio of 0.11.

#### 4. Conclusions

The results revealed that the Nb<sub>2</sub>O<sub>5</sub>-SiO<sub>2</sub> films can offer advanced resistive switching characteristics compared to SiO<sub>2</sub>. A film with the Nb:Si ratio of 0.13 brought appreciable results regarding power consumption and resistance window. In addition, precise control on intermediate states with another device configuration (Nb:Si ratio of 0.11) became possible by applying sequential voltage pulses at intermittent resistance values reached during the switching cycles.

#### Acknowdledgements

This work was funded by the Spanish Ministry of Science, Innovation and Universities grant TEC2017-84321-C4-2-R, with support of Feder funds, Finnish Centre of Excellence in Atomic Layer Deposition (284623), and Estonian Research Agency (PRG753).

#### References

C. Li, Q. Xia, Springer International Publishing, Cham, 2019, pp. 791– 813.

- [2] X. Yan, Z. Zhou, B. Ding, J. Zhao, Y. Zhang, J. Mater. Chem. C 5 (2017) 2259–2267.

- [3] X. Lian, X. Shen, J. Fu, Z. Gao, X. Wan, X. Liu, E. Hu, J. Xu, Y. Tong, Electronics 9 (2020).

- [4] H. Jiang, X. Y. Li, R. Chen, X. L. Shao, J. H. Yoon, X. Hu, C. S. Hwang, J. Zhao, Sci. Rep. 6 (2016) 1–11.

- [5] G.-S. Park, Y. B. Kim, S. Y. Park, X. S. Li, S. Heo, M.-J. Lee, M. Chang, J. H. Kwon, M. Kim, U.-I. Chung, et al., Nature Comm. 4 (2013) 1–9.

- [6] S. Kim, X. Liu, J. Park, S. Jung, W. Lee, J. Woo, J. Shin, G. Choi, C. Cho, S. Park, D. Lee, E. Cha, B. Lee, H. D. Lee, S. G. Kim, S. Chung, H. Hwang, in: 2012 Symposium on VLSI Technology (VLSIT), 2012, pp. 155–156.

- [7] J. Aziz, H. Kim, S. Rehman, M. F. Khan, D.-k. Kim, Nanomater. 10 (2020).

- [8] M. D. Pickett, G. Medeiros-Ribeiro, R. S. Williams, Nat. Mater. 12 (2013) 114–117.

- [9] L. Chen, Y.-W. Dai, Q.-Q. Sun, J.-J. Gu, Y. Xu, S.-J. Ding, D. W. Zhang, Curr. Appl. Phys. 11 (2011) 849–852.

- [10] K. M. Kim, J. Zhang, C. Graves, J. J. Yang, B. J. Choi, C. S. Hwang, Z. Li, R. S. Williams, Nano Lett. 16 (2016) 6724–6732. PMID: 27661260.

- [11] K. Kukli, M. Kemell, M. J. Heikkilä, H. Castán, S. Dueñas, K. Mizohata, M. Ritala, M. Leskelä, Nanotechnology 31 (2020) 195713.

- [12] Z. Zhang, B. Gao, Z. Fang, X. Wang, Y. Tang, J. Sohn, H.-S. P. Wong, S. S. Wong, G.-Q. Lo, IEEE Electron Dev. Lett. 36 (2014) 29–31.

- [13] T.-C. Chang, K.-C. Chang, T.-M. Tsai, T.-J. Chu, S. M. Sze, Mater. Today 19 (2016) 254–264.

- [14] H. Castán, S. Dueñas, H. García, Ó. G. Ossorio, L. A. Domínguez, B. Sahelices, E. Miranda, M. B. González, F. Campabadal, J. Appl. Phys. 124 (2018) 152101.

- [15] D. Lee, E. Cho, J. Lee, K. Jung, M. Jeong, S. Yamada, H. Hong, K. Lee, S. Heo, D. Ko, et al., Appl. Phys. Lett. 108 (2016) 212102.

- [16] M. Yu, Y. Fang, Z. Wang, Y. Pan, M. Li, Y. Cai, R. Huang, J. Appl. Phys. 119 (2016) 195302.

- [17] B. Singh, B. Mehta, D. Varandani, A. V. Savu, J. Brugger, Nanotechnology 23 (2012) 495707.