# UNIVERSIDAD DE VALLADOLID ESCUELA DE INGENIERIAS INDUSTRIALES

Grado en Ingeniería Electrónica Industrial y Automática

# Verilog-A Based Implementation of a MOSFET Model for Analog Integrated Circuit Design

#### **Autor:**

Gallego Velázquez, Alba

Responsable de Intercambio en la Uva: Moriñigo Sotelo, Daniel

> Universidad de destino: Universidad Técnica de Creta

# Valladolid, Julio y 2025.

#### TFG REALIZADO EN PROGRAMA DE INTERCAMBIO

TÍTULO: Verilog-A Based Implementation of a MOSFET Model for Analog

**Integrated Circuit Design**

ALUMNO: Alba Gallego Velázquez

FECHA: 9 de Julio de 2025

CENTRO: Departamento de Ingeniería Eléctrica y de Computadores

UNIVERSIDAD: Universidad Técnica de Creta

TUTOR: Matthias Bucher

#### Resumen:

La tesis expone en el desarrollo e implementación de un modelo compacto de un MOSFET, basado en el modelo teórico EKV, e implementado utilizando el lenguaje Verilog-A. La utilización de entornos de simulación y de compilación, como el servidor abierto OpenVAF y Ngspice, es fundamental para facilitar la ejecución efectiva del trabajo. La construcción de un modelo que pueda realizar la función de un nMOS o un pMOS nanométrico operando en un estado saturado se ve facilitada por éstos. En este modelo se incorporan dependencias físicas y se asegura la obtención de expresiones continuas para todas las regiones de inversión. El comportamiento del modelo se valida frente a datos experimentales mediante de simulación. El resultado de es un modelo preciso y versátil, apto para soportar diseños de circuitos analógicos integrados con un amplio rango de valores para el coeficiente de inversión.

#### **Abstract:**

The present thesis sets out the development and implementation of a compact model of a MOSFET, based on the theoretical EKV model, and implemented using the Verilog-A language. The utilization of simulation and compilation environments, such as the open server OpenVAF and Ngspice, is instrumental in facilitating the effective execution of the work. The construction of a model that can perform the function of an nMOS or a pMOS nanometric operating in a saturated state is facilitated by these. In this model, physical dependencies and second-order effects are incorporated, ensuring the attainment of continuous expressions for all inversion regions. The model's behaviour is validated against experimental data by means of simulation. This results in an accurate, compact and versatile model, which is suitable for supporting integrated analog circuits designs with a wide range of values for the inversion coefficient.

#### Palabras Clave:

MOSFET, Verilog-A, Open-source, Modelo EKV, Región Saturación

### **Keywords:**

MOSFET, Verilog-A, Open-source, EKV model, Saturation Region

# Verilog-A Based Implementation of a MOSFET Model for Analog Integrated Circuit Design

### Thesis by Alba Gallego Velázquez

In Partial Fulfillment of the Requirements for the Degree of Electronic Industrial and Automatic Engineering

TECHNICAL UNIVERSITY OF CRETE Chania, Crete

2025

Defended: July 1, 2025

#### **ACKNOWLEDGEMENTS**

I would like to express my sincere gratitude to Professor Matthias Bucher for his invaluable assistance, unwavering support, and constant guidance throughout the process of composing my thesis. I would also like to express my gratitude to Professor Daniel Moriñigo Sotelo for his great assistance, without which I would not have been able to undertake this academic experience that has led me to write my thesis in Greece. I would also like to acknowledge Doctor Konstantinos Gyftakis for his insightful comments and suggestions, and for his contribution to the evaluation process of my work. To my friends and family, who have provided unwavering support throughout my academic journey, both during periods of success and challenge. The encouragement and understanding demonstrated by the mentor was instrumental in fostering resilience and persisting in the face of adversity. It is because of you that I am here. I would like to express my sincere gratitude to all those who have played a pivotal role in this vital stage of my academic journey.

#### **ABSTRACT**

Recent advances in the field of analogue electronics have led to an increased demand for the creation of programmable models of analogue circuits. The present thesis sets out the development and implementation of a compact model of a MOSFET, based on the theoretical EKV model, and implemented using the Verilog-A language. The utilization of simulation and compilation environments, such as the open server OpenVAF and Ngspice, is instrumental in facilitating the effective execution of the work. The construction of a model that can perform the function of an nMOS or a pMOS nanometric operating in a saturated state is facilitated by these. In this model, physical dependencies such as temperature, channel length, and second-order effects are incorporated, ensuring the attainment of continuous expressions for all inversion regions. The model's behaviour is validated against experimental data by means of simulation, thus enabling the evaluation of parameters such as drain current, inversion coefficient, capacitances, transconductances, and response to thermal and flicker noise. This results in an accurate, compact and versatile model, which is suitable for supporting integrated analog circuits designs with a wide range of values for the inversion coefficient.

### TABLE OF CONTENTS

| Acknow    | ieageme    | nts                                                              |

|-----------|------------|------------------------------------------------------------------|

| Abstract  |            |                                                                  |

| Table of  | Content    | s                                                                |

| List of I | llustratio | ns                                                               |

| List of T | ables .    |                                                                  |

| Acronyn   | ns         |                                                                  |

| Chapter   | I: Introd  | uction                                                           |

| 1.1       | Backgro    | ound 11                                                          |

| 1.2       | Objectiv   | ves of Work                                                      |

| 1.3       | Outline    |                                                                  |

| 1.4       | Related    | Work                                                             |

|           | 1.4.1      | Nanoscale MOSFET Modeling: The simplified EKV model for the      |

|           |            | design of low-power analog circuits                              |

|           | 1.4.2      | Nanoscale MOSFET Modeling: Using the inversion coefficient as    |

|           |            | the primary design parameter                                     |

|           | 1.4.3      | Optimizing Drain Current, Inversion Level, and Channel Length in |

|           |            | Analog CMOS Design                                               |

|           | 1.4.4      | Tradeoffs and Optimization in Analog CMOS Design                 |

|           | 1.4.5      | The EPFL-EKV MOSFET Model Equations for Simulation 14            |

|           | 1.4.6      | EKV3. MOSFET Compact Model. Model's Documentation 15             |

| Chapter   | II: Theo   | retical Background                                               |

| 2.1       | Constru    | ction of a MOSFET                                                |

| 2.2       | Operation  | on of a MOSFET                                                   |

|           | 2.2.1      | Sub-threshold Region                                             |

|           |            | 2.2.1.1 Accumulation Zone                                        |

|           |            | 2.2.1.2 Depletion Zone                                           |

|           |            | 2.2.1.3 Inversion Zone                                           |

|           | 2.2.2      | Linear Region                                                    |

|           | 2.2.3      | Saturation Region                                                |

|           |            | 2.2.3.1 Drain-Induced Barrier Lowering                           |

|           |            | 2.2.3.2 Saturation Velocity                                      |

|           |            | 2.2.3.3 Hot Electrons Degradation                                |

|           | 2.2.4      | Breakdown Region                                                 |

| 2.3       | Second     | Order Effects of a MOSFET                                        |

|           | 2.3.1      | Subthreshold Current Effect                                      |

|           | 2.3.2      | Variation of Carrier Mobility                                    |

|           | 2.3.3      | Body Effect                                                      |

|           | 2.3.4      | Impact Ionization                                                |

|           | 2.3.5      | Modulation of the Channel Length                                 |

| 2.4 EKV Model                                               | 43       |

|-------------------------------------------------------------|----------|

| Chapter III: Setup Work Applications                        | 45       |

| 3.1 OpenVAF                                                 | 45       |

| 3.2 Ngspice                                                 | 46       |

| Chapter IV: Build the Model                                 | 48       |

| 4.1 nMOS Model with Verilog-A                               | 48       |

| 4.1.1 Pinch-off Voltage for a nMOS                          | 49       |

| 4.1.2 Thermodynamic Voltage for a nMOS                      | 50       |

| 4.1.2 Thermodynamic voltage for a myos                      | 50       |

| 4.1.4 Inversion Coefficient for a nMOS                      | 52       |

| 4.1.4 Inversion Coefficient for a myos                      | 52<br>52 |

|                                                             | 52<br>53 |

| 4.2 Temperature Variation of nMOS Analog Device Parameters  | 53       |

| 4.2.1 Threshold Voltage Temperature Dependence              |          |

| 4.2.2 Slope Factor Temperature Dependence                   | 54       |

| 4.2.3 Mobility of the Channel Region Temperature Dependence | 55       |

| 4.3 Length Variation of nMOS Analog Device Parameters       | 55       |

| 4.4 Capacitance of the nMOS Device                          | 58       |

| 4.5 Extension of the nMOS Model                             | 60       |

| 4.5.1 Node Charges                                          | 61       |

| 4.5.1.1 Normalized Intrinsic Node Charges                   | 61       |

| 4.5.1.2 Total Charges                                       | 62       |

| 4.5.2 Transconductances of a nMOS Device                    | 63       |

| 4.5.2.1 Source Transconductance                             | 63       |

| 4.5.2.2 Output Conductance                                  | 64       |

| 4.5.2.3 Gate Transconductance                               | 65       |

| 4.5.3 Velocity Saturation Voltage of a nMOS Device          | 66       |

| 4.5.4 Noise Effects                                         | 66       |

| 4.5.4.1 Thermal Noise                                       | 67       |

| 4.5.4.2 Flicker Noise                                       | 69       |

| 4.5.5 Operating Point of a nMOS Device                      | 70       |

| 4.6 pMOS Model with Verilog-A                               | 73       |

| Chapter V: Simulation and Results                           | 75       |

| 5.1 Length Scaling                                          | 75       |

| 5.2 Temperature Scaling                                     | 79       |

| 5.3 Gate Behaviour                                          | 83       |

| 5.4 Source Behaviour                                        | 94       |

| 5.5 Common Source Amplifier                                 | 99       |

| 5.6 Source Transconductance                                 | 00       |

|                                                             | 06       |

|                                                             | 11       |

|                                                             | 14       |

| 1                                                           | 16       |

|                                                             | 18       |

## LIST OF ILLUSTRATIONS

| Number | r                                                                                                   | age |

|--------|-----------------------------------------------------------------------------------------------------|-----|

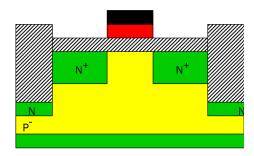

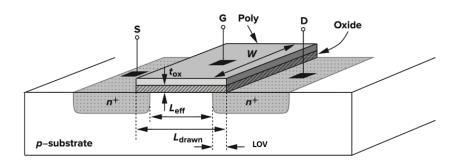

| 2.1    | Graphical scheme of the layout of a nMOS                                                            | 18  |

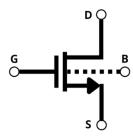

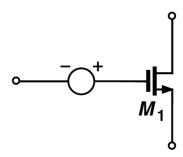

| 2.2    | Symbol of a nMOS                                                                                    | 19  |

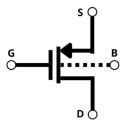

| 2.3    | Symbol of a pMOS                                                                                    | 19  |

| 2.4    | Graphical scheme of the MOSFET Accumulation zone                                                    | 20  |

| 2.5    | Graphical scheme of the MOSFET Depletion zone                                                       | 21  |

| 2.6    | Graphical scheme of the MOSFET Inversion zone                                                       | 23  |

| 2.7    | Graphical scheme of the MOSFET Cut-off region                                                       | 25  |

| 2.8    | Graphical scheme of the MOSFET lineal region                                                        | 26  |

| 2.9    | Graphical scheme of the MOSFET Saturation region                                                    | 28  |

| 2.10   | MOSFET Characteristic curve                                                                         | 34  |

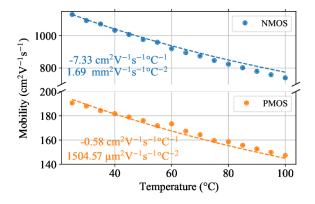

| 2.11   | Mobility versus temperature MOSFET characteristic                                                   | 37  |

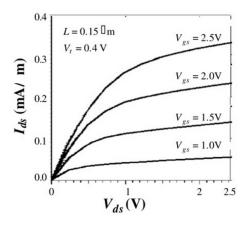

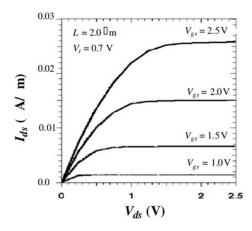

| 2.12   | Output characteristic of a short device                                                             | 42  |

| 2.13   | Output characteristic of a long device                                                              | 42  |

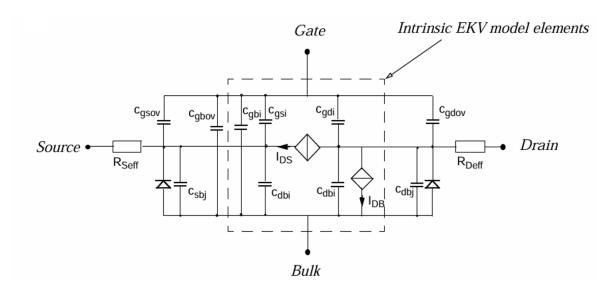

| 2.14   | Intrinsic and extrinsic elements of the MOS transistor for the EKV Model                            | 43  |

| 3.1    | Example of compilation and simulation of the model, in the terminal WSL                             | 47  |

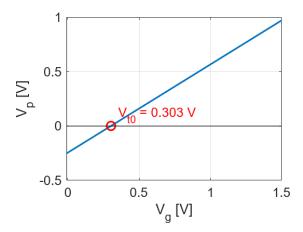

| 4.1    | Pinch-off Voltage versus Gate Voltage of a nMOS                                                     | 50  |

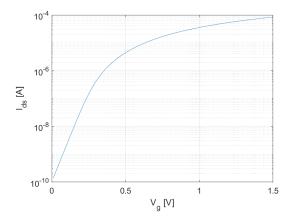

| 4.2    | The drain to source current versus the gate voltage. $L = 1.0 \mu m$ and $W = 0.5 \mu m$            | 58  |

| 4.3    | Graphical scheme of the MOSFET with the overlap length appreciation                                 | 59  |

| 4.4    | Noise disturbing as a voltage source                                                                | 69  |

| 4.5    | Noise disturbing as a current source                                                                | 69  |

| 4.6    | The inversion coefficient versus the overdrive voltage. $L = 0.5 \mu m$ and $W =$                   |     |

|        | $0.5\mu m$                                                                                          | 72  |

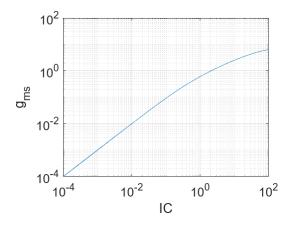

| 4.7    | Normalized source transconductance versus the inversion coefficient                                 | 72  |

| 4.8    | Normalized output conductance versus the inversion coefficient                                      | 72  |

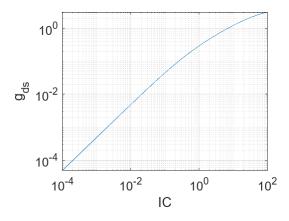

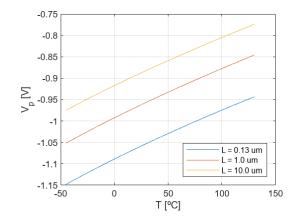

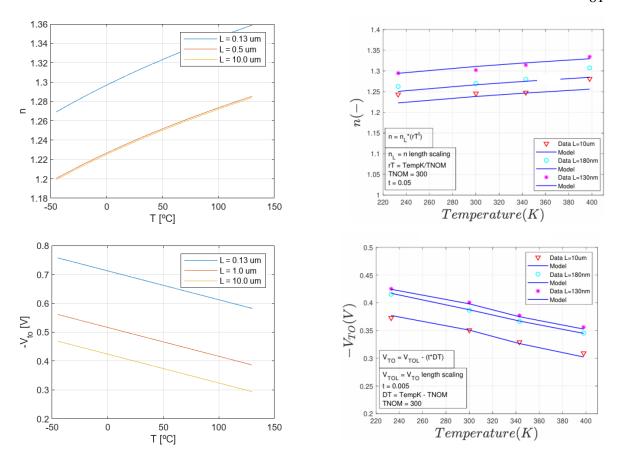

| 5.1    | The parameters $I_0$ , $\lambda_c$ , $n$ and $V_{to}$ versus the length of the channel of the nMOS. |     |

|        | The left column shows the result of the model operating at 37°C and the right                       |     |

|        | column shows experimental values of the nMOS [16]                                                   | 76  |

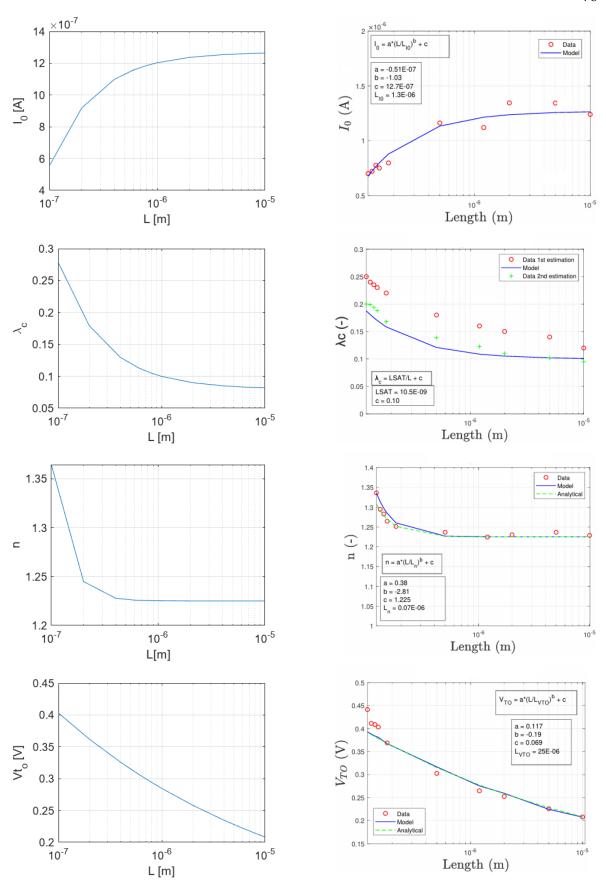

| 5.2    | The parameters $I_0$ , $\lambda_c$ , $n$ and $V_{to}$ versus the length of the channel of the pMOS. |     |

|        | The left column shows the result of the model operating at 37°C and the right                       |     |

|        | column shows experimental values of the pMOS [16]                                                   | 77  |

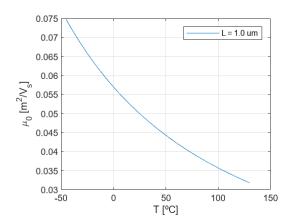

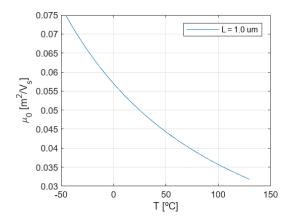

| 5.3    | The low field mobility in the channel region versus the temperature of the nMOS.                    | 79  |

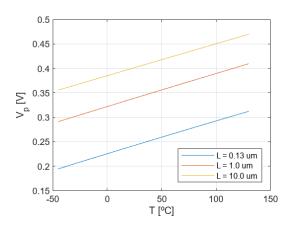

| 5.4  | The pinch-off voltage versus the temperature of the nMOS                            | 79 |

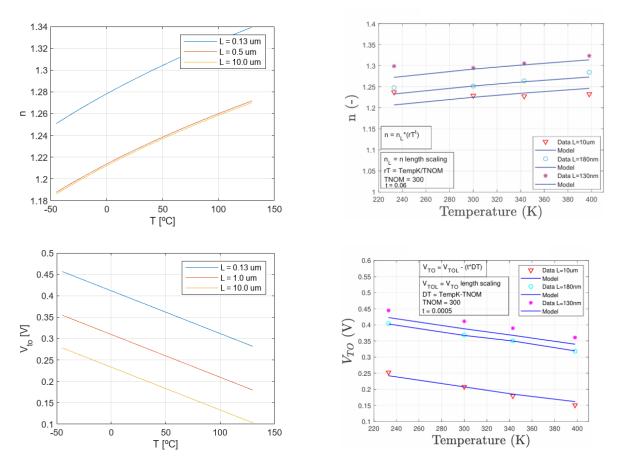

|------|-------------------------------------------------------------------------------------|----|

| 5.5  | The parameters $n$ and $V_{to}$ versus the temperature of the nMOS. The left column |    |

|      | shows the result of the model and the right column shows experimental values        |    |

|      | of the nMOS [16]                                                                    | 80 |

| 5.6  | The low field mobility in the channel region versus the temperature of the pMOS.    | 80 |

| 5.7  | The pinch-off voltage versus the temperature of the pMOS                            | 80 |

| 5.8  | The parameters $n$ and $V_{to}$ versus the temperature of the pMOS. The left column |    |

|      | shows the result of the model and the right column shows experimental values        |    |

|      | of the pMOS [16]                                                                    | 81 |

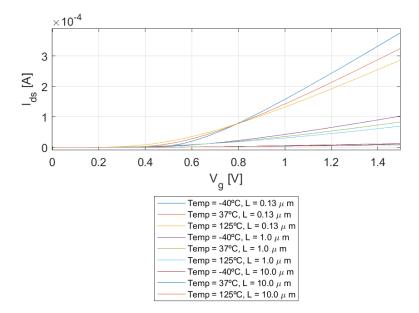

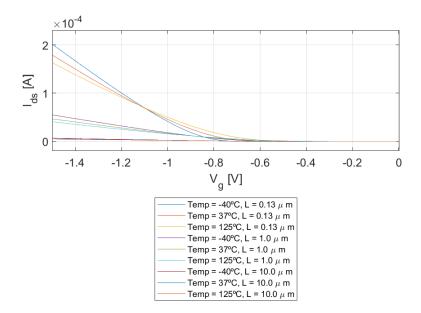

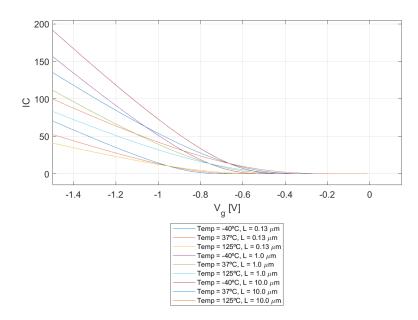

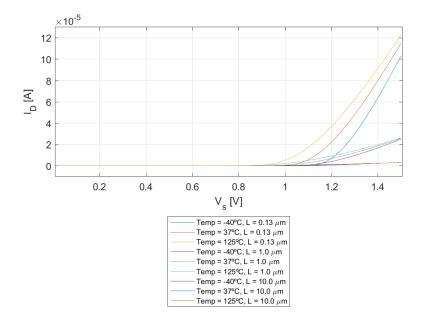

| 5.9  | The drain current versus the gate voltage of the nMOS. $I_{ds}$ is represented in   |    |

|      | linear scale                                                                        | 83 |

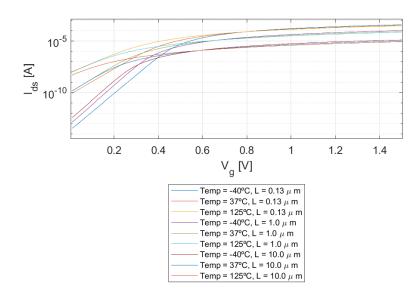

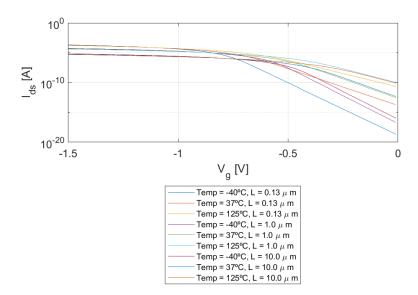

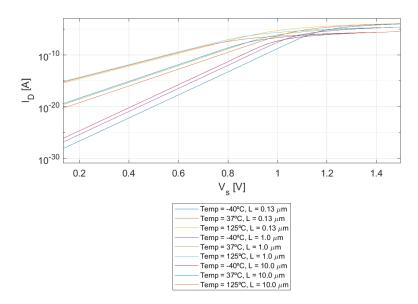

| 5.10 | The drain current versus the gate voltage of the nMOS. $I_{ds}$ is represented in   |    |

|      | logarithmic scale                                                                   | 84 |

| 5.11 | The drain current versus the gate voltage of the pMOS. $I_{ds}$ is represented in   |    |

|      | linear scale                                                                        | 84 |

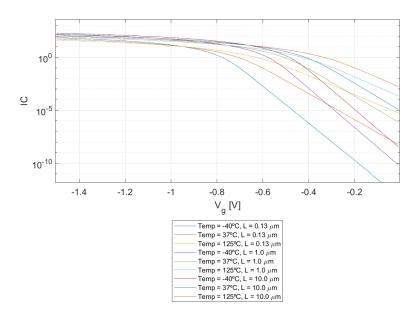

| 5.12 | The drain current versus the gate voltage of the pMOS. $I_{ds}$ is represented in   |    |

|      | logarithmic scale                                                                   | 85 |

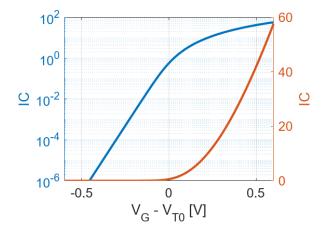

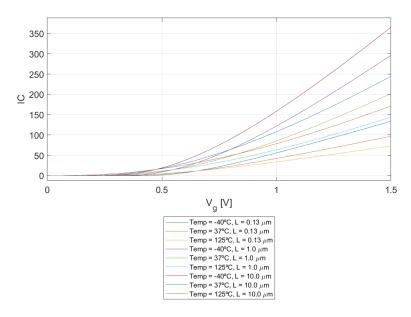

| 5.13 | The inversion coefficient versus the gate voltage of the nMOS. IC is represented    |    |

|      | in linear scale.                                                                    | 86 |

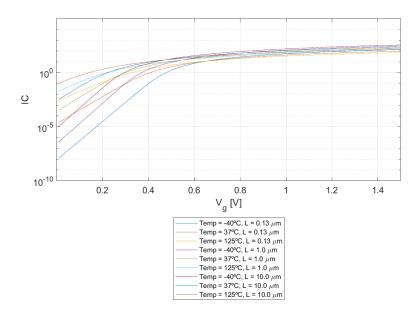

| 5.14 | The inversion coefficient versus the gate voltage of the nMOS. IC is represented    |    |

|      | in logarithmic scale.                                                               | 86 |

| 5.15 | The inversion coefficient versus the gate voltage of the pMOS. IC is represented    |    |

|      | in linear scale.                                                                    | 87 |

| 5.16 | The inversion coefficient versus the gate voltage of the pMOS. IC is represented    |    |

|      | in logarithmic scale.                                                               | 87 |

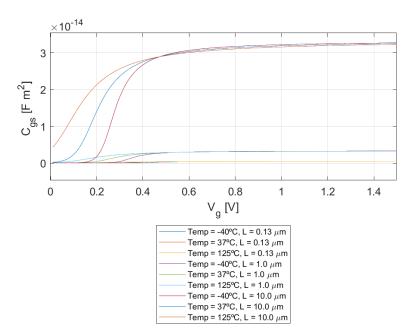

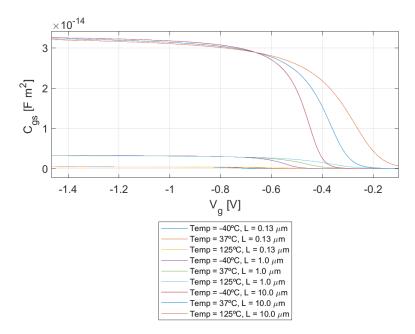

| 5.17 | The capacitance between the gate to the source versus the gate voltage of the       |    |

|      | nMOS. $C_{gs}$ is represented in linear scale                                       | 88 |

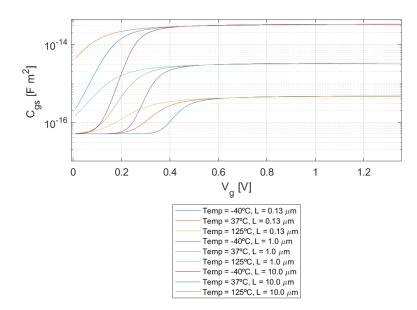

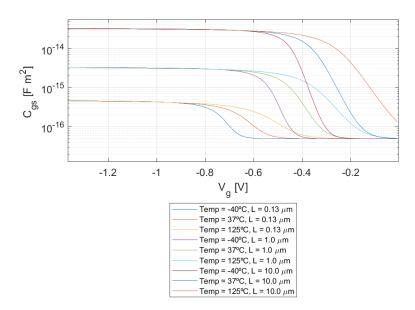

| 5.18 | The capacitance between the gate to the source versus the gate voltage of the       |    |

|      | nMOS. $C_{gs}$ is represented in logarithmic scale                                  | 89 |

| 5.19 | The capacitance between the gate to the source versus the gate voltage of the       |    |

|      | pMOS. $C_{gs}$ is represented in linear scale                                       | 89 |

| 5.20 | The capacitance between the gate to the source versus the gate voltage of the       |    |

|      | pMOS. $C_{gs}$ is represented in logarithmic scale                                  | 90 |

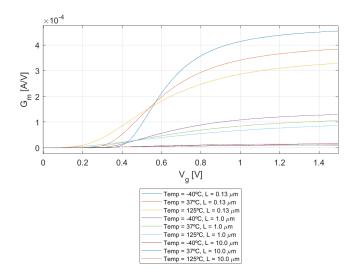

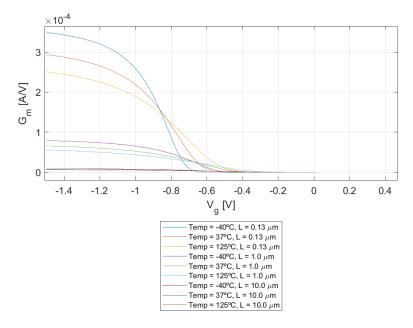

| 5.21 | The gate transconductance of the nMOS versus the gate voltage. $g_m$ is repre-      |    |

|      | sented in linear scale                                                              | 91 |

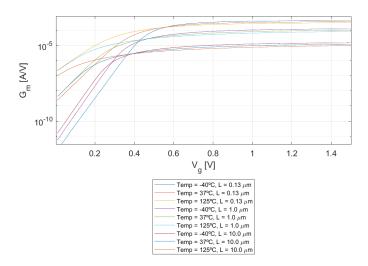

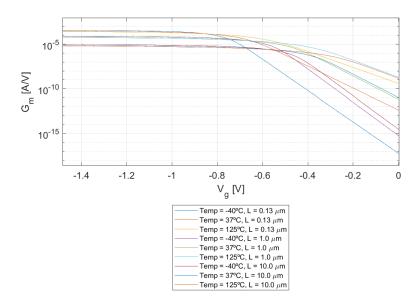

| 5.22                                | The gate transconductance of the nMOS versus the gate voltage. $g_m$ is represented in logarithmic scale                                           | 92  |

|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.23                                | The gate transconductance of the pMOS versus the gate voltage. $g_m$ is represented in linear scale                                                | 92  |

| 5.24                                | The gate transconductance of the pMOS versus the gate voltage. $g_m$ is represented in logarithmic scale                                           | 93  |

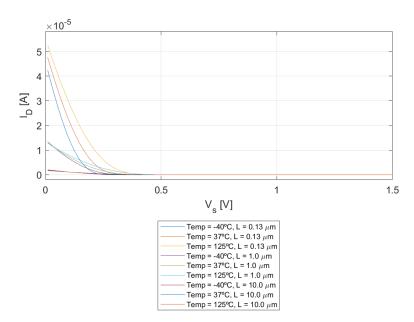

| 5.25                                | The drain current of the nMOS versus the source voltage. $I_{ds}$ is represented in linear scale                                                   | 94  |

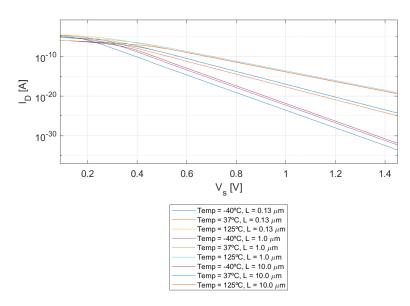

| 5.26                                | The drain current of the nMOS versus the source voltage. $I_{ds}$ is represented in logarithmic scale                                              | 95  |

| 5.27                                | The drain current of the pMOS versus the source voltage. $I_{ds}$ is represented in linear scale                                                   | 95  |

| 5.28                                | The drain current of the pMOS versus the source voltage. $I_{ds}$ is represented in logarithmic scale                                              | 96  |

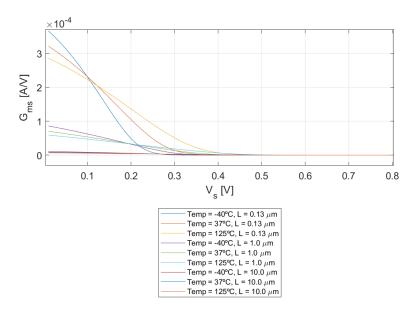

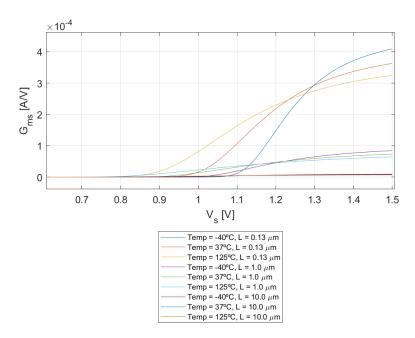

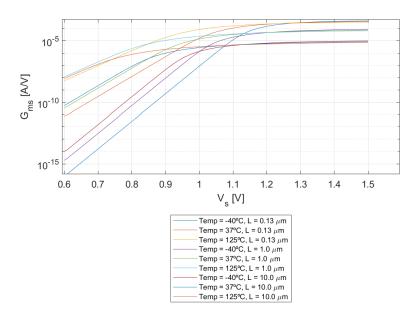

| 5.29                                | The source transconductance of the nMOS versus the source voltage. $g_{ms}$ is represented in linear scale                                         | 97  |

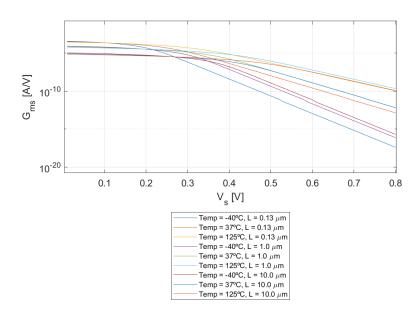

| 5.30                                | The source transconductance of the nMOS versus the source voltage. $g_{ms}$ is represented in logarithmic scale                                    | 97  |

| 5.31                                | The source transconductance of the pMOS versus the source voltage. $g_{ms}$ is represented in linear scale                                         | 98  |

| 5.32                                | The source transconductance of the pMOS versus the source voltage. $g_{ms}$ is represented in logarithmic scale                                    | 98  |

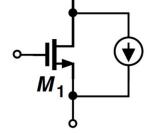

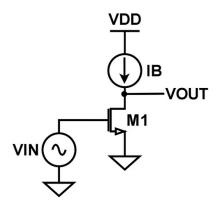

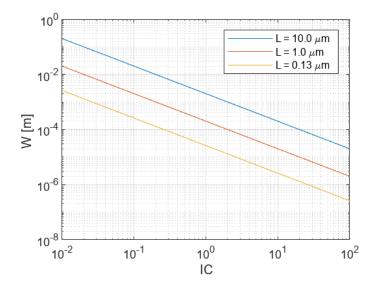

| <ul><li>5.33</li><li>5.34</li></ul> | Schematic of a Common source amplifier with ideal current source load The coefficient of inversion versus the wight of the nMOS in a common source | 99  |

|                                     | amplifier                                                                                                                                          | 100 |

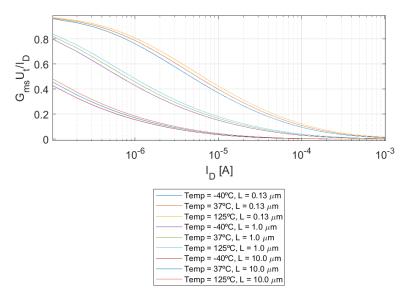

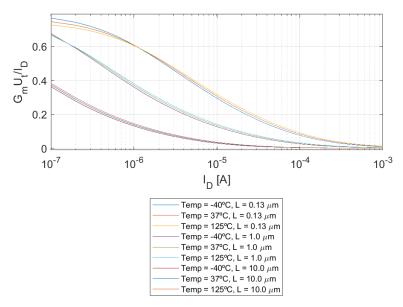

| 5.35                                | $\frac{G_{ms} \cdot U_t}{I_{ds}}$ of the nMOS versus the drain current. $\frac{G_{ms} \cdot U_t}{I_{ds}}$ is represented in linear scale           | 101 |

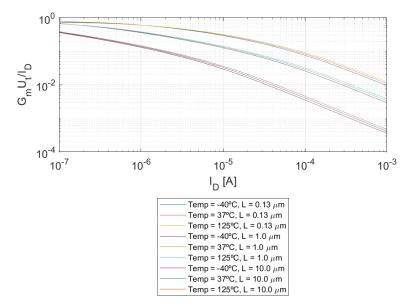

| 5.36                                | $\frac{G_{ms} \cdot U_t}{I_{ds}}$ of the nMOS versus the drain current. $\frac{G_{ms} \cdot U_t}{I_{ds}}$ is represented in logarithmic scale      | 101 |

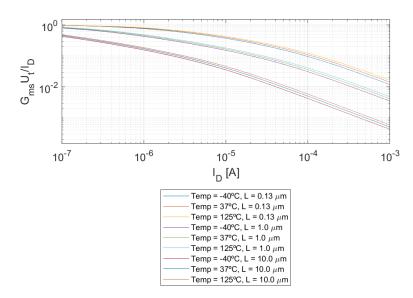

| 5.37                                | $\frac{G_{ms} \cdot U_t}{I_{ds}}$ of the pMOS versus the drain current. $\frac{G_{ms} \cdot U_t}{I_{ds}}$ is represented in linear scale           | 102 |

| 5.38                                | $\frac{G_{ms} \cdot U_t}{I_{ds}}$ of the pMOS versus the drain current. $\frac{G_{ms} \cdot U_t}{I_{ds}}$ is represented in logarithmic scale      | 102 |

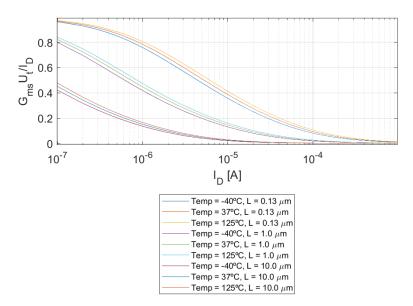

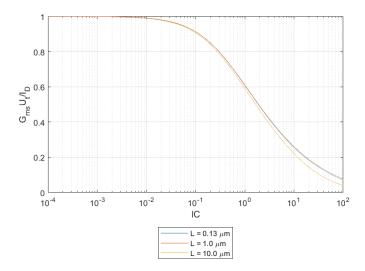

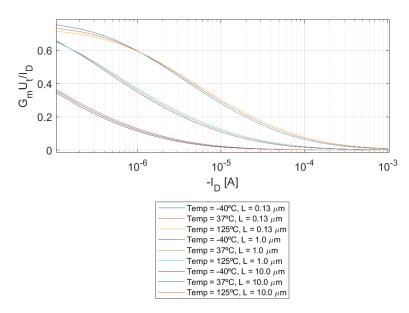

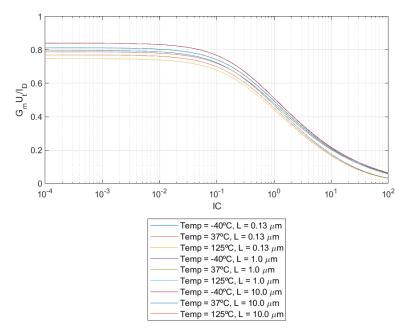

| 5.39                                | $\frac{G_{ms} \cdot U_t}{I_{ds}}$ of the nMOS versus the inversion coefficient. $\frac{G_{ms} \cdot U_t}{I_{ds}}$ is represented in linear scale   | 103 |

|                                     | IIIICAI SCAIC                                                                                                                                      | 103 |

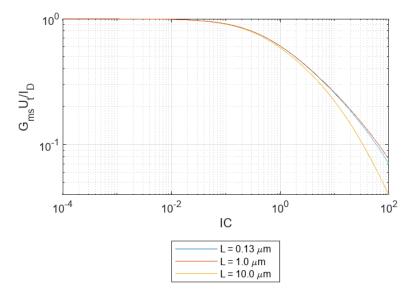

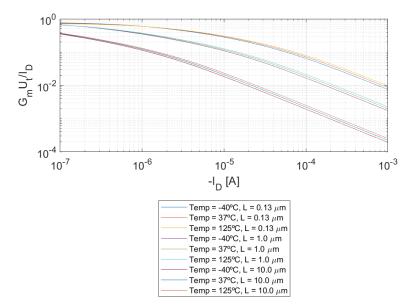

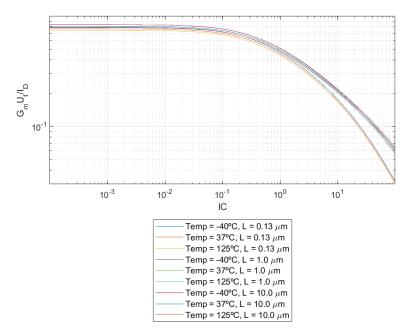

| 5.40 | $\frac{G_{ms} \cdot U_t}{I_{ds}}$ of the nMOS versus the inversion coefficient. $\frac{G_{ms} \cdot U_t}{I_{ds}}$ is represented in     |

|------|-----------------------------------------------------------------------------------------------------------------------------------------|

|      | logarithmic scale                                                                                                                       |

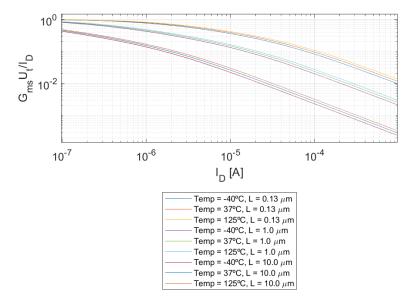

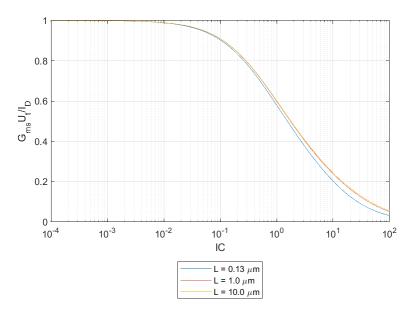

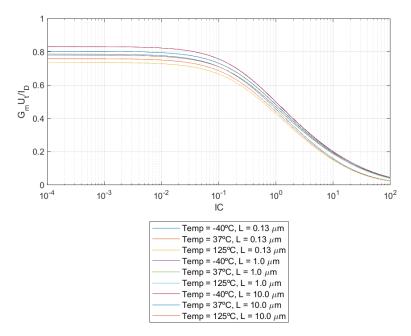

| 5.41 | $\frac{G_{ms} \cdot U_t}{I_{ds}}$ of the pMOS versus the inversion coefficient. $\frac{G_{ms} \cdot U_t}{I_{ds}}$ is represented in     |

|      | linear scale                                                                                                                            |

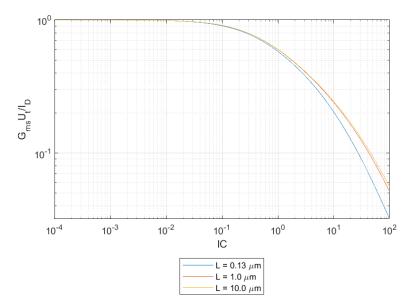

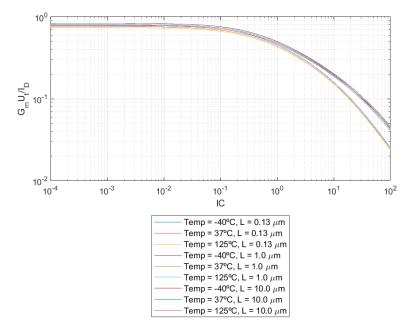

| 5.42 | $\frac{G_{ms} \cdot U_t}{I_{ds}}$ of the pMOS versus the inversion coefficient. $\frac{G_{ms} \cdot U_t}{I_{ds}}$ is represented in     |

|      | logarithmic scale                                                                                                                       |

| 5.43 | $\frac{G_m \cdot U_t}{I_{ds}}$ of the nMOS versus the drain current. $\frac{G_m \cdot U_t}{I_{ds}}$ is represented in linear scale. 106 |

| 5.44 | $\frac{G_m \cdot U_t}{I_{ds}}$ of the nMOS versus the drain current. $\frac{G_m \cdot U_t}{I_{ds}}$ is represented in logarithmic       |

|      | scale                                                                                                                                   |

| 5.45 | $\frac{G_m \cdot U_t}{I_{ds}}$ of the pMOS versus the drain current. $\frac{G_m \cdot U_t}{I_{ds}}$ is represented in linear scale. 107 |

| 5.46 | $\frac{G_m U_t}{I_{ds}}$ of the pMOS versus the drain current. $\frac{G_m U_t}{I_{ds}}$ is represented in logarithmic                   |

|      | scale                                                                                                                                   |

| 5.47 | $\frac{G_m \cdot U_t}{I_{ds}}$ of the nMOS versus the inversion coefficient. $\frac{G_m \cdot U_t}{I_{ds}}$ is represented in           |

|      | linear scale                                                                                                                            |

| 5.48 | $\frac{G_m \cdot U_t}{I_{ds}}$ of the nMOS versus the inversion coefficient. $\frac{G_m \cdot U_t}{I_{ds}}$ is represented in           |

|      | logarithmic scale                                                                                                                       |

| 5.49 | $\frac{G_{m} \cdot U_{t}}{I_{ds}}$ of the pMOS versus the inversion coefficient. $\frac{G_{m} \cdot U_{t}}{I_{ds}}$ is represented in   |

|      | linear scale                                                                                                                            |

| 5.50 | $\frac{G_m \cdot U_t}{I_{ds}}$ of the pMOS versus the inversion coefficient. $\frac{G_m \cdot U_t}{I_{ds}}$ is represented in           |

|      | logarithmic scale                                                                                                                       |

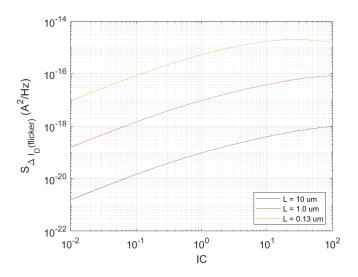

| 5.51 | Density of the flicker noise in the drain current versus the inversion coefficient                                                      |

|      | of a nMOS with a fixed $W = 0.5\mu m.$                                                                                                  |

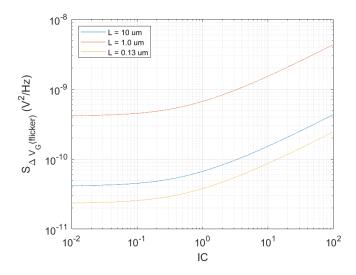

| 5.52 | Density of the flicker noise in the gate voltage versus the inversion coefficient                                                       |

|      | of a nMOS with a fixed $W = 0.5 \mu m$                                                                                                  |

|      | •                                                                                                                                       |

## LIST OF TABLES

| Number | r                                                       | Page |

|--------|---------------------------------------------------------|------|

| 4.1    | Parameters of the first nMOS model                      | 49   |

| 4.2    | Parameters for temperature dependence of the nMOS model | 53   |

| 4.3    | Parameters for length dependence of the nMOS model      | 55   |

| 4.4    | Parameters for length scaling of the nMOS model         | 56   |

| 4.5    | Parameter for capacitance of the nMOS model             | 58   |

| 4.6    | Parameters for output conductance of the nMOS model     | 64   |

| 4.7    | Parameters for flicker noise effects of the nMOS model  | 67   |

| 4.8    | Values of the operating point                           | 71   |

| 4.9    | Parameters for length scaling of the model              | 73   |

#### **ACRONYMS**

MOSFET Metal-Oxide-Semiconductor Field-Effect Transistor

**CMOS** Complementary Metal-Oxide-Semiconductor

**EKV** Enz-Krummenacher-Vittoz

**DC** Direct Current

**AC** Alternating Current

NMOS Negative-channel Metal-Oxide-SemiconductorPMOS Positive-channel Metal-Oxide-Semiconductor

**QS** Quasi-Static

NQS Non-Quasi-Static

IC Inversion Coefficient

**ID** Drain Current

#### **INTRODUCTION**

#### 1.1 Background

In the contemporary era, analogue integrated circuits are being utilized with greater frequency in a variety of industrial applications and environments. Consequently, the design of these circuits is subject to constant evolution and progression, with the objective of addressing the demand for reduced power consumption and enhanced energy efficiency. In this context, MOSFET transistors assume a particularly salient role, given their status as the primary active device in the majority of analogue circuits.

It is imperative to exercise a high degree of control over these transistors, given their pivotal role in determining the performance, gain, and linearity of the circuit. This is particularly true when considering the mode of operation of the transistors in different inversion regions, categorized as weak, moderate, or strong.

In order to obtain an accurate and flexible representation of the behaviour of a MOSFET, it is necessary to use compact models that allow continuous simulation in the different operating regions. This will be of vital importance in processes that require advanced technology and lower power consumption. The solution to this growing market need was the development of the EKV model. This model provides a precise description of the second-order effects to which MOSFET transistors are subjected, such as channel length modulation or vertical field mobility reduction, among others.

Concurrently, significant advancements have been made in the analytical modeling of these analogue circuits. Concurrently, languages that implement the description of these circuits, such as Verilog-A, have also advanced. It is possible to implement customized models of different analogue devices for subsequent simulation in environments such as Ngspice or Spectre by utilizing this language. Consequently, Verilog-A has become a versatile and widely utilized language among engineers seeking to develop compact portable models, incorporate tangible effects into existing models, or validate such models against experimental data.

In this context, the present paper focuses on the study, construction and implementation of a compact model of an EKV transistor using the Verilog-A language. The implementation of this process will be facilitated by the utilization of the OpenVAF and Ngspice environments. The objective of this study is to ascertain the behaviour of the MOSFET under various

polarization and temperature conditions. The analysis will extract parameters such as the drain current, capacitances, and transconductances, along with other fundamental operating values, to ensure the effective functioning of an analogue circuit.

In addition to the acquisition of a theoretical and mathematical functional model and the advancement of associated theoretical research, the objective of this work is to utilize this model in professional simulation environments.

#### 1.2 Objectives of Work

The aim of this thesis is to fulfill a series of objectives in order to construct a model correctly and ensure its behaviour. It will also make a suitable contribution to future works.

- Learn to handle the different development environments, OpenVAF and Ngspice. Master the programming languages needed to use them: Verilog-A and SPICE.

- Create a functional Verilog-A model of an nMOS and pMOS transistor operating under saturation conditions and in any inversion region.

- Obtain the operating point of the device, as well as the drain current, main voltages, capacitances and transconductances at different temperatures.

- Prepare the model for use in more complex analogue circuits.

- Verify that the model is functioning correctly through its parameters and variables. Verify that it responds as expected in different environmental situations.

#### 1.3 Outline

The document is divided into chapters where:

**Chapter 1 - Introduction:** The objectives of the thesis, the concept of the work, and the methodology are introduced.

**Chapter 2 - Theoretical Background:** An explanation of the technology addressed in this work. This includes the characteristics of the MOSFETs, regions of operation, prominent architectures, and the effects to be considered when modeling the analogue device.

**Chapter 3 - Setup Work Applications:** Description of how the working applications were prepared. This includes the open server, OpenVAF, and the compatible simulator, Ngspice.

**Chapter 4 - Build the Model:** Construction of the model. The steps followed to create the Verilog-A model, including the considerations, expressions and parameters used.

**Chapter 5 - Simulation and Results:** Analysis of the results obtained from the model. Verification of the correct functioning of the code.

**Chapter 6 - Conclusions and future work:** Presentation of the final conclusions of the work carried out and some proposals for future work.

#### 1.4 Related Work

The following documents have been selected as the primary reference material for this study. In order to achieve a more profound comprehension of the operational mechanics of the EKV model, it is imperative to ascertain the parameters of its essential values. This undertaking is undertaken with the objective of elucidating the effects that exert influence on the model.

# 1.4.1 Nanoscale MOSFET Modeling: The simplified EKV model for the design of low-power analog circuits

This article introduces the EKV (Enz-Krummenacher-Vittoz) model, a compact and accurate alternative to traditional models for designing the characteristics of MOSFETs in processes requiring the most advanced CMOS technology. It also explains how the inversion coefficient (IC) can be used as an alternative to the over-excitation voltage, the difference in voltage between the gate and the source, and the threshold voltage. The introduction of the inversion coefficient enables the model to be used in weak, moderate, and strong inversion operations. The EKV model is oriented towards nanometer technologies in the saturated state and enables MOSFETs to be characterized with a small number of parameters while maintaining high accuracy in current and transconductance values.

# 1.4.2 Nanoscale MOSFET Modeling: Using the inversion coefficient as the primary design parameter

This document is a continuation of 'Nanoscale MOSFET Modelling Part 1'. Here, the inversion coefficient is the primary variable used to model analogue circuits with advanced CMOS technology. The simplified EKV design is used for the analysis of the essential variables of analogue circuits, taking into account only the main parameters. These variables are analysed in the three inversion modes: weak, moderate and strong. An attempt is then

made to extract the operating point. In this article, we derive simple expressions for MOSFETs as a function of IC to enable quicker analysis of behaviour, eliminating the need for external simulations. To validate the results, the model is compared with real measurements of devices of various sizes, as well as with the BSIM6 model.

# 1.4.3 Optimizing Drain Current, Inversion Level, and Channel Length in Analog CMOS Design

This article proposes a methodology for designing analogue circuits in which several parameters can be optimized simultaneously. The inversion coefficient, the drain current and the channel length are optimized here, forming the basis of the rest of the model. This approach provides greater control over the MOSFET inversion regime and enables the simultaneous optimization of power, gain, bandwidth and noise efficiency. The paper also examines channel saturation voltage, voltage and current mismatches, as well as thermal and flicker noise.

#### 1.4.4 Tradeoffs and Optimization in Analog CMOS Design

It presents a methodology for optimizing the design of integrated circuits using CMOS technology. The inversion coefficient is used as the main variable to characterize the devices, with the aim of controlling their performance and power consumption. The study employs the EKV model and empirical data to verify the correct operation of the methodology. The paper also discusses the MOSFET operating plane, which is a visual tool used to determine the optimal operating regions of the MOSFET according to the applicable requirements. Additionally, it analyses how parameters such as transconductance efficiency, velocity saturation, thermal noise density, and flicker density react to different operating points.

#### 1.4.5 The EPFL-EKV MOSFET Model Equations for Simulation

This article presents a compact EKV model of a MOSFET transistor. It has been designed to be compatible with the simulation of more complex analogue circuits. The model focuses on characterizing low-power nanometer MOSFETs so that their behaviour in all inversion regions can be simulated continuously. This is made possible by the mathematical formulation used in the model. Another notable feature is that the model has unique and continuous expressions for the device's various operating modes. The model is structured into two sections: the intrinsic parameters, which describe the behaviour of the transistor; and the

extrinsic parameters, which model the contact resistance, capacitance, and diodes located between the terminals of the MOSFET.

#### 1.4.6 EKV3. MOSFET Compact Model. Model's Documentation

This paper presents an enhanced version of the compact EKV 2.6 model. While it follows the same dynamics as the previous model, it attempts to unify the expressions so that the model can operate across all regions and inversion levels. However, this article improves upon the previous one by implementing a more detailed model that incorporates geometric variation, device mismatch, and other adverse effects that can affect the device. The model also takes into account the presence of intrinsic and parasitic capacitances, as well as leakage currents and temperature influence.

#### THEORETICAL BACKGROUND

To realize the design and characterization of a circuit based on MOSFET technology first requires a proper understanding of this technology. The definition of a MOSFET is a field transistor that is used in electronics to amplify the commutation of a signal [1]. The MOSFET (Metal Oxide Semiconductor Field Effect Transistor) is a devise with a majority of carriers, which can be electrons or voltaic voids depending on whether we talk about a nMOS or a pMOS.

#### 2.1 Construction of a MOSFET

To manufacture a MOSFET device, a series of specific processes must be carried out, but before this it is vital to subject the substrate that will be the basis of the nMOS or pMOS to a series of prior preparation processes.

First of all, the state of the substrate must be checked. In the case of microelectronics applications, it is vital that the substrate has a very high degree of purity. In its natural state, silicon oxide has a purity of 98, 99%, but even this is not enough for the use of the MOSFET, so the level of unwanted impurities must be much lower than the level of impurities that will be intentionally introduced later. Apart from the purity, it must also be taken into account that the manufacturing process can be influenced by the crystalline orientation, in real crystals the surfaces present discontinuities which then affect different factors of the device, and it must also be taken into account that the crystal will present defects, both native and interstitial, which will cause the periodicity of the network to be lost.

One of the processes that must be carried out prior to the manufacture of the device is to obtain purified silicon. To achieve this, a series of chemical and physical processes must be carried out on the silicon. With the chemical processes, polycrystalline silicon can be obtained with a degree of purity of up to 99.999999%. But for the manufacture of MOSFETs, a purity of 99.9999999% is required, so from that point it is necessary to resort to physical processes, such as purification by zones, the nacelle method or the floating zone method.

After obtaining the desired level of purity, it is necessary to transform the semiconductor into a rod-shaped single crystal, with a certain crystalline orientation and type of doping. To achieve this, two different methods are usually used, the Czochralski method and the floating

zone method. The former consists of growing a solid phase on a liquid phase contained in a crucible. The floating zone method is more similar to recrystallization than to growth from a liquid phase, and is therefore more complex than the former, but the profiles obtained are more homogeneous.

The last step before manufacturing the MOSFET would be the preparation of the substrate, first the single crystal must be marked so that its crystalline orientation and the type of doping can be known. Then the single crystal would have to be cut to form the wafers, this is done with special saws whose edge contains diamond powder. Finally, the substrate would have to be polished to remove any remaining damage and defects on the surface, which would be achieved by both mechanical and chemical polishing.

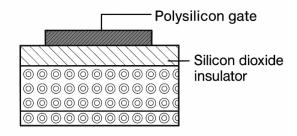

After all the previous processes we can start building a MOSFET, for which we will need to follow a series of steps; diffusion, ionic implantation, epitaxial growth, ... as it's explained in [2] The process is similar for nMOS and pMOS, for a nMOS a subtract type p is needed. Then the subtract is treated through different procedures, first a termical oxidation to form three layers SiO<sub>2</sub>, Si<sub>2</sub>N<sub>3</sub> and SiO<sub>2</sub>. After that a photo-resin is applied and through a lithography process the areas of the drain and the source will be isolating. With a ionic implantation the braking channels are build.

One's you have the braking channels another oxidation is made, leaving inside that layer  $Si_3N_4$  to make sure the oxide don't enter where the transistors should be place. Then the superficial isolating is removed.

The next step is the emplacement of the polysilicon, for that a layer is place and then using again the process of lithography the rest of it is removed leaving only the polysilicon of the gate.

The last step will be a ionic implantation of phosphorous, arsenic and antimony, thanks to which the drain and the source are created. And with that the nMOS will be build, as is shown in figure 2.1.

Figure 2.1: Graphical scheme of the layout of a nMOS.

(Maria Cristina Perez Barreiro (2024). "Tema 2: Procesos de Fabricación". *Microelectronics. University of Valladolid.*)

In the other hand, for a pMOS the process is almost the same, the difference is that the pMOS is build from a subtract type n and the ionic implantation is made with boron instead of antimony, arsenic and phosphorous.

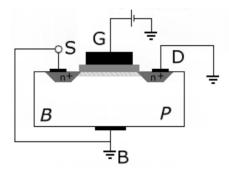

#### 2.2 Operation of a MOSFET

Within the MOSFET devices a distinction can be made between nMOS and pMOS, both are majority carrier devices but in the nMOS the carriers are electrons and in the pMOS they are electrons and in the pMOS they are holes. The nMOS devices work in such a way that if the gate voltage is less than the threshold voltage the channel remains cut off, so that the current flowing between the drain and the source is practically zero. However, when the gate voltage is positive with respect to the substrate voltage, electrons appear in the channel and the conductivity increases. In pMOS, on the other hand, the behaviour is analogous: the gate voltage must be negative to cause holes to appear in the channel and thus help with conductivity.

The structure of an nMOS consists of a lightly doped P-type silicon substrate containing two heavily doped n+ regions. Between these two regions, there is a P-type region called the channel, which is covered by a layer of silicon dioxide SiO<sub>2</sub> and a layer of polycrystalline silicon forming the gate. As the oxide layer is insulating, the current from the gate to the channel is practically zero. Due to the symmetry of the structure, there is no physical difference between the drain and the source. The three terminals are located on the surface, and sometimes a fourth terminal is used for the bulk.

Analogous to the nMOS, the pMOS has an N-type substrate, which contains the heavily

doped p-type regions that will be the source and the drain.

Figure 2.2: Symbol of a nMOS.

(Jorge Iván Cuevas Chávez (2024)

"Caracterización eléctrica del circuito sujetador parásito en circuitos CMOS de compuerta cuasi-flotante" *Technological Institute of Cd. Guzmán.*)

Figure 2.3: Symbol of a pMOS.

(Jorge Iván Cuevas Chávez (2024)

"Caracterización eléctrica del circuito sujetador parásito en circuitos CMOS de compuerta cuasi-flotante" *Technological Institute of Cd. Guzmán.*)

Focusing on the general operation of these devices, we will talk in a generic way about the different regions of operation, both about the effects seen in the device in each of these regions and about the conditions in which a MOSFET is found in each of these regions.

If we focus for the moment on the behaviour of an nMOS, we know that the two most basic concepts for it to work correctly are that it is necessary to apply a positive voltage between the drain and the source and that if the voltage between the gate and the source is zero, no current flows through the channel because the drain and the source are isolated. However, when a voltage starts to be applied to the positive gate with respect to the source, we know that an electric field starts to appear which repels the holes and attracts the electrons towards the gate, thus increasing the conductivity of the channel. Thus, when this voltage continues to increase, there comes a point where the bulk area under the gate is no longer P-type and becomes N-type due to the dense accumulation of electrons. At this point the channel is created between the drain and the source and the current is allowed to flow. Once the channel is created, with a suitable voltage  $V_{ds}$ , current will exist between the drain and the source, until the voltage becomes so great that the channel recedes from the vicinity of the drain. This is known as the saturation region and will be the conditions under which we work here.

#### 2.2.1 Sub-threshold Region

Looking at the different situations mentioned above, we will start with the sub-threshold region. the transistor is in this area as long as there is no channel formed between the drain and the source, which is always the case when the voltage between the gate and the source is less than the threshold voltage. However, within this region we can also find different situations, we find the accumulation region, the depletion region and the inversion region, which differ from each other according to the value of the voltage between the gate and the source.

#### 2.2.1.1 Accumulation Zone

Looking at the different situations mentioned above, we will start with the accumulation zone. This is when the voltage  $V_{gs}$  is well below the threshold voltage and negative, in this region the bulk structure remains in its initial distribution, like its show in the figure 2.4. In this situation the MOS structure can be seen as a capacitance associated with the gate due to the oxide separating the gate and the semiconductor. This capacitance is called the specific oxide capacitance per area unit  $C_{ox}$ , and we will see that this capacitance affects the rest of the behaviour of the MOSFET. The specific oxide capacitance per area unit is given by Equation 2.1 [3], where  $\varepsilon_{ox}$  is the permittivity of the oxide and  $X_{ox}$  is the width of the oxide.

Figure 2.4: Graphical scheme of the MOSFET Accumulation zone.

$$C'_{ox} = \frac{\varepsilon_{ox}}{t_{ox}} \tag{2.1}$$

In this region, as already mentioned, we work with negative gate voltages, so due to the field created in the oxide by this voltage, the majority carriers are attracted and concentrate at the junction between the oxide and the semiconductor. Due to this polarization, the MOSFET behaves like a capacitor.

Another concept associated with this is the total oxide capacitance of a given transistor  $C_{ox}$  which results from the product of the specific oxide capacitance per unit area and the actual area of the transistor under consideration, Equation 2.2 [3].

$$C_{ox} = C'_{ox} \cdot L \cdot W \tag{2.2}$$

#### 2.2.1.2 Depletion Zone

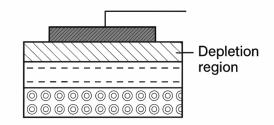

If the voltage between the gate and the source continues to increase, the accumulation zone is left behind and the depletion zone is entered. This is so called because the voids that were previously next to the oxide are now repelled towards the bottom of the bulk, thus creating a charge-free region or depletion zone, as you can see in the figure 2.5. In this area of operation, the voltage between the gate and the source is positive, but still below the threshold voltage.

Figure 2.5: Graphical scheme of the MOSFET Depletion zone.

The increased voltage creates an electric field in the oxide, called  $\varepsilon_{ox}$ , which points to the bulk and also creates a field that penetrates the semiconductor  $\varepsilon(x)$ . The electric field generates a voltage in the crystal that will be maximum at the surface, and decreases to zero  $(V_b = 0)$  at the bottom of the crystal.

The electric field in the crystal acts on the carrier concentration, especially at the surface. Due to the effect of the electric field, the emptiness zone extends to a depth  $X_d$ . This region, without free carriers, has only uncovered charges and is called the space charge. The width of the vacancy zone can be calculated using the one-dimensional Poisson solution for an abrupt junction, giving the Equation 2.3 [4], where  $\varepsilon_{si}$  is the permittivity of silicon,  $\phi_s$  is the

potential at the crystal surface, q the electron charge and Na is the initial concentration of the P-type crystal.

$$X_d = \sqrt{\frac{2 \,\varepsilon_{\rm si} \,\phi_s}{q \,N_a}} \tag{2.3}$$

On the other hand, the space charge can then be calculated as shows Equation 2.4 [5]. This space charge, in series with oxide capacitance  $C_{ox}$ , determines the gate-substrate capacitance curve in small-signal analysis, modeled as two capacitors in series.

$$Q_{B0} = -q N_a X_d = -\sqrt{2 \varepsilon_{si} q N_a \phi_s}$$

(2.4)

The MOSFET drain zone is therefore a direct analogy to the depletion region of a reverse biased PN junction, and plays a key role in determining the threshold voltage, input capacitance and body effect when there is source-substrate biasing. Once we know this, we could define the tension in the oxide with Equation 2.5 [4].

$$V_{ox} = -\frac{Q_{BO}}{C_{ox}'} \tag{2.5}$$

#### 2.2.1.3 Inversion Zone

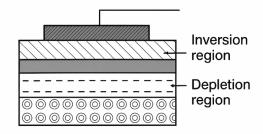

By further increasing the voltage between the gate and the source until it is higher than the threshold voltage  $V_t$ , we enter the inversion zone. Here the electrons are attracted to the region of the substrate under the gate, creating an N-type zone which will become the channel of the device and link the drain to the source, as shown in the figure. Therefore, we know that the absolute voltage to be applied to create the channel is the difference between  $V_{gs}$  and the threshold voltage. In this situation, if we were to apply voltage between the drain and the source, current could flow through the channel.

Figure 2.6: Graphical scheme of the MOSFET Inversion zone.

Under these conditions, if no voltage  $V_{ds}$  is applied the channel would be symmetrical along its entire length.

Once we enter the inversion zone and as the voltage value between the gate and the source increases, the width of the depletion zone  $X_d$  also increases. However, this zone does not grow indefinitely, but there comes a point where the field at the junction between the oxide and the substrate is so large that it causes free electrons to be directed towards the junction. When the inversion occurs, the potential at the crystal surface reaches a value called  $\phi_{si}$ , which depends on the doping level of the crystal.

To quantify this process, the Fermi potential of the bulk is used, which satisfies the following Equation 2.6, where ni is the intrinsic density. Strong inversion is reached when the  $\phi_{Si}$  potential doubles the value of the Fermi potential. When this condition is fulfilled, the formation of the channel under the gate of the MOSFET device starts, and it is at this moment that the depletion region reaches the maximum width  $X_d$ .

$$|\phi_F| = \left| \frac{K \cdot T}{q} \right| \cdot \ln(\frac{Na}{ni}) \tag{2.6}$$

Analogously to this, we know that the maximum space charge will be given when the maximum width of the depletion region is reached, Equation 2.7, so its value will be that of the following Equation 2.8 [4].

$$X_{dm} = \sqrt{\frac{2\,\varepsilon_{\rm si}}{q\,N_a}\,2\,\phi_F} \tag{2.7}$$

$$Q_{B0,\text{max}} = -\sqrt{2\,\varepsilon_{\text{si}}\,q\,N_a\,2\,\phi_F} \tag{2.8}$$

It is also known that as the voltage from the gate to the source value increases above the threshold voltage value, more inversion electrons will accumulate, whose charge is represented by QI, so that the total charge density will also increase and will follow the Equation 2.9 [6].

$$OS = Q_{RO \max} + QI \tag{2.9}$$

Once we know this we can determine the value of the gate voltage that generates the inversion process, this value will be called  $V_{t0}$  and will follow the Equation 2.10 [6].

$$V_{t0} = V_{ox} + \phi_{Si} \tag{2.10}$$

At the start of the inversion there are almost no free electrons so the charge due to these QI will be very small compared to the space charge,  $QI \ll Q_{BO}$ . Knowing this we can conclude that at this point the surface charge density is equivalent to the space charge, so the oxide tension in the depletion zone at this point will be as follows in Equation 2.11 [6].

$$V_{OX} = -\frac{Q_S}{C'_{ox}} = -\frac{Q_{B0,\text{max}}}{C'_{ox}} = \frac{\sqrt{2 q \, \varepsilon_{\text{si}} \, N_a \, 2 \, |\phi_F|}}{C'_{ox}}$$

(2.11)

If we also want to take into account the charges that will appear on the oxide, we have to add the concept of the flatband voltage VFB. This takes into account the charges on the oxide and the MOS interface, and also the difference between the work functions of the metal and the semiconductor. Therefore, if we put all these concepts together, we can obtain the gate voltage generated by the inversion process, Equation 2.12 [6].

$$V_{T0} = V_{FB} + \frac{\sqrt{2 q \varepsilon_{si} N_a 2 |\phi_F|}}{C'_{ar}} + 2 |\phi_F|$$

(2.12)

Therefore, as can be understood from the above, the sub-threshold region is characterized by a lack of current between the drain and the source, and by a voltage from the gate of the MOSFET device to the source terminal that is less than or at best equal to the threshold voltage, hence the name of this particular operating region.

#### 2.2.2 Linear Region

Having already discussed the sub-threshold or cutoff region, we can move on to the next operating region. This is where the most optimal conditions for the normal operation of the device are found, it is also the region of operation where it is easiest to predict the behaviour of the MOSFET device you are dealing with. This phenomenon can be attributed, in large part, to the observation that, within the linear region, the current traversing the  $I_{ds}$  channel exhibits a linear relationship with the voltage differential between the drain and the source, as the nomenclature would suggest.

Once the voltage between the gate and the source is high enough to be in inverting mode, if a voltage is applied between the drain and the source we obtain a current that goes from one terminal to the other. It is at this point that the device enters the linear region of operation.

Figure 2.7: Graphical scheme of the MOSFET Cut-off region.

(Vicente García. (2012) "El Transistor MOSFET. Electrónica Práctica Aplicada". https://www.diarioelectronicohoy.com/blog/el-transistor-mosfet)

Within this linear region, it is known that as the voltage  $V_{ds}$  increases, the shape of the channel changes. As previously mentioned, the channel is formed in the inversion mode, in which, as there is no voltage between the drain and the source, the channel is symmetrical throughout its length, having the same width both in the area close to the drain and the area close to the source, as you can see in the figure 2.7. However, in the linear region, as there is already a voltage  $V_{ds}$ , the part of the channel in the vicinity of the drain becomes narrower, but the original channel length remains as the figure 2.8 show.

Figure 2.8: Graphical scheme of the MOSFET lineal region.

(Diego Mallada Morales. "Modelado y caracterización del transistor MOSFET: Extracción de parámetros". *University of Valladolid. Science Department.*)

This phenomenon occurs because, on the side of the channel in closest proximity to the source terminal, the field used to create the channel is always worth the difference between the voltage  $V_{gs}$  and the threshold voltage. As previously mentioned, this value is the one used to create the channel in inversion mode, meaning that the width of the channel does not vary on the source side. Conversely, in the vicinity of the drain, the voltage that maintains the channel is no greater than the difference between the gate and the drain. Consequently, as the  $V_{ds}$  voltage increases, the channel becomes narrower.

It can be deduced from the available evidence that, while provided Equation 2.13 is satisfied the channel will maintain its original length [6].

$$V_{gs} - V_t > V_{ds} \tag{2.13}$$

In the event of the expression becoming unfulfilled due to an excessive increase in the voltage  $V_{ds}$ , it can be deduced that the voltage  $V_{gd}$  will be less than the threshold voltage. Consequently, the channel will move away from the drain, thereby initiating a decrease in the effective length of the channel. It is at this particular point that the device enters the saturation region.

As previously established, the linear region is characterized by the maintenance of constant channel length. This results in the formation of a continuous channel, which is predominantly influenced by the majority carriers. This is applicable to both nMOS electrons and pMOS holes. In this region of operation, the surface potential never cuts the channel, so that, as previously mentioned, the current between the drain and the source will be proportional to the voltage  $V_{ds}$  for a given voltage  $V_{gs}$ .

Consequently, it can be deduced that the equation for the drain current in this region is given by Equation 2.14 [3].

$$I_D = \mu C'_{ox} \frac{W}{L} \left[ (V_{GS} - V_{th}) V_{DS} - \frac{1}{2} V_{DS}^2 \right]$$

(2.14)

In this regime, the channel of the MOSFET device is to be considered as a block of silicon, the conductivity of which is governed by the Equation 2.15 [4], where n(x) is the density of the majority carriers, which is dependent on the gate voltage. In the event of the application of a negligible voltage,  $V_{ds}$ , the voltage drop is distributed uniformly along the entire length of the channel, resulting in the attainment of a channel resistance,  $R_{on}$ , as per the Equation 2.16 [4].

$$\sigma = q \,\mu_n \, n(x) \tag{2.15}$$

$$R_{\rm on} \approx \frac{1}{\mu_n C'_{ox}} \frac{L}{W \left( V_{GS} - V_{th} \right)} \tag{2.16}$$

In a more practical setting, MOSFETs in linear mode can be used as variable resistors controlled by the gate terminal. However, to ensure the stability of the device, it is imperative to maintain a constant voltage between the drain and the small source, thereby preventing the occurrence of saturation.

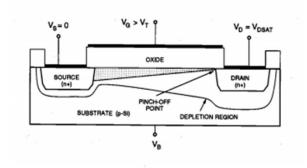

#### 2.2.3 Saturation Region

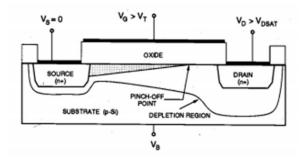

The final region of operation is the saturation region. The MOSFET device enters this region when the Equation 2.13 is no longer fulfilled. It can thus be concluded that, in the event of the MOSFET being in saturation, the channel will have moved away from the vicinity of the drain, as demonstrated in the accompanying figure 2.9. These conditions will be the ones with which we will engage in the following sections of this paper, dealing with nMOS and pMOS devices under saturation conditions.

Figure 2.9: Graphical scheme of the MOSFET Saturation region.

(Diego Mallada Morales. "Modelado y caracterización del transistor MOSFET: Extracción de parámetros". *University of Valladolid. Science Department.*)

Despite the reduction in channel length, it is understood that the current between the drain and the source does not vanish due to the free electrons departing the channel being attracted by the high voltage of the drain, thus traversing the depletion zone. This effect ensures that the voltage between the drain and the source remains practically constant. The reason for this is that if the voltage  $V_{ds}$  increases, the length of the channel decreases. This, in turn, results in an increase in the resistance and the force with which the electrons are attracted to the drain.

Therefore, in circumstances where the device is operating in saturation, the current flowing between the drain and the source is subject to control by the gate voltage. It is evident that, in the event of a fixed  $V_{ds}$  voltage and a fixed gate voltage, the current would be governed by a number of factors. These include the distance between the drain and the source, the width of the channel, the threshold voltage, the width of the oxide itself, the dielectric coefficient of the gate, and the mobility of the carriers in the device.

In a manner analogous to the linear operating region, within the saturation region the drain current is governed by the Equation 2.17 [3]. However, if the dependence of  $V_{ds}$  on the reduction of the effective channel length is to be incorporated into this relationship, the so-called channel-length modulation parameter,  $\lambda$ , can be included to form the Equation 2.18.

$$I_{D,\text{sat}} = \frac{1}{2} \mu_n C'_{\text{ox}} \frac{W}{L} (V_{GS} - V_{th})^2$$

(2.17)

$$I_D \approx I_{D,\text{sat}} \left[ 1 + \lambda V_{DS} \right] \tag{2.18}$$

In this paper, the focus is on the saturation conditions of short-channel devices, and it is argued that this focus enables the discovery of a number of additional effects on the behaviour of the devices.

#### 2.2.3.1 Drain-Induced Barrier Lowering

In the context of short-channel MOSFET devices operating in the saturation region, a range of effects must be taken into consideration, including, but not limited to, Drain-Induced Barrier Lowering (DIBL). This effect can be expressed as follows: an increase in the voltage between the drain and the source results in a decrease in the effective threshold voltage [7].

The phenomenon can be attributed to the fact that, in nanometric technologies, the distance between the drain and the source is excessively small. This results in the electric field generated in the vicinity of the drain affecting the source by reducing the potential barrier at the end of this, and consequently increasing the leakage current. This indicates that the electric field, when specified, exerts an influence on the source, thereby facilitating the flow of free electrons from the source to the drain, obviating the necessity for an increase in gate voltage.

Therefore, in compact models, the DIBL can be quantified by this slope, Equation 2.19.

$$DIBL = -\frac{\Delta V_{th}}{\Delta V_{DS}}$$

(2.19)

In a similar manner, the threshold voltage of short-channel devices is affected, necessitating the reformulation of its expression to yield the Equation 2.20.

$$V_{th}(V_{DS}) \approx V_{th0} - \text{DIBL} \cdot V_{DS}$$

(2.20)

In summary, short-channel MOSFETs operating in the saturation region are subject to the following adverse effects, which are a consequence of the DIBL effect. It can thus be concluded that the control previously exerted by the gate on the behaviour of the drain current is now being assumed by the voltage at the drain terminal itself. This has the effect of causing the sub-threshold swing to degrade and the leakage current to rise exponentially.

Consequently, there is a shift in the  $I_d - V_{gs}$  characteristic curve, moving it towards lower gate values.

A further deleterious effect is the reduction of the analogue gain, because the DIBL increases the value of the output conductance gds, which in turn reduces the intrinsic gain of the MOSFET device, in other words the transconductance of the device between the output conductance  $g_m/g_{ds}$ . This has been demonstrated to result in a deterioration in the performance of small-signal amplifiers.

Finally, it is important to note that there exist techniques capable of mitigating the impact of Drain-Induced Barrier Lowering in short-channel devices. The most straightforward solution to this problem would be to use devices with a longer channel length. However, if the utilization of short-channel devices is deemed advantageous due to the characteristics they offer, advanced architectures such as FinFET, FDSIO or SOI can be employed.

The capacity of architectures such as FinFETs to mitigate the effects of DIBL is attributable to their geometric design. FinFETs incorporate an 'envelope gate' that enhances the electrostatic control of the channel, thereby minimizing the impact of the electric field of the drain on the source, in comparison to alternative architectures. In a planar MOSFET, the gate only exerts influence in the upper region of the channel. This enables the drain field to pass underneath and affect the source potential barrier, as previously outlined.

However, in the case of a FinFET, the channel is formed by a very thin layer of silicon that the gate surrounds on up to three sides. This configuration is known as a multi-gate configuration. This novel approach entails the utilization of the gate field to regulate the potential across the entirety of the channel area. Consequently, the depletion zones in the vicinity of the drain are confined to that specific area, thereby precluding the possibility of extension towards the source [8].

Furthermore, in these devices, there is a reduction in both the channel thickness and the effective channel length. However, the latter is maintained at a relatively short, controlled distance, thereby ensuring that the drain and source remain electrostatically isolated from each other.

This effect therefore has important implications when it comes to short-channel devices, but effective solutions have also been found.

#### 2.2.3.2 Saturation Velocity

In the context of short-channel MOSFET devices operating in the saturation region, an additional effect that warrants consideration is the effect of saturation velocity.

The phenomenon under discussion can be traced back to the electric field that is generated in the channel when there is a significant voltage difference between the drain and the source. The electric field thus engenders a cessation of linear acceleration in the carriers within the channel, i.e. electrons in the case of nMOS and holes in the case of pMOS, resulting in the attainment of a limiting velocity. This limiting velocity is a material property of the channel and is denoted as the saturation velocity  $v_{sat}$ .

The critical electric field, denoted  $E_c$ , is the value of the electric field at which the velocity of the carriers is expressed by the following Equation 2.21 [4]. This relationship is linear, with a slope that corresponds to the mobility of the carriers in the channel.

$$V_d = \mu_o \cdot E \tag{2.21}$$

However, at values of the electric field that exceed a critical threshold, the collisions of the free carriers become exceedingly frequent. Consequently, they are unable to gain additional energy from the field, resulting in the cessation of their acceleration and the subsequent stagnation at the saturation velocity. As previously outlined, the saturation velocity may be expressed as by Equation 2.22, where  $E_c$  is defined as the critical electric field. This limitation in velocity signifies that the value of the drain current ceases to increase as the voltage between the gate and the source rises.

$$V_{sat} = \mu_o \cdot E_c \tag{2.22}$$

Therefore, in circumstances where the carriers are moving at saturation velocity, the drain current will be governed by the Equation 2.18.

$$I_{D,sat} \approx W C'_{ox} v_{sat} (V_{GS} - V_{th})$$

(2.23)

In the case of the ekv models, the creation of a parameter  $L_{sat}$ , has been observed. This is defined as the length of the channel at the saturation rate. This is given by the Equation 2.24 [9]. It is imperative to emphasize that the primary rationale for the necessity of this parameter is predicated on the scaling of  $\lambda_c$ , which is to be followed in accordance with the Equation 2.25 [9].

$$L_{sat} = \frac{2\,\mu_n \, U_t}{v_{sat}} \tag{2.24}$$

$$\lambda_c = \frac{L}{L_{cat}} \tag{2.25}$$

In order to adapt the value of the inversion coefficient to this situation, it is necessary to set  $\lambda_c$  as a function of the channel length at the saturation rate.

It is evident that the saturation speed regime exerts a significant influence on the transconductance of the MOSFET, as evidenced by the proximity of its value to attaining a certain degree of independence from the channel length. This assertion is substantiated by the Equation 2.26 [9].

$$g_{m,sat} \approx W C'_{ox} v_{sat}$$

(2.26)

Consequently, it can be posited that the saturation rate functions as a physical limit on both current and gain for these devices, compelling integrated circuits designers to meticulously evaluate the trade-off between channel length, carrier mobility and saturation rate, with a view to optimizing the device to the greatest extent possible and thereby maximizing performance.

#### 2.2.3.3 Hot Electrons Degradation

The final phenomenon for the saturation region that will be discussed is the degradation of hot carriers. In MOSFET devices, this phenomenon occurs when some electrons or holes, depending on the device type, acquire sufficient kinetic energy to overcome the potential barriers when exposed to strong electric fields.

The ability of these carriers to penetrate the dielectric of the gate oxide is dependent on their capacity to overcome the potential barriers that are in place. The effect of this phenomenon is detrimental to the standard operation of the MOSFET device, since the presence of hot carriers instigates substantial leakage currents and engenders a permanent alteration in the characteristics of the transistor.

The most significant effects of hot carrier degradation are threefold. Firstly, the gate threshold voltage is displaced. Secondly, the device's own transconductance is lost. Thirdly, and as mentioned above, the leakage current increases markedly.

As previously mentioned, it should be noted that the effect is exacerbated by decreasing the length of the gate. Technologies with a length of less than 100 nanometers are particularly impacted by this effect. In such conditions, it can be observed that the presence of elevator fields in the pinch-off region serves to enhance the generation of hot carriers. This, in turn, results in the voltage between the drain and the source becoming non-linear, thereby reducing the operational lifespan of the MOSFET.

This effect has prompted integrated circuit designers to explore methods for reducing the drain voltage, thereby preventing the formation of such substantial electric fields. In the field of semiconductor engineering, certain solutions have been proposed, including the design of slightly doped drainers and the utilization of architectures such as FinFET.

In order to measure the damage caused by this effect, certain tests can be performed to check the accelerated aging of the devices. The experimental setup involves the application of high voltage pulses, both  $V_{gs}$  and  $V_{ds}$ , and the subsequent measurement of the evolution of threshold voltage, transconductance and leakage current over time. The process of extraction enables the subsequent extraction of a series of parameters, which in turn facilitate the prediction of the device's lifetime. A comparison of these parameters with empirical model values is then possible.

In practice today, these devices are utilized in saturation mode when a stable drain current is required in analogue applications, such as current sources or linear regulators.

### 2.2.4 Breakdown Region

It is imperative to note that the breakdown operating region is an undesirable state to avoid entering. The primary characteristic of this phenomenon is that the voltage between the drain and the source  $V_{ds}$  exceeds a critical value. This results in the saturation region being left behind, and the MOSFET ceases to behave as a gate-controlled switch. Instead, it enters a state of punch-through.

Avalanche breakdown is characterized by the presence of a high density of free electrons, which, when interacting with silicon atoms, results in the generation of additional electron-hole pairs. This phenomenon can be likened to that of hot electrons, exhibiting a similar effect. It is evident that this process is characterized by an increase, resulting in a substantial rise in drain current, even in the absence of gate voltage. The voltage  $V_{ds}$  at which this occurs is contingent on the technology employed and is typically specified by the manufacturer, as this scenario can result in irreversible damage to the device. An illustration of this phenomenon is the generation of irreversible defects in the transistor material when the avalanche current overheats the oxide and silicon.

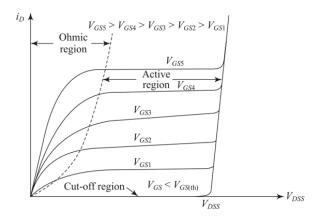

Figure 2.10: MOSFET Characteristic curve.

(S Rvivarman. "I-V Characteristics of Power MOSFET". https://sravivarman.com/technical-articles/i-v-characteristics-of-power-mosfet/)

Conversely, an examination of the characteristic curve, figure 2.10, of the MOSFET reveals the breakdown region with clarity, situated after the active or saturation region where the current remains constant. However, it is when the current reaches this operating zone that the drain current is suddenly triggered.

### 2.3 Second Order Effects of a MOSFET

As previously mentioned, MOSFETs have a number of operating regions, each with its own characteristics. The device's behaviour, the equations used to describe its characteristics, and its functionality can all vary from one region to another. However, in addition to understanding the operating regions, it is important to consider some effects that can alter the expected behaviour of MOSFETs.

We will now take a closer look at some of these effects, such as the subthreshold current effect, mobility variation and the body effect.

#### 2.3.1 Subthreshold Current Effect

To more accurately model a MOSFET device, it is important to consider the sub-threshold current. This unwanted diffusion current occurs when the device is in the cutoff region, where theoretically no current should be flowing through the device. This behaviour is particularly significant in nanometric MOSFETs because their small size exacerbates non-ideal effects such as sub-threshold currents.

This current originates when the voltage between the gate and the source is lower than the threshold voltage, or what is the same, when the device is in the cutoff region, as explained above. Under these conditions, no current should flow through the device because the channel has not yet formed. However, due to the high electron concentration gradient at the source and low gradient in the channel, a diffusion current appears, which is favored by the applied voltage  $V_{ds}$ .