### Universidad de Valladolid

### **FACULTAD DE CIENCIAS**

### TRABAJO FIN DE GRADO

**Grado en Física**

Estudio experimental de dispositivos de conmutación resistiva

Ana Sarmentero González Salvador Dueñas Carazo y Guillermo Vinuesa Sanz 2024 ÍNDICE ÍNDICE

## Índice

| 1. | Mot                                  | tivación                                                                       | 3          |

|----|--------------------------------------|--------------------------------------------------------------------------------|------------|

|    | 1.1.                                 | Las limitaciones de las memorias actuales basadas en la tecnología del silicio | 3          |

|    | 1.2.                                 | El memristor como cuarto elemento fundamental de los circuitos                 | 5          |

|    | 1.3.                                 | Las memorias RRAM como alternativa y su relación con el memristor              | 7          |

|    | 1.4.                                 | Aplicaciones en el ámbito de redes neuromórficas                               | 9          |

| 2. | Des                                  | arrollo teórico                                                                | <b>12</b>  |

|    | 2.1.                                 | El fenómeno de conmutación resistiva                                           | 12         |

|    | 2.2.                                 | El modelo filamentario                                                         | 14         |

|    | 2.3.                                 | Mapas de memoria                                                               | 17         |

|    | 2.4.                                 | Comportamiento transitorio                                                     | 18         |

| 3. | Pro                                  | ceso experimental                                                              | 20         |

|    | 3.1.                                 | Disposición experimental                                                       | 20         |

|    |                                      | 3.1.1. Dispositivos de conmutación resistiva caracterizados eléctricamente     | 20         |

|    |                                      | 3.1.2. Instrumentación                                                         | 21         |

|    |                                      | 3.1.3. Programas utilizados                                                    | 22         |

|    | 3.2.                                 | Técnicas de caracterización eléctrica                                          | 23         |

|    |                                      | 3.2.1. Curvas I-V                                                              | 23         |

|    |                                      | 3.2.2. Mapas de memoria o histerones                                           | 24         |

|    |                                      | 3.2.3. Comportamiento transitorio                                              | 25         |

| 4. | Resultados experimentales y análisis |                                                                                | <b>2</b> 6 |

|    | 4.1.                                 | Curvas I-V                                                                     | 26         |

|    | 4.2.                                 | Mapas de memoria                                                               | 27         |

|    | 4.3.                                 | Comportamiento transitorio                                                     | 31         |

|    | 4.4.                                 | Lazos de incremento y decremento                                               | 33         |

| 5  | Con                                  | clusiones                                                                      | 35         |

ÍNDICE

### Resumen y abstract

### Resumen

En este trabajo se realiza un estudio de memorias RRAM conocidas comúnmente como *memristores*. Para comprender la evolución y la importancia de dichas memorias emergentes se realiza un previo análisis del contexto histórico para estas memorias, del descubrimiento del *memristor* y de su relevancia en la actual era del silicio. Se trata de un trabajo experimental en el que se pretende estudiar y comprender el funcionamiento interno de estas memorias. Para ello se realizan medidas de las curvas I-V, mapas de memoria o *histerones* de su capacidad y conductancia y por último se estudia su comportamiento transitorio.

### Abstract

In this work, an experimental study of RRAM memories, commonly referred to as *mem-ristors*, is realized. To fully comprehend the development and significance of said emerging memories, first a historical context analysis is conducted as well as a review of the discovery of the *memristor* and its relevance in the actual silicon era. This experimental study aims to discern the internal workings of said memories. To achieve this, measurements of the I-V curves and memory maps or *hysterons* of their conductance and capacity were conducted. Finally, its transient response was studied.

ÍNDICE

### Introducción

En este trabajo de fin de grado se realizan diversas medidas con el fin de caracterizar eléctricamente las muestras metal-aislante-metal (MIM) dentro del marco de la conmutación resistiva.

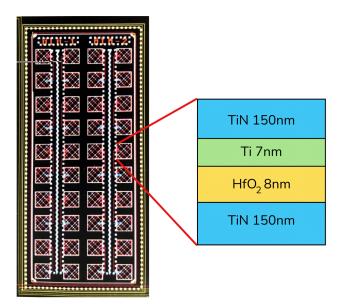

Las muestras estudiadas presentan la siguiente estructura interna: TiN-Ti-HfO<sub>2</sub>-TiN (8nm). Los dispositivos utilizados en este trabajo proceden de la colaboración entre Grupo de Caracterización de Materiales y Dispositivos Electrónicos (GCME), Grupo de Investigación Reconocido (GIR) de la Universidad de Valladolid con The Leibniz Institute for High Performance Microelectronics (IHP), en Alemania. Los resultados obtenidos y estudiados en este trabajo se deben a la realización de prácticas de empresa en el grupo de investigación GCME en el verano de 2022.

A lo largo de este trabajo se establecerá un fundamento teórico del fenómeno de conmutación resistiva a base de diversos modelos y posteriormente se presentarán las medidas realizadas junto con los resultados obtenidos. Para llevar acabo un estudio experimental completo se estudiarán los ciclos I-V y sus mapas de memoria, los mapas de memoria correspondientes a medidas de capacidad y conductancia y por último el comportamiento transitorio de los dispositivos.

La estructura de este trabajo es la siguiente:

- 1. Motivación: donde se exponen los motivos por los que el estudio de las memorias que presentan conmutación resistiva ha crecido tanto en los últimos años.

- 2. Desarrollo teórico: donde se analiza el origen de este fenómeno mediante modelos y se explica la base teórica de las diversas medidas que se realizan en el siguiente apartado.

- 3. Proceso experimental: en el que se detalla la estructura de las muestras y los procedimientos seguidos a la hora de realizar las medidas.

- 4. Resultados y análisis: en este apartado se presentan los resultados obtenidos y se analizan.

- 5. Conclusiones: donde finalmente se resumen los hallazgos y se realiza un análisis general del fenómeno de conmutación resistiva estudiado.

### 1. Motivación

### 1.1. Las limitaciones de las memorias actuales basadas en la tecnología del silicio

El desarrollo de la electrónica tal y como la conocemos hoy en día y de sus múltiples aplicaciones ha sido posible gracias a la invención del transistor, que fue capaz de superar las dificultades que se presentaban con las válvulas de vacío en la primera mitad del siglo XX. Los transistores desarrollados en 1947 por W. Shockley, J. Bardeen y W. Brattain resolvieron todos estos inconvenientes (entre los que se destacan el tamaño, el peso y su elevado consumo energético). Junto con el desarrollo de los circuitos integrados (CI), ambas tecnologías han sido clave para el progreso de los avances tecnológicos de los que disfrutamos actualmente.

Los transistores se basan en la conducción eléctrica de materiales semiconductores (como el silicio y el germanio, siendo este último el material que inicialmente fue más utilizado). El uso del silicio se generalizó a partir del año 1958, con el auge de los transistores y el desarrollo de la tecnología de circuitos integrados sobre obleas de silicio.

Los circuitos integrados incorporan en un solo dispositivo todos los componentes fundamentales para el funcionamiento de cualquier dispositivo electrónico, como transistores, resistencias, condensadores y diodos. Este desarrollo desembocó en un enorme avance en la capacidad de producción masiva de los CI, e impuso la estandarización de esta tecnología, lo que conllevaba mejoras en su fiabilidad y facilitaba la incorporación de mayor complejidad en el diseño de los circuitos.

Los CI se crearon inicialmente con tecnología TTL (*Transistor-Transistor Logic*), basada en el transistor bipolar, pero esta tecnología fue reemplazada por la tecnología CMOS (*Complementary Metal-Oxide-Semiconductor*), que se convirtió en el proceso estándar de fabricación de los transistores MOSFET y continúa siéndolo hasta hoy. Ya en 2011 el 99 % de los CI basados en semiconductores se construían con tecnología CMOS.

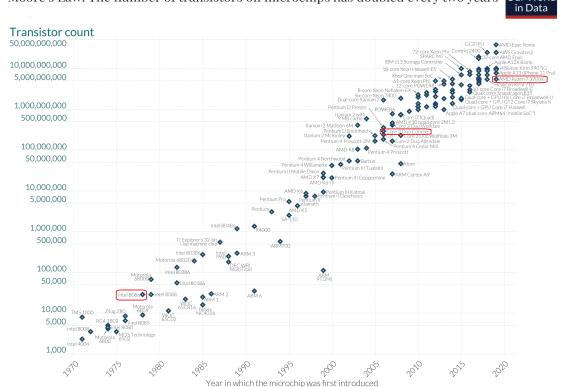

La descripción más común de la tecnología CMOS se basa en la Ley de Moore [1], formulada en 1965 por G. Moore, donde afirma que el número de transistores en el CI más complejo del momento duplicaría su valor cada año durante los próximos 10 años. En 1975 Moore observó cómo sus predicciones fueron correctas, pero propuso que en un futuro el número de transistores por CI duplicaría su valor cada dos años [2]. Podemos ver cómo esta tendencia se ha mantenido los últimos 40 años (ver Fig. 1).

La importancia de la Ley de Moore radica no en su robustez a lo largo de los años, si no en la causa y el efecto de esta tendencia. Una de las principales razones detrás de este desarrollo es la significativa reducción en el coste de los componentes dentro de un chip. Los avances en la industria han permitido disminuir drásticamente los costes de fabricación, impulsando el desarrollo de la tecnología del silicio. Lo más relevante es que la tasa de crecimiento en el número de componentes supera al aumento de coste por chip.

Aunque los avances de la electrónica que disfrutamos actualmente se deben a la tecnología del silicio, no todo son ventajas. La alta velocidad de procesamiento en los circuitos integrados se obtuvo en un principio disminuyendo el tamaño y la distancia entre los chips, de forma que una instrucción necesite menos tiempo para moverse físicamente de un componente a otro durante su ejecución. Hoy en día hemos alcanzado el límite en cuanto a tamaño y densidad de componentes [3], y para continuar con los avances en

este sector, ya no nos basta con mejorar el diseño o reducir el tamaño de los chips de silicio. A día de hoy, la implementación de estas técnicas para mejorar la velocidad de procesamiento han hecho que el procesador, también conocido como CPU, sea mucho más rápido de lo que era inicialmente.

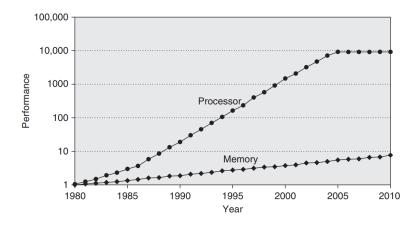

Sin embargo, no ha ocurrido lo mismo para las memorias, que no han mejorado su velocidad de acceso al mismo ritmo que los procesadores [4] (ver Fig. 2). A este problema se le conoce como "memory wall problem", término acuñado por primera vez por W. Wulf [5]. Debido a esto, el procesador debe esperar a que se acceda a la información almacenada en las memorias, lo que limita su velocidad. Para mitigar este problema, las CPUs tienen memorias SRAM que son mucho más rápidas que la memoria principal, aunque más caras también. Su función principal es almacenar información que ocupe poco y que se use frecuentemente y, de esta forma, aumentar la velocidad de funcionamiento del dispositivo. Esto conlleva a un mayor gasto en potencia, pues las SRAM deben estar constantemente conectadas a la corriente para poder almacenar esta información.

De todas formas, aunque la implementación de estos métodos ha mejorado la velocidad de funcionamiento de las CPUs, la latencia entre el procesador y la memoria persiste. Añadir memorias extra al dispositivo es una de las soluciones que se han implementado en estos años, pero aumenta la complejidad del diseño electrónico e incrementa su coste final. Una posible solución a este problema es la aplicación de tecnologías "in-memory computing", de la cual hablaremos más adelante.

**Figura 1:** Extraído de [6]. Número de transistores en microchips desde el año 1970 hasta 2020. Se puede apreciar claramente que que la Ley de Moore se mantiene estable.

La densidad de los transistores en un circuito ha aumentado de forma considerable en los últimos años [7]: actualmente, el GPU con el mayor número de transistores pertenece

a la compañía *Nvidia*, con 4nm de tamaño y con 208 billones de transistores. Integrar un número tan elevado de componentes en un mismo dispositivo supone un aumento en la complejidad del diseño, que alcanzará sus límites físicos si se sigue con la tendencia actual de la Ley de Moore. Al aumentar el número de transistores por dispositivo, también crece el consumo de energía y, por tanto, la disipación de calor, incrementando el peligro de que los transistores interfieran unos con otros.

Las corrientes fuga (o *leakage currents*) también se espera que sean un problema si se intenta reducir el tamaño de los chips de silicio por debajo de su límite en escalabilidad. Para la mayoría de dispositivos este límite suele estar en los 5nm.

Como ya se ha comentado anteriormente, las mejoras en memorias basadas en la tecnología del silicio han llegado a su límite y con los recientes avances en Inteligencia Artificial y *Big Data*, que requieren un elevado número de parámetros para poder efectuar operaciones complejas, sólo se puede esperar que en un futuro los problemas ya presentes incrementen. La industria necesita una nueva tecnología que sea capaz de asumir las necesidades del progreso actual.

Figura 2: Extraído de [4]. Tomando el rendimiento en 1980 como base, se presenta la brecha de rendimiento, medida como la diferencia entre el tiempo que necesita una acción de la memoria del procesador (para un único core) y la latencia de acceso a la memoria DRAM.

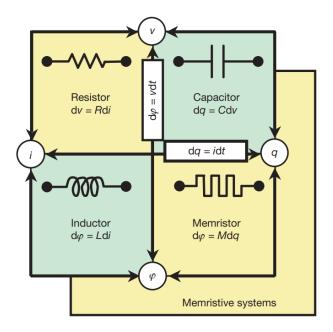

### 1.2. El memristor como cuarto elemento fundamental de los circuitos

Según la teoría de circuitos existen tres elementos pasivos básicos: la resistencia, R, la capacidad, C, y la inductancia, L. Cada elemento se define en términos de la relación entre dos de las cuatro variables fundamentales de los circuitos: la corriente, I, el voltaje, V, la carga, q, y el flujo,  $\phi$  (ver Fig. 3). La relación entre R, C y L con estos parámetros fundamentales puede describirse según las siguientes ecuaciones:

$$dv = Rdi (1)$$

$$dq = Cdv (2)$$

$$d\varphi = Ldi \tag{3}$$

Sin embargo, como se puede observar en las ecuaciones anteriores, faltaba un elemento que relacionase el flujo y la carga. Basándose en argumentos de simetría, Leon Chua presentó en 1971 su teoría, en la que afirmaba la existencia de un nuevo elemento, el memristor [8], un elemento que actuaría como una combinación entre una memoria y un resistencia (su nombre proviene de las palabras memory y resistor en inglés). La existencia de este elemento, el memristor, fue demostrada de forma experimental en 2008 por un grupo de los laboratorios Hewlett Packard (HP), liderado por Strukov [9].

Como se vio en el apartado anterior (ver Fig. 2) a finales de la década de los 2000, el problema descrito como *memory wall* se encontraba en su máximo histórico, y el descubrimiento experimental del memristor atrajo mucho interés, pues potencialmente esta tecnología podría permitir mejoras más allá de los límites de la tecnología CMOS.

**Figura 3:** Extraído de [9]. Elementos de circuitos elementales, incluyendo el memristor,  $\varphi$ , y las relaciones entre ellos.

De acuerdo a los argumentos de simetría expuestos por Leon Chua, el memristor debe satisfacer la siguiente relación:

$$d\varphi = M(q)dq \tag{4}$$

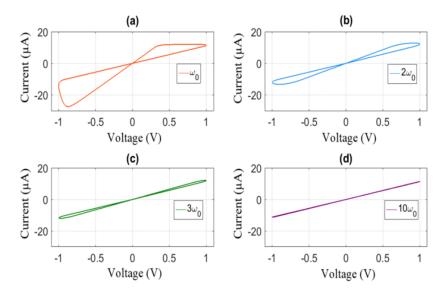

siendo M(q) la memristancia, medida en ohmios. Para los elementos lineales, donde M es constante, la memristancia es equivalente a la resistencia (Ec. 5). Por el contrario, si depende de la carga, como hemos supuesto en la Ecuación 4, tenemos un elemento del circuito que no se comporta de forma lineal como el resto. En este caso, al representar la curva I-V característica se obtiene una figura de Lissajous (ver Fig. 4).

$$M(q) = \frac{d\varphi}{dq} = \frac{d\varphi}{dt}\frac{dt}{dq} = \frac{v}{i} = R \tag{5}$$

Cabe destacar que ninguna combinación de componentes resistivos, capacitivos e inductivos da lugar a los mismos resultados obtenidos con un memristor no lineal [9].

**Figura 4:** Extraído de [10]. Ejemplos de varias curvas I-V de elementos memristivos basados en el modelo matemático desarrollado en [10], en las que se observa la variación de las figuras de Lissajous dependiendo de la frecuencia.

Las curvas representadas en la Figura 4 se conocen como "pinched hysteresis loops", debido a su forma, y son una característica fundamental de los memristores. El efecto de la memoria en los memristores está determinado por el área encerrada en las curvas, como veremos más adelante.

### 1.3. Las memorias RRAM como alternativa y su relación con el memristor

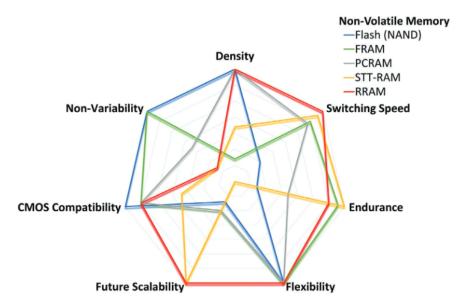

Las memorias no volátiles (NVM, non-volatile memories) se encuentran muy presentes en los dispositivos, sobre todo en aquellos portátiles, debido a su bajo consumo, su menor peso y su escalabilidad. Como se indicó previamente, continuar reduciendo el tamaño de estas memorias se ha convertido en un proceso cada vez más difícil. Las memorias FLASH son las NVM dominantes en el mercado actual, pero su funcionamiento depende del almacenamiento de carga, lo cual crea una serie de inconvenientes únicos a estas memorias al intentar reducir el tamaño de su capa de SiO2 por debajo de 1,5nm debido a los límites establecidos por el efecto túnel.

Actualmente, para mejorar el funcionamiento del sistema general, se combinan varias memorias, aumentando la complejidad del diseño y su coste final. Para solucionar este problema la industria busca nuevas memorias que cuenten con las mejores características posibles: la velocidad de las DRAM, que sean memorias no volátiles, que tengan un alto grado de escalabilidad y que su producción sea barata, o incluso que todas las operaciones se realicen en la propia memoria (conocido como "in-memory computing" [11]), entre otros. Rutas alternativas a las RAMs tradicionales se encuentran en proceso de investigación en estos momentos y podemos distinguir varios ejemplos de estas nuevas memorias como: PCRAM (phase-change RAM), ReRAM (Resistive RAM), F-RAM (Ferroelectric RAM) y MRAM (Magnetic RAM).

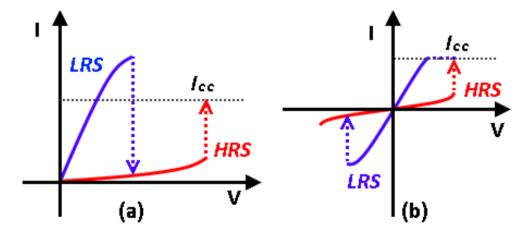

Nos centraremos en las memorias ReRAM, que son nanoestructuras MIM (Metal-Insulator-Metal) que presentan el fenómeno de conmutación resistiva (reisistive switching, RS) ante un estímulo eléctrico. El fenómeno de conmutación resistiva se basa en que estos dispositivos presentan variación entre dos estados de resistencia bien definidos, con una variación entre ellos de hasta 9 órdenes de magnitud. Estos estados son conocidos como LRS ("low resistance state") y HRS ("high resistance state") y las ReRAMS pueden alternar entre estos dos estados cuando se les aplica un impulso eléctrico. Otras ventajas notables de las ReRAMs es su compatibilidad con la tecnología CMOS, su estructura simple y su bajo coste de fabricación.

**Figura 5:** Extraído de [12]. Esquema comparativo entre las distintas características de memorias no volátiles (NVM) existentes y emergentes en el mercado.

El campo de los memristores y el de las memorias ReRAM tienen mucho en común, pero inicialmente las dos comunidades no se relacionaban entre sí. Es importante recordar que el memristor nació como idea completamente teórica [8], y no fue hasta que se publicó el primer memristor físico por el grupo de investigación de HP liderado por Strukov [9] que se comenzó a estudiar de forma experimental a mayor escala. El estudio de las memorias ReRAM comenzó de forma más experimental, centrándose en las propiedades de los diversos materiales para explicar los fenómenos observados. Durante un tiempo existió cierta controversia, pues se argumentaba que eran campos separados debido a que el tipo de materiales que se utilizaban en su fabricación eran distintos.

L. Chua argumentó que todas las memorias que presenten conmutación resistiva son memristores [13] y hoy en día ambos campos se entienden como uno solo. De forma generalizada, los científicos que estudian las memorias ReRAM utilizan la teoría de los memristores, y aquellos estudiando memristores se apoyan en estudios previos de las memorias ReRAM para explicar ciertas propiedades de los dispositivos.

Basándonos en las conclusiones de [13] definimos un memristor como cualquier dispositivo electrónico con 2 terminales que pueda presentar uno de dos valores posibles de resistencia (HRS y LRS) a lo largo de un periodo suficientemente largo de tiempo sin consumir potencia. Además, debe poder conmutar entre HRS y LRS al aplicar una co-

rriente muy pequeña (para no alterar su valor de resistencia). A esto se le conoce como una memoria no volátil que presenta commutación resistiva. Otra característica que debe cumplirse es que la curva del ciclo de histéresis disminuya según aumenta la frecuencia, en lo que ya conocemos como "pinched hysteresis loop", tal y como veíamos en la Figura 4.

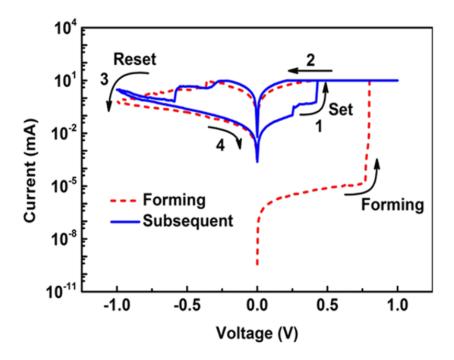

De momento, parece que las memorias ReRAM bipolares son los dispositivos más cercanos al memristor real (ver Fig. 6) y serán estos dispositivos los que estudiaremos.

Figura 6: Extraído de [14]. Curvas I-V típicas experimentales de ReRAM unipolar (a) y bipolar (b), y memristor teórico (c) y experimental (d). En (d) vemos un ejemplo de curva I-V de un memristor que conmuta del estado ON al OFF. Muchos memristores conmutan en sentido contrario, del estado OFF al ON, y veríamos que el sentido de la curva es el contrario al que se representa en la figura.

### 1.4. Aplicaciones en el ámbito de redes neuromórficas

La capacidad de computación de los ordenadores digitales basados en transistores con tecnología CMOS, ha crecido en las últimas décadas, sobre todo debido a que el número de transistores por componente ha aumentado tal y como predecía G. Moore (Sección 1.1 y 1.3). Sin embargo, la forma en la que los componentes de hardware están organizados en un ordenador, la conocida como arquitectura de von Neumann, prácticamente no ha variado desde su concepción en 1945. Esto es en parte debido a la gran ventaja que presenta, pues cientos de ingenieros pueden trabajar de forma independiente en la construcción de un sistema extremadamente complicado sin la necesidad de entender todos los componentes individuales que lo forman.

Con los avances actuales en Inteligencia Artificial, *Big Data* y el Internet de las Cosas (IoT), la cantidad de datos que queremos almacenar en un único dispositivo está creciendo de forma exponencial, lo que nos lleva, entre otros, al problema ya conocido de *memory wall*.

Diversos dispositivos electrónicos están surgiendo como alternativa a los transistores, aprovechándose de fenómenos como el spin, la transición de fase o el transporte de iones, a medida que tanto nuestro entendimiento de sus procesos físicos como los avances en la tecnología que nos permite crearlos aumentan. Entre todos ellos, el memristor se alza como un candidato muy prometedor.

El memristor presenta muchas ventajas, entre ellas una energía muy baja para su programación debido a las pequeñas dimensiones del dispositivo y una velocidad de conmutación muy rápida. En cuanto a la arquitectura de los dispositivos, ofrece también muchos beneficios, pues múltiples memristores pueden ser organizados en grandes arrays o apilados tridimensionalmente para formar circuitos más complejos.

Esto abre la puerta a la implementación de algoritmos utilizados en *deep learning*, que requieren un número de parámetros muy alto para realizar las operaciones basadas en redes neuronales y resultan muy costosos a nivel de recursos para los sistemas de computación digital tradicionales. Estas cualidades únicas hacen que los memristores sean una elección natural para formar redes neuronales, con un amplio rango de aplicaciones como procesamiento del lenguaje, reconocimiento de objetos, toma de decisiones, vehículos autónomos, robótica, medicina y finanzas, por nombrar algunos ejemplos.

Existen extensas simulaciones de estos dispositivos, pero las demostraciones experimentales no son tan amplias, debido al comportamiento no ideal de los dispositivos reales, que repercute sobre todo en la variabilidad muestra a muestra.

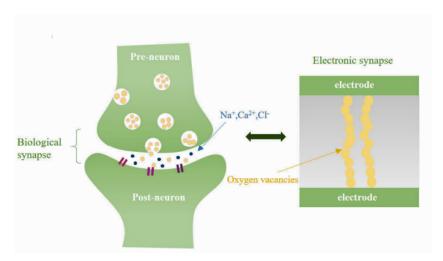

El diseño en computación basado en las sinapsis neuronales cerebrales se espera que cambie por completo la arquitectura tradicional y que nos lleve a una nueva generación de potencia computacional. El memristor, no solo presenta parámetros de funcionamiento óptimos, sino que además tiene un comportamiento natural muy similar a las sinapsis neuronales pues, debido a su curva de histéresis, sus estados internos dependen de la historia de la corriente o voltaje que han sido aplicados anteriormente. La variabilidad de resistencia del memristor exhibe muchas similitudes a los procesos de aprendizaje de las neuronas tal y como los conocemos hoy en día, y presenta la ventaja de que estos procesos pueden realizarse en un único memristor.

Para comprender mejor estas similitudes entre las neuronas y los memristores, presentamos un resumen de los procesos involucrados en la sinapsis neuronal y aquellos presentes en las memorias RRAM. La memoria humana se divide en dos tipos de procesos para el aprendizaje:

- STM (short-term memory)

- LTM (long-term memory)

De forma similar, el comportamiento sináptico en memorias RRAM se divide en:

- STP (short-term plasticity)

- LTP (long-term plasticity)

Se cree que LTP se relaciona con funciones de aprendizaje y memoria, mientras que STP se relaciona con la mejora a corto plazo de conectividad neuronal, durando unos

minutos o incluso menos. Por otro lado, LTP dura varias horas o incluso años [15]. Entre estos dos tipos de memoria, en los dispositivos electrónicos buscamos implementar STP, estableciendo nuevas relaciones a corto plazo y mejorando la velocidad de acceso a los datos almacenados, solucionando así los problemas generados debido a memory wall. STM es un fenómeno extraordinariamente similar a la conmutación resistiva, el principal mecanismo de funcionamiento de los memristores, el cual veremos a continuación. Se consigue así establecer un estado conductor inestable bajo ciertas condiciones de voltaje y recuperar el estado estable original tras un proceso de relajación, y dicho estado puede variar su valor dependiendo del estímulo inicial aplicado, al igual que la sinapsis neuronal. Este fenómeno resulta muy interesante para mejorar las conexiones existentes entre dispositivos y es un gran punto de partida hacia la posible evolución hacia sistemas más complejos.

Figura 7: Extraído de [15]. Comparación entre sinapsis biológicas y las sinapsis electrónicas de un memristor con un óxido metálico como aislante.

### 2. Desarrollo teórico

#### 2.1. El fenómeno de conmutación resistiva

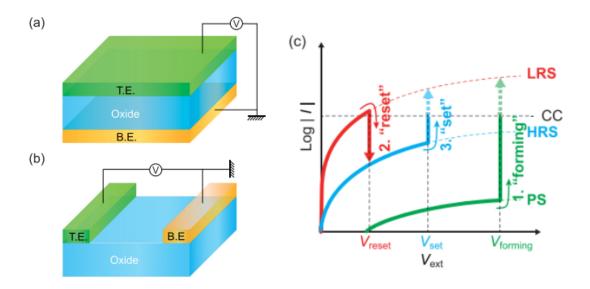

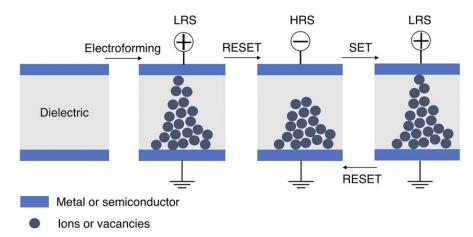

La conmutación resistiva se refiere al fenómeno físico en el que la resistencia de un material dieléctrico cambia como respuesta a la aplicación de un campo eléctrico externo. Se diferencia del fenómeno de la ruptura del dieléctrico, pues este último es permanente, mientras que la conmutación es reversible y puede repetirse. Típicamente, este cambio de resistencia es no volátil, es decir, que dicho estado se mantiene durante un largo periodo de tiempo tras retirar el campo eléctrico externo aplicado. Este fenómeno ocurre en diversos materiales (óxidos, nitrilos, semiconductores y materiales orgánicos pero ha sido investigado sobretodo en los óxidos metálicos, en cuyo estudio se centra este trabajo. Los dispositivos que presentan RS tienen una configuración similar a la de la Figura 8, con una capa de óxido fina entre dos terminales metálicas (estructura MIM o MIS). Un aislante óxido tendrá una resistencia bastante alta, pues su qap se encuentra en el rango de (1-5) eV comparado con la energía térmica a temperatura ambiente (unos 25meV). El proceso consiste en aplicar un voltaje inicial V<sub>forming</sub>, tras el cual el dispositivo entra en un estado de baja resistencia, llamado low-resistance state (LRS). Este proceso se conoce como electroforming o forming. Durante este proceso es importante restringir la corriente que circula por el dispositivo, mediante la compliance current, I<sub>CC</sub>, pues podría resultar en una ruptura completa del dieléctrico, dejando el dispositivo inutilizable. Tras el proceso de *electroforming*, la resistencia del dispositivo puede alternar entre estados de baja resistencia, LRS, y de alta resistencia, high-resistance state (HRS) mediante el voltaje aplicado. Distinguimos así dos procesos, el SET y el RESET:

- $\bullet$  El proceso del SET ocurre cuando la resistencia cambia de HRS a LRS tras aplicar el correspondiente voltaje de SET,  $V_{SET}$ , que será siempre menor que  $V_{forming}$ .

- $\bullet$  El proceso de RESET ocurre cuando la resistencia pasa del estado LRS a HRS,  $V_{\rm RESET}.$

Se puede alternar entre estos estados de forma cíclica, formando el ciclo de curvas I-V característico de los dispositivos con conmutación resistiva (ver Fig. 8). Siguiendo el esquema propuesto en la Figura 8, describimos los pasos de la conmutación resistiva: Primero ocurre el proceso de forming (1), donde se le aplica un alto voltaje a una muestra y el dispositivo pasa a un estado inicial LRS. El dispositivo cambia del estado LRS a HRS al aplicar un  $V_{\rm RESET}$  (2). Se puede volver a cambiar del estado HRS al LRS mediante  $V_{\rm SET}$  (3) y podemos alternar entre ambos estados (2-3). Las siglas "PS" que aparecen en la curva de forming se refieren a "Pristine State", es decir, corresponde a la curva del dispositivo en estado virgen, cuando aun no se ha hecho el forming.

**Figura 8:** Extraído de [16]. Esquema de un montaje típico de estructuras MIM o MIS que presentan RS: en estructuras vertical (a) y plana (b). En (c) se observan las curvas I-V esquemáticas del proceso RS.

Existe una clasificación de la conmutación resistiva dependiendo de la polaridad de los voltajes aplicados: para los casos en los que siempre se aplica la misma polaridad (o positiva o negativa) el dispositivo se llama "unipolar"; en el caso contrario, donde la polaridad varía para el proceso de SET y RESET el dispositivo es "bipolar" (ver Fig. 9). Se ha observado que las distintas polaridades dependen del material [16]. En este estudio se estudiarán muestras de HfO<sub>2</sub>, que presentan un comportamiento bipolar.

**Figura 9:** Extraído de [17]. Esquema de curvas I-V para memorias unipolares (a) y bipolares (b). El esquema (b) corresponde a una figura bipolar con forma de 8 (figure-of-eight, F8). Si el SET y RESET ocurrieran a polaridades de signo opuesto, el sentido de la curva sería el contrario, correspondería a una cF8 (counter-figure-of-eight).

### 2.2. El modelo filamentario

El modelo filamentario se basa en la formación de filamentos conductores en el medio aislante de las estructuras MIM como respuesta a un estímulo eléctrico externo. Estos filamentos modifican las propiedades conductoras del medio aislante, lo que explica el fenómeno de conmutación resistiva que se describía anteriormente. Los canales propician la conducción entre ambos electrodos y permiten que el dispositivo alterne entre los dos estados LRS y HRS dependiendo del nivel de formación de los filamentos en el medio aislante [16].

Este proceso conlleva varias etapas. La primera se trata del "electroforming" en el que aplicamos un alto voltaje que forma un filamento conductor inicial que une ambos electrodos. Tras aplicar este voltaje, el dispositivo se encuentra en un estado de baja resistencia LRS. Después se aplica un voltaje de RESET,  $V_{RESET}$ , de distinta polaridad al  $V_{SET}$  para los dispositivos bipolares, que se traduce en la disolución parcial del filamento conductor, lo que conlleva un aumento de la resistencia del medio aislante, es decir, hemos pasado al estado HRS. Podemos repetir este ciclo aplicando de nuevo un voltaje lo suficientemente intenso,  $V_{SET}$ . Así, volvemos a formar el filamento parcialmente disuelto y el dispositivo vuelve a pasar al estado LRS mediante el proceso de SET.

El proceso de formación del filamento puede realizarse mediante diversos mecanismos dependiendo del material que utilicemos como aislante. Nos centraremos en RS mediante vacantes de oxígeno (ver Fig. 10), con  $HfO_2$  como aislante, que es uno de los materiales más prometedores como aislante en la estructura MIM del memristor [18].

Es importante destacar que el valor del voltaje inicial aplicado a la muestra,  $V_{forming}$ , es considerablemente mayor que el  $V_{SET}$  utilizado posteriormente. Esto es debido a que el voltaje aplicado en el electroforming es el que crea el canal conductor. El voltaje aplicado en el proceso de SET solamente se aplica para la formación parcial de un canal formado previamente, lo que necesita un voltaje menor. El proceso de electroforming es por tanto irreversible, ya que el dispositivo no volverá a necesitar un valor tan alto de voltaje aplicado.

Figura 10: Extraído de [19]. Esquema del fenómeno de RS en un dispositivo bipolar. Primero se realiza el proceso de electroforming en el material dieléctrico, después el dispositivo pasa al estado de resistencia LRS, donde el filamento está formado al completo. A continuación se produce el proceso de RESET en el que se disuelve parcialmente el filamento y el dispositivo pasa al estado HRS. Por último, mediante el SET se vuelve al estado LRS y así continúa el ciclo.

Podemos modelizar la creación del filamento de diversas maneras. A continuación se presenta un resumen del modelo desarrollado en [20].

Este modelo nos permitirá entender los parámetros en juego. Podemos definir  $V_A$  como la caída de voltaje interno del memristor y  $\Delta V_A$  como la caída de voltaje en el filamento conductor. Definiendo también  $\rho_{OFF}$  como la resistividad del material aislante, A el área del dispositivo, l(t) es la longitud del filamento conductor y d la distancia entre TE y BE. Así podemos escribir la corriente que pasa por el dispositivo como:

$$i = \frac{V_A - \Delta V_A}{\rho_{OFF} \frac{d - l(t)}{A}} \tag{6}$$

Donde se han tomado longitudes de dispositivo típicas (>50nm) y se han despreciado efectos parásitos [20].

Podemos definir  $d_{eff}(t) = d - l(t)$ , como la distancia efectiva que separa ambos electrodos en un tiempo determinado t. Y desarrollando, se puede llegar a la relación entre la caída del voltaje interno y el voltaje aplicado, que es:

$$V_A = \frac{\frac{d_{eff}(t)}{k_2}}{1 + \frac{d_{eff}(t)}{k_2} - \frac{d - d_{eff}(t)}{k_1 d_{eff}(t) + d - d_{eff}(t)}} V_{APPL}$$

(7)

Donde los parámetros  $k_1$  y  $k_2$  se refieren a las relaciones de resistividad del material dieléctrico y la base de los electrodos, respectivamente. Otra relación interesante es la tasa de ruptura del filamento conductor, que se puede escribir como:

$$\frac{d\left(d_{eff}\left(t\right)\right)}{d\left(t\right)} = \mu_{ON} \frac{V_A - \Delta V_A\left(t\right)}{d_{eff}\left(t\right)} \tag{8}$$

Siendo  $\mu_{ON}$  la movilidad de los iones que crean los filamentos conductores.

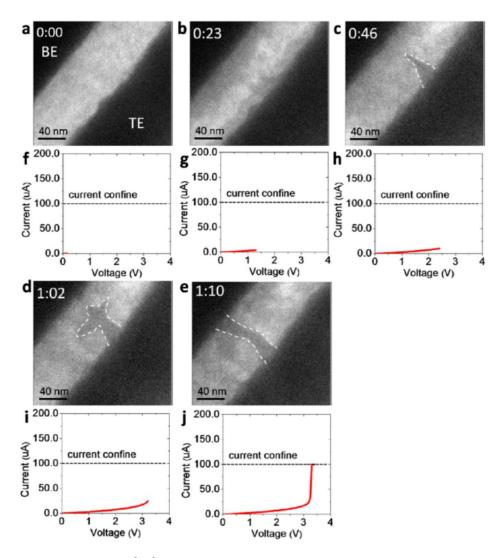

El modelo filamentario no es simplemente un modelo teórico, ha sido observado experimentalmente mediante diversas técnicas, entre las que se destaca la Microscopía Electrónica de Transición, TEM [21], como vemos en la Figura 11.

Una vez observada la formación del filamento conductor, para comprender el funcionamiento de los dispositivos RRAM, debemos estudiar los diferentes mecanismos de RS para estos dispositivos. La línea de investigación actual más reconocida es el modelo filamentario, aunque aun no existen explicaciones a diversos problemas relativos a la composición química y morfología del filamento, que influyen muy significativamente en el comportamiento de los dispositivos RRAM. Nos centraremos en tres mecanismos relacionados con la migración de cationes/aniones.

Figura 11: Extraído de [21]. Serie de imágenes TEM con sus correspondientes curvas I-V características ((f)-(j)) durante el proceso de forming. Puede observarse la evolución dinámica del CF ((a)-(e)). A medida que aumenta el voltaje, el CF crece de una forma cónica ((a)-(c)) hasta una forma dendrítica (d) y después pasa a una forma cilíndrica tras conectar los dos electrodos (e).

Estos serán: mecanismo termo-químico (TCM), mecanismo por cambio de valencia (VCM) y metalización electroquímica (ECM)

• Mecanismo termo-químico (TCM): este modelo puede aplicarse para explicar la formación y ruptura del CF en el caso de migración de iones de oxígeno o iones metálicos. Esta migración ocurre por el efecto Joule: el gradiente térmico es tan elevado que provoca que los iones de oxígeno se desplacen hacia el exterior de la zona filamentaria. Esta termodifusión provoca un cambio estequiométrico, haciendo que aparezca otro óxido del mismo material con una mayor conductividad, que será el que formará el filamento conductor. En el proceso de RESET, el filamento desaparece debido al efecto Joule. Al no limitarse la corriente en el RESET, la temperatura se eleva y provoca que el filamento se disuelva.

- Mecanismo por cambio de valencia (VCM): en un memristor de tipo VCM, el estudiado en este trabajo, el material aislante suele ser un óxido metálico (HfO<sub>2</sub> en nuestro caso). Este material es generalmente un mal conductor pero al aplicar un campo eléctrico, los átomos de oxígeno pueden migrar dentro del material, dejando tras de sí vacancias de oxígeno. Estas vacancias actúan como puntos de concentración de carga positiva, facilitando la conductividad a través de dicho canal y permitiendo que se produzca el proceso de SET. Al aplicar un voltaje de polaridad contraria, el campo eléctrico induce el movimiento de los iones de oxígeno en la dirección opuesta o provoca su recombinación, lo que disuelve parcialmente el filamento.

- Metalización electroquímica (ECM): en este mecanismo el TE puede ser ionizado y así los cationes metálicos se difunden a través del dieléctrico hacia el BE (inerte, conectado a tierra). De momento sólo se conocen tres metales que presenten este fenómeno cuando se utilizan como TE: Ag, Cu y Ni. En este proceso de desplazamiento se crea el CF. Al aplicar un voltaje de polaridad contraria, los iones metálicos recorren el camino contrario, deshaciendo el CF formado.

### 2.3. Mapas de memoria

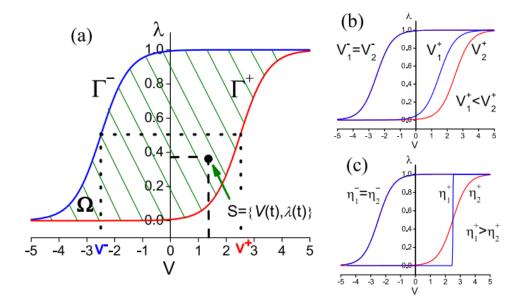

Un modelo para estudiar las memorias resistivas es son los mapas de memoria [22, 23], también conocidos como histerones, que nos permite representar la relación entre el voltaje y la conductancia, G, o la capacidad, C. Según el modelo de Chua [8], el modelo filamentario está formado por dos ecuaciones: una para el transporte de portadores de carga por el canal y otra ecuación que determina el estado de memoria del dispositivo. Para modelar este comportamiento memristivo se utilizan funciones de cresta dadas por:

$$\Gamma^{+}(V) = \left\{1 + e^{-\eta^{+}(V - V^{+})}\right\}^{-1} \tag{9}$$

$$\Gamma^{-}(V) = \left\{ 1 + e^{-\eta^{-}(V - V^{-})} \right\}^{-1} \tag{10}$$

Donde  $\eta^+$  y  $\eta^-$  son las tasas de transición entre el SET y el RESET (lo rápido que se realizan estos procesos) mientras que  $V^+$  y  $V^-$  son los voltajes umbrales para estos procesos, respectivamente. Físicamente, las funciones  $\Gamma^+$  y  $\Gamma^-$  son la agregación y disolución de los filamentos conductores durante los procesos de SET y RESET.

Modelándolo de esta manera, podemos representar los mapas de memoria: en la Figura 12 se observa cómo en el eje de ordenadas hemos representado  $\lambda$ , que es un parámetro de control con valores desde 0 (HRS) hasta 1 (LRS).

**Figura 12:** Extraído de [22]. (a) Modelo de histerones con funciones  $\Gamma^+$  y  $\Gamma^-$ , donde  $\omega$  es el conjunto de posibles estados. En (b) y (c) podemos ver los efectos de las funciones  $V^+$  y  $\eta^+$  sobre  $\Gamma^+$  respectivamente.

### 2.4. Comportamiento transitorio

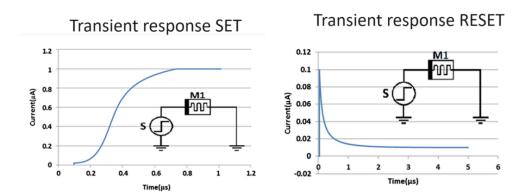

El comportamiento transitorio mide el comportamiento de un sistema cuando se ajusta a un nuevo cambio. Abarca desde el periodo inicial de ajuste hasta que el sistema se encuentra de nuevo en un estado de equilibrio. Durante un transitorio el comportamiento del memristor es inestable, hasta que alcanza un nuevo estado de equilibrio (LRS o HRS). Se utiliza en el estudio de memristores para valorar la respuesta del dispositivo durante el SET y RESET. Esto nos permite entender mejor su respuesta temporal, que es un elemento crucial en el estudio de redes neuronales de impulsos (SNN, Spiking Neural Networks), que son un modelo de redes neuronales muy realistas capaces de procesar información de una forma más similar a las redes neuronales biológicas debido a la inclusión del tiempo en su modelaje [24, 25].

En los transitorios estudiaremos el tiempo de conmutación, es decir, el tiempo en el que el memristor cambia de un estado de resistencia a otro (durante los procesos de SET o RESET) y la estabilización del estado de resistencia del memristor después de aplicar un voltaje o corriente.

Las curvas típicas que podemos esperar medir en este proceso se muestran en la Figura 13.

Figura 13: Extraído de [24]. Respuesta transitoria de corriente frente al tiempo modelada según lo desarrollado en [24] con una resistencia de  $R=50M\Omega$  y un voltaje desde 0V a 1V para el proceso de SET, y un voltaje desde 0V a -1V para el proceso de RESET.

Podemos observar la forma característica de un proceso de SET abrupto y un RESET gradual de los dispositivos basados en VCM. Durante el proceso de SET, el aumento de corriente induce un incremento de temperatura en el filamento debido al calentamiento por efecto Joule. Este aumento térmico facilita el proceso de creación de iones de oxígeno y acelera su migración hacia el filamento conductor (CF). Como resultado, el flujo de iones disminuye la resistencia del filamento, favoreciendo así la formación de un estado conductor. Por el contrario, en el proceso de RESET ocurre lo contrario: la disminución de la corriente reduce la temperatura del CF, lo que frena el proceso de RESET.

### 3. Proceso experimental

### 3.1. Disposición experimental

En este apartado se describen las características principales de las muestras estudiadas y se explican los instrumentos y programas empleados para realizar las medidas de caracterización correspondientes.

### 3.1.1. Dispositivos de conmutación resistiva caracterizados eléctricamente

Las muestras medidas provienen de IHP, Alemania, y fueron recibidas en Junio de 2021. Los dispositivos presentan una estructura MIM, donde las capas metálicas son de nitruro de titanio (TiN) y la capa aislante es de óxido de hafnio (HfO<sub>2</sub>) con una longitud de 8nm. Estas muestras cuentan también con una capa de transición de titanio (Ti) entre el TE y el material aislante, como puede verse en la Figura 14.

**Figura 14:** Fotografía de las placas medidas (izquierda), con un esquema de la sección transversal de la estructura interna de las muestras de TiN-Ti-HfO<sub>2</sub>-TiN (8nm) medidas (derecha). El área total de los dispositivos es de 600nm X 600nm.

El TiN se utiliza como conductor barrera entre el dispositivo activo y los contactos de metal utilizados para que pueda pasar corriente por el dispositivo. La capa de Ti ofrece una mayor estabilidad estructural para el filamento conductor, ya que el titanio se oxida con facilidad, generando una zona densa en vacantes de oxígeno en la interfaz entre el metal del TE y el  $HfO_2$ .

El TiN se utiliza como una barrera de difusión, evitando la difusión del metal en el medio aislante. Se trata de un material que se utiliza en aplicaciones bioelectrónicas, como implantes inteligentes o biosensores, debido a su capacidad para resistir la corrosión causada por el fluido corporal.

Las muestras estudiadas han sido creadas utilizando dos técnicas: Atomic Layer Deposition (deposición de capas atómicas, ALD) y magnetron sputtering. Se utiliza la técnica de ALD para controlar el grosor de la capa del dieléctrico. Dicha técnica se basa en exponer

al sustrato a una secuencia alterna de reactivos en fase de vapor. Por otro lado, aunque el magnetron sputtering se trata de otra técnica basada en la deposición de elementos en fase de vapor, esta técnica utiliza el confinamiento de energía electromagnética en una cavidad resonante, el magnetrón. Esta técnica es la utilizada para depositar el Ti, el material del TE.

Las muestras utilizadas en este trabajo proceden de las colaboraciones del *Grupo de Caracterización de Materiales y Dispositivos Electrónicos (GCME)*, *Grupo de Investigación Reconocido (GIR)* de la Universidad de Valladolid con *The Leibniz Institute for High Performance Microelectronics (IHP)*, en Alemania. Todas las muestras presentan conmutación resistiva bipolar basado en el VCM, donde los filamentos conductores se forman debido a las vacantes de oxígeno presentes en el medio aislante.

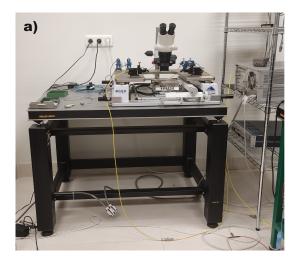

#### 3.1.2. Instrumentación

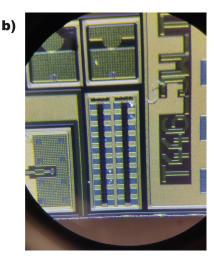

Para la obtención de las curva I-V, las medidas de histerones y los transitorios, se utiliza una mesa de puntas  $Cascade\ Microtech\ (Fig.\ 15)$ . Se trata de una mesa con un microscopio integrado que permite observar las placas de muestras y aplicar el impulso eléctrico necesario para su funcionamiento. La mesa cuenta con dos puntas de tungsteno, una se conectará a la placa metálica inferior conectada a tierra, en lo que conocemos como el BE (Bottom Electrode) y la otra será la que aplique la señal eléctrica correspondiente a la muestra, el TE (Top Electrode). Es un trabajo muy preciso, pues se debe tener cuidado de no rayar las muestras con las puntas, que tienen un tamaño del orden de  $\mu m^2$ .

**Figura 15:** La imagen (a) muestra la mesa de puntas con el microscopio integrado. La imagen (b) muestra uno de los chips estudiados bajo microscopio.

La señal eléctrica aplicada es generada en un analizador de semiconductores *Hewlett Packard 4155B Semiconductor Parameter Analyzer* que se controla en remoto mediante el programa de ordenador *Agilent VEE*. Los equipos y el ordenador están conectados gracias a una interfaz GPIB.

Figura 16: Analizador de semiconductores Hewlett Packard 4155B Semiconductor Parameter Analyzer utilizado en la caracterización de las muestras.

Antes de realizar las medidas de las muestras en la mesa de puntas, se cortocircuitan los BE de todas las muestras de la placa con una lámina de cobre. Así, una de las puntas de tungsteno hará contacto con esta lámina de cobre, conectada a tierra. Para realizar esta conexión se aplica una laca de plata, un material muy conductor, sobre la lámina de cobre rayada previamente, para permitir que la laca se adhiera mejor. Así, se evita que las resistencias en serie puedan afectar a nuestras medidas.

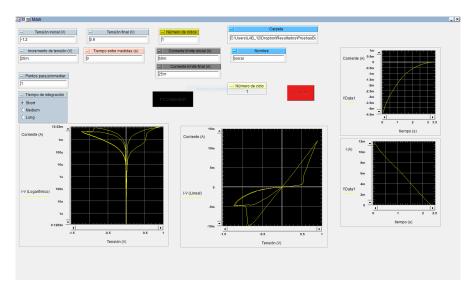

#### 3.1.3. Programas utilizados

En todas las caracterizaciones realizadas se utilizan diversos programas desarrollados en el *Grupo de Caracterización de Materiales y Dispositivos Electrónicos (GCME)* para facilitar las medidas correspondientes a través del programa *Keysight VEE*.

Figura 17: Captura de pantalla del programa de software utilizado en la medición de las muestras estudiadas. En la captura podemos ver un primer conjunto de cuadros en los que se pueden ajustar los valores de trabajo para voltaje, corriente, el paso para voltaje y corriente respectivamente y el número de ciclos. El programa presenta en la parte inferior dos gráficas donde se observa la evolución de los ciclos I-V en dos representaciones diferentes.

Este software nos permite configurar la señal aplicada sobre la muestra con múltiples valores: amplitud de la señal, número de ciclos aplicados, el paso de tensión, la velocidad de medida y la current compliance  $(I_{CC})$ . Para la medición de cada técnica de caracterización (curvas I-V, mapas de memoria y comportamiento transitorio) se utiliza un programa auxiliar distinto que permite ajustar los parámetros necesarios para cada tipo de medida, que veremos en más detalle a continuación.

#### 3.2. Técnicas de caracterización eléctrica

#### 3.2.1. Curvas I-V

El primer paso para poder realizar las medidas de las curvas I-V se trata del electro-forming, tras el cual las muestras presentan commutación resistiva en forma de pinched hysteresis loop, como se vio en la Sección 1.2. Para tensiones negativas crecientes (en módulo) ocurre el proceso de RESET, donde se pasa del estado LRS a HRS, y después la tensión aplicada pasa a ser positiva y se produce el proceso de SET al pasar del estado HRS a LRS.

**Figura 18:** Extraído de [26]. Esquema representativo de las curvas I-V, donde se explica el paso de LRS a HRS mediante los procesos de SET y RESET además del proceso de forming.

En las curvas I-V representamos el voltaje frente a la corriente aplicada aunque en ocasiones, como veremos en la Sección 4, estas curvas suelen representarse en escala logarítmica. Esta representación se utiliza para analizar más fácilmente las diferencias entre los procesos de SET y RESET.

### 3.2.2. Mapas de memoria o histerones

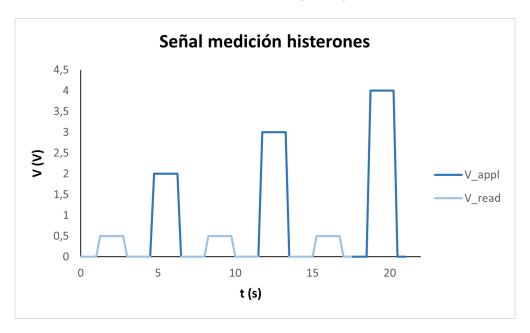

Para realizar las medidas de los mapas de memoria, debemos aplicar dos voltajes, el primero será la señal de voltaje aplicado para observar el fenómeno de conmutación resistiva,  $V_{APPL}$ , esta señal va barriendo todos los valores de voltaje para medir la respuesta I-V. La segunda señal se trata de un voltaje de lectura,  $V_{READ}$ , de valor constante y mucho menor que  $V_{APPL}$ . De esta forma medimos en qué estado se encuentra el dispositivo sin alterar su estado de resistencia (ver 19).

**Figura 19:** Extraída de [27]. Señal de voltaje aplicada a lo largo del tiempo para realizar las medidas de los histerones, diferenciando claramente entre  $V_{APPL}$  y  $V_{READ}$ . Análogamente para la señal negativa aplicada en las medidas.

En la sección 2.3 se presentaron los mapas de memoria normalizados, con la variable  $\lambda$  representada en el eje de ordenadas. Sin embargo, esta disposición no es la única posible, ya que también podemos representar la capacidad, C, o la conductancia, G, en el eje vertical. De este modo, podemos observar claramente las distintas características de las muestras medidas.

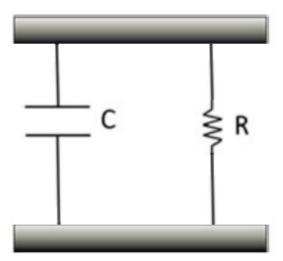

La conductancia se define como la parte real de la admitancia, Y, que es el inverso de la impedancia, Z. Para calcular la impedancia del memristor, presentamos el siguiente modelo de la Figura 20, con un condensador en paralelo con una resistencia.

**Figura 20:** Circuito equivalente de un memristor utilizado para calcular su impedancia. Consiste en una capacidad C en paralelo con una resistencia R.

Es importante resaltar que se trata de una aproximación para poder calcular la conductancia, y utilizar este modelo de circuito para el memristor, no refleja que este se comporte como un circuito RC. Tal y como se mencionaba en la sección 1.2, no existe ninguna combinación de componentes (resistivos, capacitivos o inductivos) que den lugar al mismo comportamiento observado y esperado de un memristor [9].

#### 3.2.3. Comportamiento transitorio

Se medirá la intensidad de corriente en función del tiempo para observar cómo varía la respuesta en corriente a lo largo del tiempo al aplicar un estímulo eléctrico. Se observará la respuesta inicial del memristor, que dependerá de su estado de resistencia. Así distinguiremos entre los transitorios de SET y de RESET. También observaremos su evolución temporal, cómo la resistencia del memristor varía debido al voltaje aplicado, y si presenta algún comportamiento no lineal, que podría reflejar alguna característica interna del memristor. Por último se estudiará también la estabilización del memristor una vez el estímulo eléctrico aplicado finaliza.

Los resultados que podemos esperar de este método de caracterización corresponden a la Figura 13 de la Sección 2.4.

# 4. Resultados experimentales y análisis

#### 4.1. Curvas I-V

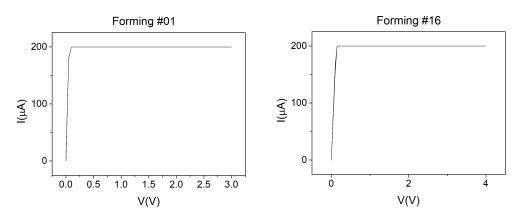

El primer paso para realizar todas las medidas se trata del electroforming. Se aplica un voltaje desde 0V a 3-4V, dependiendo de la muestra, y una corriente límite de  $200\mu A$ . Este proceso rompe el medio aislante en la estructura MIM, cambiando su estructura interna, y nos permite preparar la muestra para analizar su conmutación resistiva. En la Figura 21 se presentan las curvas correspondientes a este proceso para dos de los chips estudiados. En el resto de chips no se observa ninguna variación en el comportamiento. Para las muestras que aparecen en la Figura 21 podemos ver que el electroforming se produce bastante rápido, alcanzando el estado de LRS a un voltaje de 0,25V o menos. Se observa una alta uniformidad en todas las muestras estudiadas y también podemos observar que el proceso de electroforming se realiza sin pasos intermedios.

**Figura 21:** Electroforming realizado para las muestras  $n^0$ 1 y  $n^0$ 16. La corriente límite es de  $200\mu A$  y se aplica un voltaje desde 0V hasta 3-4V, dependiendo de la muestra. Se observa que el electroforming ocurre de media a 0,25V, con variaciones muy pequeñas muestra a muestra.

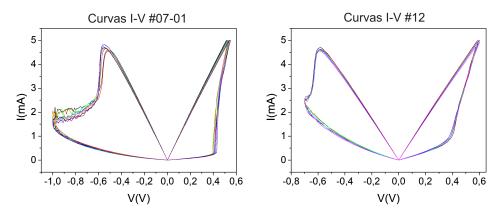

Una vez realizado el forming podemos pasar a medir los ciclos I-V. Después del electroforming se ha creado el filamento conductor y la muestra se encuentra en el estado LRS, que es donde comienza el ciclo. Se representan los ciclos I-V en escala logarítmica y la corriente en valor absoluto por comodidad, a diferencia de lo que se mostraba en la Figura 9. Cada ciclo completado por la muestra aparece en la Figura 22 con un color distinto y para estas medidas se han utilizado los siguientes valores límite de corriente:  $I_{limiteSET} = 5mA$  y  $I_{limiteRESET} = 10mA$  en valor absoluto.

En estas medidas se observa una mayor variabilidad muestra a muestra. Las muestras más estables tienen un voltaje umbral de SET de  $V_{umbralSET}=0,45V$  de media y un voltaje umbral de RESET de  $V_{umbralRESET}=-0,8V$  como podemos ver en la Figura 22. Se puede observar que los ciclos son bastante simétricos en una misma muestra, aunque existe una mayor variabilidad en el proceso de RESET que en el SET. De nuevo, para las muestras más estables la corriente de conducción es muy simétrica y para ambos procesos tiene un valor de  $I_{conduccion}=5mA$ .

**Figura 22:** Ejemplo de ciclos I-V para los chips  $n^{o}$ 7 y  $n^{o}$ 12. En estas medidas se han aplicado los siguientes valores de corriente límite para cada proceso:  $I_{limiteSET} = 5mA$  y  $I_{limiteRESET} = 10mA$ .

Se puede observar cómo el proceso de SET se produce de forma más abrupta y cómo el proceso de RESET ocurre de forma más gradual. Esto es debido al aumento de la resistencia que ocurre en el RESET, que ralentiza el proceso al competir con el aumento de voltaje en valor absoluto.

Los chips de la Figura 22 presentan unos valores de funcionamiento muy similares. Aunque sus curvas I-V no son exactamente iguales, diferenciándose en particular en el proceso de RESET donde el filamento se destruye parcialmente, lo que es indicativo de la variabilidad muestra a muestra.

### 4.2. Mapas de memoria

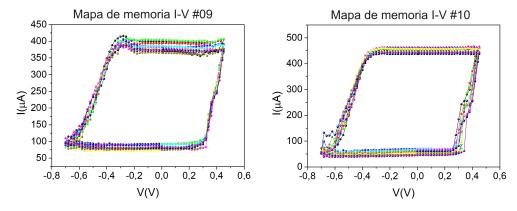

A continuación vamos a estudiar la estabilidad de los estados LRS y HRS en las curvas I-V. Para realizar estas medidas se aplica la señal que vimos en la Figura 19: se realizan los ciclos de forma habitual con  $V_{APPL}$  y en estos mapas de memoria se representa la corriente frente a  $V_{READ}$ , que determina el estado de resistencia en el que se encuentra el dispositivo.

**Figura 23:** Ejemplo de mapas de memoria basados en las curvas I-V para los chips  $n^{o}9$  y  $n^{o}10$ .

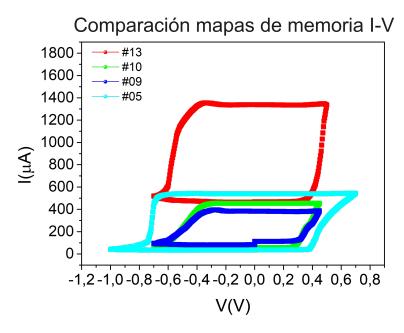

En la Figura 23 podemos ver la estabilidad de los estados de resistencia LRS y HRS de los dispositivos. Ambos se producen a una corriente de conducción estable, aunque el valor varía dependiendo de la muestra. En estas medidas se observa una gran variación

entre los diversos dispositivos en la corriente de funcionamiento, como podemos ver en la Figura 24. En esta figura se comparan cuatro de las muestras más estables, entre ellas las muestras  $n^{o}9$  y  $n^{o}10$  de la Figura 23, y se puede apreciar claramente cómo los parámetros para la muestra  $n^{o}13$  difieren significativamente del resto de muestras.

**Figura 24:** Comparación de mapas de memoria I-V de las muestras  $n^{\varrho}05$ ,  $n^{\varrho}09$ ,  $n^{\varrho}10$  y  $n^{\varrho}13$ .

Las muestras  $n^09$  y  $n^010$  presentan unos valores de funcionamiento muy similares, con  $I_{conduccionHRS} = 425\mu A$  y  $I_{conduccionLRS} = 75\mu A$ . En ambas muestras el SET comienza en  $V_{SET} = 0, 4V$  y el RESET en  $V_{RESET} = -0, 6V$ . Comparando estos valores con las muestras  $n^013$  y  $n^005$  se observa que la muestra  $n^013$  presenta los mismos valores de voltaje de funcionamiento aunque valores distintos de corriente de conducción. Para la muestra  $n^005$  observamos lo contrario, sus valores de corriente de conducción son más similares a los observados en las muestras  $n^010$  y  $n^013$ , pero su voltaje de funcionamiento presenta cierta variación frente a las muestras anteriores.

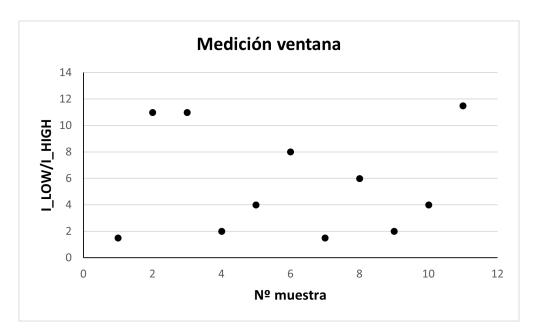

Otro parámetro interesante para el estudio es la ventana entre los estados LRS y HRS. Al medir la ventana podemos evaluar la relación entre los estados de alta y baja corriente del memristor, que se corresponden a los estados HRS y LRS respectivamente. Se trata de una relación crucial para estudiar la estabilidad de los dispositivos, distinguiendo entre sus estados lógicos 0 y 1. Realizando los cálculos necesarios podemos ver que la ventana entre ambos estados es bastante estable (ver Fig. 25)

**Figura 25:** Representación de la ventana entre los estados LRS y HRS de resistencia para las muestras más estables.

Según los valores obtenidos, podemos concluir que el valor de la ventana para las muestras más estables de todas las muestras estudiadas es algo bajo. Idealmente se busca un valor de ventana de varios órdenes de magnitud, pero en nuestras medidas sólo se observa un orden de magnitud de variación entre los estados 0 y 1 en el mejor de los casos.

Este valor bajo de la ventana representa una mala robustez contra posibles perturbaciones eléctricas o térmicas en el dispositivo. Al intentar implementar este tipo de memristores como memorias, podría dar lugar a información corrupta debido a posibles errores en la lectura, lo que limita su uso en aplicaciones prácticas en su estado actual.

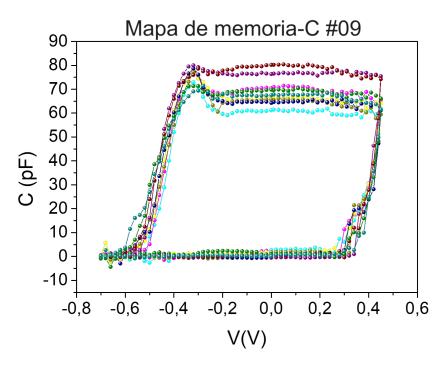

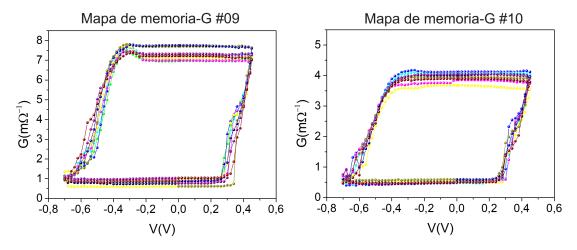

También se han realizado medidas de mapas de memoria de capacidad, C, y conductancia, G, como podemos ver en las Figuras 26 y 27. Para hallar los valores de capacidad y conductancia se ha utilizado el modelo de circuito equivalente para el memristor (ver Figura 20). Para realizar estas medidas se ha aplicado una señal alterna de voltaje 30mV y frecuencia 100kHz.

En la Figura 26 podemos observar cómo la capacidad del dispositivo varía en los estados LRS y HRS. Obtenemos que los estados son estables para un mismo dispositivo y soportan un elevado número de ciclos, pero la ventana entre estados sigue siendo inferior a los valores esperados y la variabilidad muestra a muestra persiste.

En la Figura 27 se puede observar cómo los resultados obtenidos para los estados de HRS y LRS varían bastante entre las dos muestras. Para el chip nº9 tenemos que los valores obtenidos son  $G_{LRS}=1m\Omega^{-1}$  y  $G_{HRS}=70m\Omega^{-1}$ , mientras que para el chip nº10 obtenemos  $G_{LRS}=0,5m\Omega^{-1}$  y  $G_{HRS}=4m\Omega^{-1}$ .

Se debe recalcar que las medidas de mapas de memoria de capacidad y conductancia son complicadas de realizar y el modelo utilizado es una aproximación al comportamiento real del memristor, lo que puede explicar la variabilidad de resultados entre las distintas muestras.

Figura 26: Ejemplo de mapa de memoria de capacidad para el chip  $n^{o}9$ . En estas medidas se ha aplicado una señal alterna de características V=30mV y f=100kHz. Para este dispositivo los valores de la capacidad para LRS y HRS son  $C_{LRS}=0pF$  y  $C_{HRS}=70pF$  respectivamente.

Figura 27: Ejemplo de mapas de memoria de conductancia I-V para los chips  $n^{\varrho}9$  y  $n^{\varrho}10$ . En estas medidas se ha aplicado una señal alterna de características V=30mV y f=100kHz. Para este dispositivo los valores de la conductancia para LRS y HRS son  $G_{LRS}=1m\Omega^{-1}$  y  $G_{HRS}=70m\Omega^{-1}$  para el chip  $n^{\varrho}9$  y  $G_{LRS}=0,5m\Omega^{-1}$  y  $G_{HRS}=4m\Omega^{-1}$  para el chip  $n^{\varrho}10$ .

### 4.3. Comportamiento transitorio

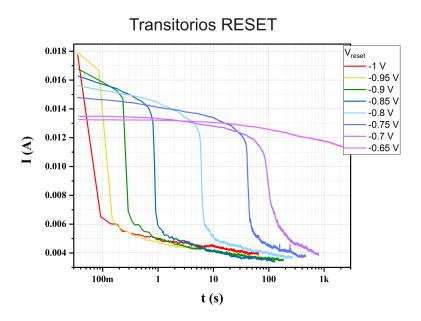

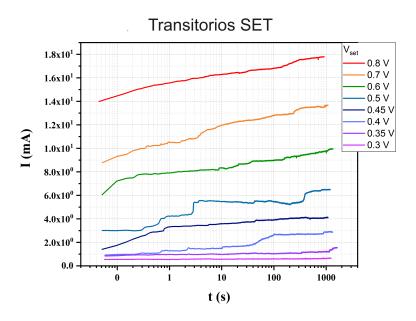

Para realizar las medidas del comportamiento transitorio de las muestras, se aplica durante un largo tiempo un voltaje determinado. En las Figuras 28 y 29 se hace un barrido de voltaje desde 0,3V hasta el valor máximo que permita la muestra en los procesos de RESET y SET respectivamente.

**Figura 28:** Ejemplo de medidas de comportamiento transitorio durante el proceso de RESET con el eje temporal en escala logarítmica. Voltajes aplicados desde 0,35V hasta 0,9V en incrementos de 0,5V durante t=1000s.

En la figura 28 se representan los transitorios de RESET a distintos voltajes aplicados. En este transitorio el dispositivo transiciona del estado LRS al HRS y se aprecia claramente cómo la curva se asemeja a una función sigmoidal. En dicha figura podemos observar que para la mayoría de voltajes los valores iniciales de corriente se mantienen constantes, este comportamiento se debe a que aún no se ha alcanzado el valor de umbral de voltaje. Se puede apreciar claramente cómo este tramo inicial constante no aparece al aplicar un valor de  $V_{RESET} = -1V$ , donde el voltaje cae verticalmente desde t=0, o al aplicar  $V_{RESET} = -0.65$ , donde el único tramo presente es este valor constante, debido a que el voltaje aplicado es demasiado bajo para activar el RESET. Después de este estado prácticamente constante, la corriente disminuye rápidamente, revelando la eficiencia en el cambio de estados del memristor.

Es importante recalcar no sólo el valor del voltaje umbral que debe alcanzarse para que se produzca el RESET, si no también el valor umbral correspondiente para el tiempo. Aunque en el comportamiento ideal del dispositivo este tiempo umbral es mínimo, en la realidad se necesita un determinado tiempo para disolver parcialmente el CF. Fijándonos en la curva donde se aplica un voltaje  $V_{RESET}=-0,85V$ , el tiempo en el que el memristor realiza el proceso de RESET es aproximadamente:  $t_{RESET}=1s$ . Si nos centramos en las curvas donde el voltaje aplicado es mayor, se puede apreciar cómo el tiempo necesario para que el RESET ocurra es menor, pasando a ser  $t_{RESET}=200ms$  aproximadamente para  $V_{RESET}=-0,95V$ . Esta disminución en el tiempo umbral de transición al RESET tiene sentido, pues al aplicar un mayor voltaje los iones de oxígeno presentes en el medio aislante se aceleran más rápidamente hacia las zonas de vacantes (es decir, el filamento

conductor), favoreciendo así la recombinación que lleva a la destrucción parcial del CF. Por último, se observa una etapa en la que la corriente continua disminuyendo. El hecho de que la corriente no alcance un valor constante puede deberse al tiempo que le toma a los materiales que forman el memristor alcanzar un nuevo equilibrio tras el cambio de estado.

A continuación, en la Figura 29 se representan los transitorios de SET a distintos voltajes aplicados. En este transitorio el dispositivo transiciona del estado HRS al LRS. Como el eje temporal se encuentra en escala logarítmica, vemos esta variación exponencial de la pendiente relativa a la corriente como una función lineal para aquellos transitorios que superan el voltaje umbral necesario para provocar el SET. En todos los voltajes se puede apreciar un cambio en la pendiente de las funciones representadas, excepto en la curva con voltaje  $V_{SET}=0,5V$  aplicado, donde se observan distintos tramos en forma escalonada. Es posible que estos escalones se deban a la formación del filamento conductor, que atraviesa diversas etapas, ya que durante las medidas realizadas en el laboratorio esta curva fue la primera en medirse.

**Figura 29:** Ejemplo de medidas de comportamiento transitorio durante el proceso de SET con el eje temporal en escala logarítmica. Voltajes aplicados desde 0.3V hasta 0.5V en incrementos de 0.5V durante t=1000s.

De forma similar al proceso de RESET, en el proceso de SET es de esperar que la transición entre estados de lugar a corrientes más elevadas conforme aumenta el voltaje aplicado. Esto se debe a que, al incrementar el voltaje, el tiempo requerido para que se produzca el SET es menor. Aumentar la tensión implica favorecer el movimiento de los iones de oxígeno fuera de la zona filamentaria, lo que provoca que las vacantes de oxígeno aparezcan más rápidamente y que contribuyan a la formación del filamento conductor de forma más eficiente, mejorando la robustez del filamento. Observando la Figura 29, se aprecian variaciones en la pendiente representada especialmente para el caso donde  $V_{SET}=0,5V$ , el primer caso medido en el laboratorio.

Podemos concluir que, en una primera instancia, el filamento conductor se forma conforme aumenta el tiempo durante el cual medimos el transitorio; mientras que para las siguientes medidas realizadas a distintos voltajes no se aprecia una variación de la

pendiente tan clara. A nivel físico es posible que esto se deba a una saturación de las vacantes de oxígeno presentes en el medio aislante del memristor. Es decir, el material ha alcanzado un límite en cuanto a la cantidad de vacancias de oxígeno que puede acumular en el área activa de formación del CF, de modo que la corriente no aumenta significativamente. Esta falta de variación en el transitorio correspondiente al proceso de SET indica que el filamento ya tiene una estructura robusta y no se está formando activamente en respuesta a cada incremento de voltaje, al menos dentro del rango aplicado.

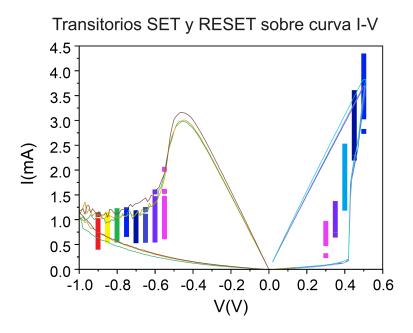

**Figura 30:** Medidas de SET y RESET sobre ciclos I-V. Los colores de los transitorios (líneas verticales) corresponden a los transitorios medidos en las Figuras 28 y 29.

Finalmente, en la Figura 30 se puede observar que las líneas correspondientes a los transitorios representadas sobre sus correspondientes curvas I-V son completamente verticales. No se aprecia ninguna pendiente, lo que indicaría un mal funcionamiento del dispositivo, y esto evidencia la coherencia entre ambas medidas. En algunos voltajes se puede apreciar cómo el valor de la corriente supera los valores de las curvas I-V. Esto se debe a la lentitud con la que se realizan la medida de transitorios, lo cual puede permitir que el dispositivo alcance valores de corriente superiores a los que alcanzaría en circunstancias normales de medición de curvas I-V.

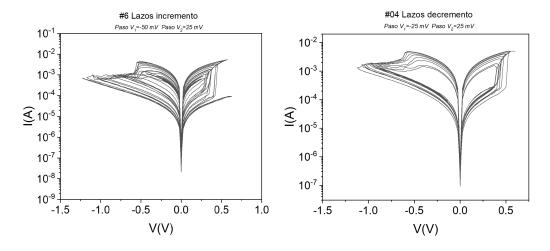

### 4.4. Lazos de incremento y decremento

La última de las medidas que se presentan en este estudio son los lazos de incremento y decremento, los cuales se miden de la siguiente manera:

- Lazos de incremento: estos lazos se obtienen aumentando gradualmente el voltaje aplicado a un memristor en sus medidas de curvas I-V desde un estado de alta resistencia HRS.

- Lazos de decremento: estos lazos se obtienen disminuyendo el voltaje aplicado desde un estado de baja resistencia LRS.

Estos lazos, tanto incrementales como decrementales, revelan una de las características más reseñables de los memristores: su capacidad de operar a distintos valores de resistencia (estados multinivel) dependiendo del voltaje aplicado para cada ciclo I-V. Esta propiedad es similar a los pesos aplicados en las sinapsis neuronales, que son capaces de adaptar su respuesta dependiendo del estímulo al que se vean sometidas. Además, los memristores son capaces de trabajar a distintos voltajes manteniendo su histéresis, es decir, manteniendo su información almacenada [28]

El área del lazo es menor a menor voltaje aplicado y aunque a voltajes extremadamente pequeños la información podría llegar a perderse, este comportamiento no se observa en la Figura 31, en los lazos decremento, donde existe este riesgo de pérdida de información. Mediante ambos experimentos hemos conseguido mostrar las capacidades multinivel de esta muestra, dando cuenta de la multitud de estados resistivos que puede alcanzar.

Debido a que estas medidas de lazos incremento y decremento se tratan de curvas I-V, es interesante recalcar que dichas curvas continúan siendo consistentes con la teoría expuesta anteriormente. Cuando se realiza un SET o un RESET a un menor voltaje que el habitual, la curva parte del estado que se alcanzaría con la anterior transición. Esto revela que el filamento conductor se ha formado previamente en el medio aislante de la estructura MIM y que, por muy débil que sea la señal eléctrica aplicada, el dispositivo es capaz de realizar el ciclo I-V con normalidad, evidenciando su "memoria. ante un estímulo previo.

Figura 31: Lazos incremento y decremento de las muestras  $n^06$  y  $n^04$  respectivamente. En los lazos incremento (derecha) el paso de voltaje en los procesos de SET y RESET no es simétrico, mientras que sí lo es en los lazos decremento el paso de voltaje sí es simétrico. En los lazos incremento se comienza con un voltaje de  $V_{incremento,i} = 0,025V$  y termina en  $V_{incremento,f} = 0,5V$ . En los lazos decremento se comienza con un voltaje de  $V_{decremento,i} = 0,5V$  y termina en  $V_{decremento,f} = 0,3V$ .

### 5. Conclusiones

En este trabajo se han realizado una serie de medidas con el fin de caracterizar la respuesta de muestras  $TiN-Ti-HfO_2-TiN$  (8nm) estudiadas dentro del marco de la conmutación resistiva. Se han medido las curvas I-V de los memristores, sus mapas de memoria I-V, de capacidad y de conductancia, los transitorios de SET y RESET y los lazos de incremento y decremento asociados a estos dispositivos.

En todas estas medidas se ha profundizado en la teoría presentada, y las conclusiones halladas respaldan los modelos teóricos estudiados. Podemos verificar que todos los fenómenos teóricos esperados en los memristores están presentes en estos dispositivos y se observan con claridad.

Sin embargo, aunque para cada chip estudiado los resultados concuerdan con lo esperado, se ha observado una alta variabilidad muestra a muestra, dificultando la estandarización de los valores de funcionamiento de estas memorias. En cuanto a las medidas de mapas de memoria, se aprecia una alta estabilidad de cada estado de resistencia (HRS y LRS), pero los valores de ventana obtenidos no son los ideales, lo que dificulta su posible aplicación práctica ante un posible error en el almacenamiento de información.

Por otro lado, en las medidas de los transitorios asociados a los procesos de SET y RESET se ha comprobado que para ambos procesos el tiempo de transición entre estados de resistencia es menor al aumentar el voltaje aplicado. Además, en el proceso de RESET se aprecia un tiempo umbral necesario para que el RESET ocurra. Dicho tiempo mínimo disminuye al aumentar el voltaje aplicado. Este comportamiento no se ha observado en el transitorio de SET, aunque también se esperaba obtener el mismo resultado.

Podemos concluir que existe una saturación de vacantes de oxígeno en la zona efectiva donde se crea el filamento conductor, es decir que su estructura es robusta y no se está formando activamente durante el SET en respuesta a cada incremento de voltaje. Por otro lado, para el RESET, el filamento no tiene un proceso fijo que siga en todas las iteraciones y por eso observamos de forma más clara la variación de la corriente que atraviesa el dispositivo respecto al tiempo.

Por último, se han presentado las medidas correspondientes a los lazos de incremento y decremento de las muestras estudiadas, donde se ha observado que los memristores son capaces de presentar diversos estados de resistencia dependiendo del estímulo eléctrico previo aplicado. La capacidad multinivel de los memristores tiene un alto potencial para emular el comportamiento de las sinapsis neuronales y en este estudio se ha observado este comportamiento claramente.

En conclusión, aunque los resultados obtenidos entran dentro de lo esperado y verifican todos los fenómenos desarrollados teóricamente, el mayor punto de mejora es la variabilidad muestra a muestra, que sigue siendo uno de los mayores inconvenientes de las memorias RRAM. En estos dispositivos de TiN-Ti-HfO<sub>2</sub>-TiN, además se ha observado una alta degradación a lo largo de los ciclos de conmutación: algunos dispositivos soportaban 100 ciclos cómodamente pero otros se degradaban antes de alcanzar los 50.

Una menor variabilidad muestra a muestra y ciclo a ciclo permitiría que las memorias RRAM se estandarizaran en el mercado y facilitaría su implementación en múltiples ámbitos de la industria. Para llegar a este punto se debe optimizar el proceso de fa-

bricación de los memristores. Esta mejora podría desarrollarse a partir de un análisis computacional previo a la fabricación de las estructuras MIM, basado en modelos sobre caracterizaciones eléctricas experimentales como la realizada en este trabajo.

En un futuro, este desarrollo basado en la combinación de estudios experimentales y computacionales, podría permitir que se fabricaran memristores con las características deseadas para cada aplicación en concreto, reforzando características únicas de los memristores como su faceta como memorias no volátiles, su resistencia variable dependiendo de la historia del dispositivo, alta densidad de almacenamiento y bajo consumo de energía o su velocidad de conmutación, según se desee.

Este Trabajo de Fin de Grado ha permitido conectar los conocimientos adquiridos a lo largo del plan de estudios del Grado en Física con su aplicación práctica en un entorno de laboratorio trabajando junto con el Grupo de Caracterización de Materiales y Dispositivos Electrónicos (GCME). En particular se han ampliado los conocimientos relacionados con electrónica, dispositivos optoelectrónicos, teoría de circuitos, materiales semiconductores y técnicas de medición en laboratorio.

En este trabajo se ha profundizado en el comportamiento de dispositivos electrónicos (memristores) bajo diferentes condiciones de operación, analizando la relación entre el comportamiento eléctrico observado con la teoría del comportamiento a nivel molecular de los materiales que forman el memristor. Se han desarrollado diversas habilidades como: análisis de datos mediante herramientas de software y técnicas de laboratorio que me han permitido mejorar mi precisión en tanto en la manipulación de equipos como en la toma de medidas fiables. Además, en la elaboración de este Trabajo de Fin de Grado he podido desarrollar habilidades de investigación y pensamiento crítico.

Quiero agradecer al Grupo de Caracterización de Materiales y Dispositivos Electrónicos (GCME), en particular a Guillermo, Óscar, Salva y Helena su apoyo durante las prácticas y la elaboración de este Trabajo de Fin de Grado. Agradezco especialmente su paciencia y el tiempo que han dedicado a orientarme para desarrollar este trabajo. Este TFG no habría sido posible sin su apoyo y compromiso.

REFERENCIAS REFERENCIAS

### Referencias

[1] Gordon E. Moore. Cramming more components onto integrated circuits, reprinted from electronics, volume 38, number 8, april 19, 1965, pp.114 ff. *IEEE Solid-State Circuits Society Newsletter*, 11(3):33–35, (2006).

- [2] Gordon E. Moore. Progress in digital integrated electronics [technical literal ture, copyright 1975 leee. reprinted, with permission. technical digest. international electron devices meeting, leee, 1975, pp. 11-13.]. *IEEE Solid-State Circuits Society Newsletter*, 11(3):36–37, (2006).

- [3] Robert Keyes. Physical limits of silicon transistors and circuits. Reports on Progress in Physics, 68:2701, 09 (2005).

- [4] David A. Patterson and John L. Hennessy. *Computer architecture: a quantitative approach*. Morgan Kaufmann Publishers Inc., San Francisco, CA, USA, (1990).

- [5] Wm. A. Wulf and Sally A. McKee. Hitting the memory wall: implications of the obvious. SIGARCH Comput. Archit. News, 23(1):20–24, mar (1995).

- [6] Max Roser, Hannah Ritchie, and Edouard Mathieu. What is moore's law? What is Moore's Law?, (2023). Última visita el 19/03/2024.

- [7] Humaira and Mamoona Asghar. Limitation of silicon based computation and future prospects. pages 559 561, 03 (2010).

- [8] L. Chua. Memristor-the missing circuit element. *IEEE Transactions on Circuit Theory*, 18(5):507–519, (1971).

- [9] Dmitri B. Strukov, Greg Snider, Duncan R. Stewart, and R. Stanley Williams. The missing memristor found. *Nature*, 453:80–83, (2008).

- [10] Cesar de Souza Dias and Paulo Butzen. A spice model for design of threshold current controlled memristive devices based applications. Analog Integrated Circuits and Signal Processing, 106, 01 (2021).

- [11] Abu Sebastian, Manuel Le Gallo, Riduan Khaddam-Aljameh, and Evangelos Eleftheriou. Memory devices and applications for in-memory computing. *Nature nanotechnology*, 15(7):529—544, July (2020).

- [12] Emanuel Carlos, Rita Branquinho, Rodrigo Martins, Asal Kiazadeh, and Elvira Fortunato. Recent progress in solution-based metal oxide resistive switching devices. *Advanced Materials*, 33(7):2004328, (2021).

- [13] Leon Chua. Resistance switching memories are memristors. Applied Physics A, 102:765–783, 03 (2011).

- [14] Ella Gale. Tio2-based memristors and reram: Materials, mechanisms and models (a review). Semiconductor Science and Technology, 29(10), oct (2014).

- [15] Yamin Li, Kang Su, Haoran Chen, Xiaofeng Zou, Changhong Wang, Hongtao Man, Kai Liu, Xin Xi, and Tuo Li. Research progress of neural synapses based on memristors. *Electronics*, 12:3298, 07 (2023).

REFERENCIAS REFERENCIAS

[16] Jae Lee, Shinbuhm Lee, and Tae Noh. Resistive switching phenomena: A review of statistical physics approaches. *Applied Physics Reviews*, 2, 09 (2015).

- [17] Ee Wah Lim and Razali Ismail. Conduction mechanism of valence change resistive switching memory: A survey. *Electronics*, 4:586–613, 09 (2015).

- [18] Jaewook Lee, Yang Kun, Ju Kwon, Ji Eun Kim, Dong Han, Dong Lee, Jung Yoon, and Min Hyuk Park. Role of oxygen vacancies in ferroelectric or resistive switching hafnium oxide. *Nano convergence*, 10:55, 12 (2023).